用于HF接收机的高纯度频率源的研制

2019-04-17程明周叶华姜建飞

程明,周叶华,姜建飞,2

(1.中国电子科技集团公司第三十六研究所,嘉兴 314033;2.通信信息控制和安全技术国防重点实验室,嘉兴 314033)

0 引言

短波通信,这一传统的通信方式,由于其通信距离远、成本低廉、抗打击毁坏能力强等优点,在军事远程通信、无线电导航、授时系统、广播等领域得到广泛应用[1-3]。尽管自20世纪70年代以来,随着卫星通信的异军突起,卫星通信在相当大的程度上取代了短波通信,但随着人们对卫星通信的易损耗性、耗资巨大等局限性的认知,短波通信又重新得到重视。从军事角度而言,没有一种单一的远程通信可以满足所有需求,因而世界上主要发达国家的C4ISR系统都部署了短波通信系统,而且发挥着越来越重要的作用[4-7]。其中,0.3~300 kHz用于超远程海军通信,0.3~30 kHz多用于潜艇通信和无线电导航,500 kHz~15 MHz用于无线电广播,2~30 MHz(HF(high frequency)频段为主)用于三军超视距通信、陆军战术移动通信、我国BPM授时系统等[8-12]。短波频段电磁频谱异常拥挤和复杂,因此要求短波接收机必须具有大动态的特点,而研制大动态接收机必然需要高纯度频率源作为本振,因为频率源的相位噪声和杂散抑制影响接收机的瞬时动态范围和灵敏度,同时换频速度也影响接收机的侦察搜索速度及截获能力,因此研制高纯度的频率源是研制高性能短波接收机的关键技术。

1 方案原理

现因某机载工程需要,需要研发一款高性能大动态短波接收机,工作频段为HF频段:2~30 MHz。HF接收机的一本振频率为:76.8~104.8 MHz,要求频率源具有小步进、捷变频、高纯度等特点。下面对其详细指标和设计方案进行论述。

1.1 主要技术指标要求

用于HF接收机的高纯度频率源的主要技术指标要求如下:

①输出频率范围:76.8~104.8 MHz;

②频率步进:1 Hz;

③杂散抑制:≥85 dB;

④相位噪声:≤-140 dBc/Hz@10 kHz;

⑤换频速度:≤10 μs;

⑥标频输入:100 MHz,0~5 dBm,相噪优于-155 dBc/Hz@10 kHz。

⑦频率准确度与稳定度:同外部标频。

1.2 方案选择

目前,频率合成的方法一般包括如下几种:直接频率合成技术、锁相频率合成技术(PLL)和直接数字频率合成技术(DDS)。

①直接式频率合成技术运用倍频器、分频器、混频器、谐波发生器等部件,对频标源进行加减乘除运算,采用滤波器取出所需的频率;具有换频速度快、相噪低等优点,但体积较大,杂散抑制也很难做好。

②锁相式频率合成技术利用鉴相器、分频器、环路滤波器、压控振荡器等器件组成,锁相环锁定后输出特定频率,具有电路简单、成本低、体积小等优点。

③直接数字频率合成技术采用数字电路技术得到离散的数字序列,然后经过D/A变换得到模拟信号,具有换频速度快、频率分辨率高、体积功耗小等优点[13]。

经过慎重考虑和评审,课题组认为该高纯度频率源采用锁相式频率合成技术与直接数字频率合成技术相结合的方案比较合适,兼具低相噪、高分辨率、高杂散抑制、捷变频等优点。

1.3 详细设计方案

具体方案如图1所示,该方案采用锁相式频率合成技术与直接数字频率合成技术相结合的方式,主要由锁相源和DDS两部分组成,锁相源用做DDS的时钟,锁相源频率为900/1 000 MHz,时钟选择可变的原因是为了规避DDS某些杂散。锁相源输出频率fCLK(即DDS时钟)可用下面公式表示:

fCLK=N·fPD,

(1)

式(1)中,N为环路分频比,对于该方案N为9或10;fPD为环路鉴相频率,对于该方案fPD为100 MHz。

DDS输出频率fDDS可用下面公式表示:

(2)

式(2)中,FTW为DDS的频率控制字,假定DDS有32 bit控制字。

该方案主要由以下单元组成:鉴相器、环路滤波器、压控振荡器(VCO)、放大器、功率分配器、DDS、低通滤波器等。工作原理如下,输入标频为100 MHz,来自超低相噪恒温晶振,标频分频比R=1;鉴相频率为100 MHz;环路分频比N=9或10。高纯度频率的DDS频标为900/1 000 MHz,需要100 MHz鉴相才能做到最低相噪,分频比为9/10。AD公司的(锁相环路)PLL,集成VCO芯片,具有体积小的优点,在低鉴相频率时(20 MHz以下)鉴相器基底噪声为-230 dBc/Hz,具有较好的基底噪声,但在100 MHz鉴相时鉴相器基底噪声只有-220 dBc/Hz,有较大恶化,并且该类集成芯片换频速度一般超过100 μs,做不到捷变频。DDS集成的时钟倍频功能,使用的集成VCO噪声较差,鉴相器在100 MHz是基底噪声也不是最低,因此不适合本方案。PEREGRINE公司PE33241芯片,在100 MHz鉴相时基底噪声仍然可以做到-230 dBc/Hz,为目前行业最低水平;并且该芯片采用并行控制,在换频发送数据时可以做到最快速度;采用鉴相芯片PE33241自己搭建锁相环,可以选用分离的性能较好的集成VCO,从而使锁相环输出900/1 000 MHz具有更好的相位噪声[14-15]。经环路锁定后,VCO输出频率为900/1 000 MHz,用作DDS的时钟信号,通过控制DDS,输出76.8~104.8 MHz信号。DDS输出具有一定的时钟杂散,因此需要加低通滤波器加以滤除,该低通滤波器的截止频率可以设计为120 MHz。

图1 频率源方案

1.4 与上一代方案比较

上一代HF接收机用频率源的主要技术指标如下:①接收机工作频段:HF频段;②频率步进:10 Hz;③相位噪声:≤-133 dBc/Hz@10 kHz;④换频速度:≤50 μs;⑤杂波抑制:≥85 dB。

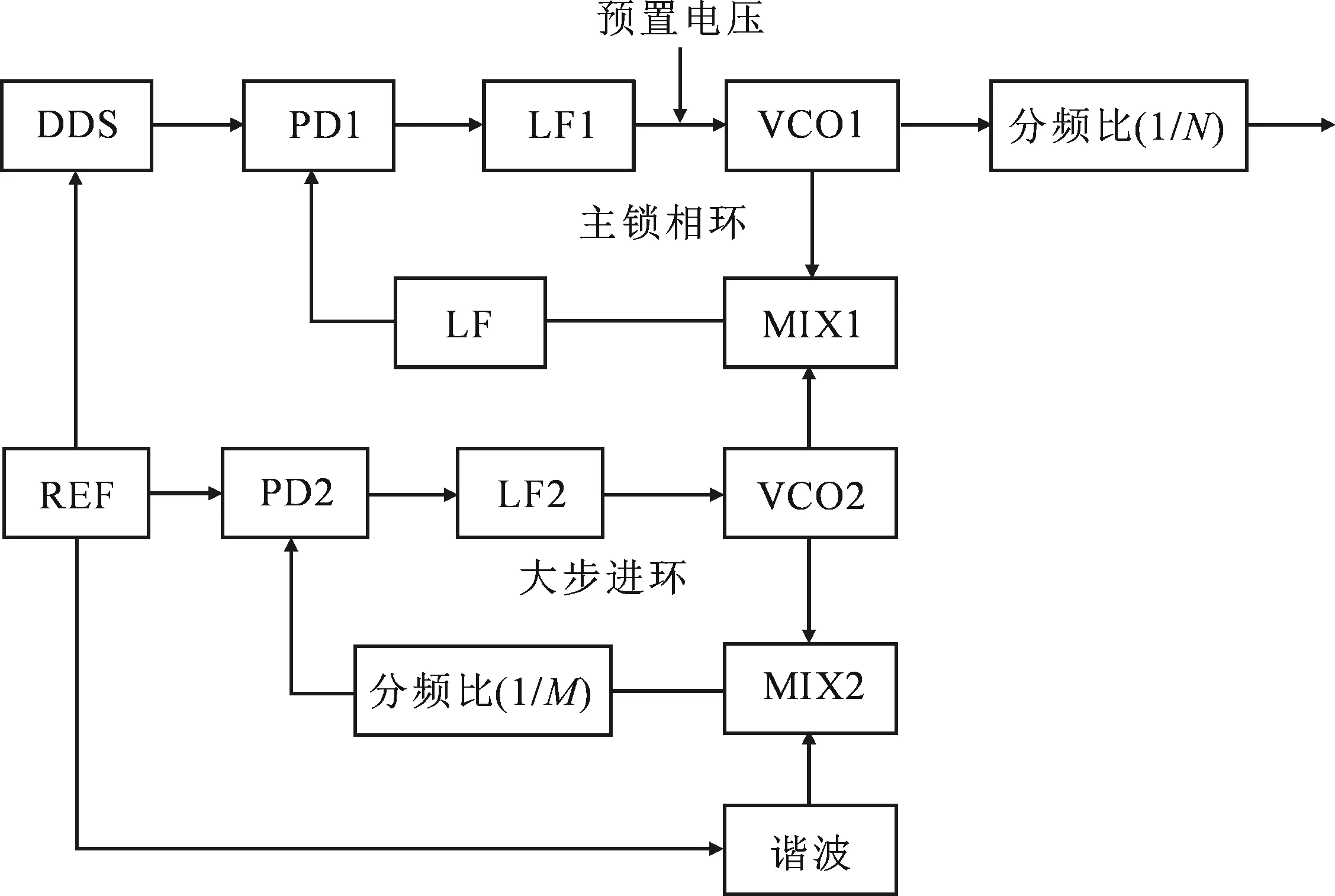

因为受制于当时的元器件水平等原因,上一代HF接收机用频率源的方案比较复杂,基本原理如图2所示,详细方案可见参考文献6[16]。该方案主要由以下几部分组成:①标频分配电路;②大步进环路;③梳状谱发生器电路;④DDS小步进电路;⑤主锁相环;⑥预置电压电路。频标为100 MHz恒温晶振信号,然后3分路用作各自标频。通过梳状谱和大步进混频环实现大步进功能,通过DDS实现小步进,主锁相环的VCO1锁定后输出相对比较高的频率,然后再通过分频器N除下来,得到比较高的杂散抑制和低相噪。换频速度主要通过预置频率电压来实现,但也很难做到捷变频。

与上一代方案比较,新方案具有如下优点:①方案大大简化,只需一个环路和DDS即可实现;②因为不再需要多环电路,因此可以实现捷变频,这对接收机而言是个重要进步;③可以实现更低的相位噪声。

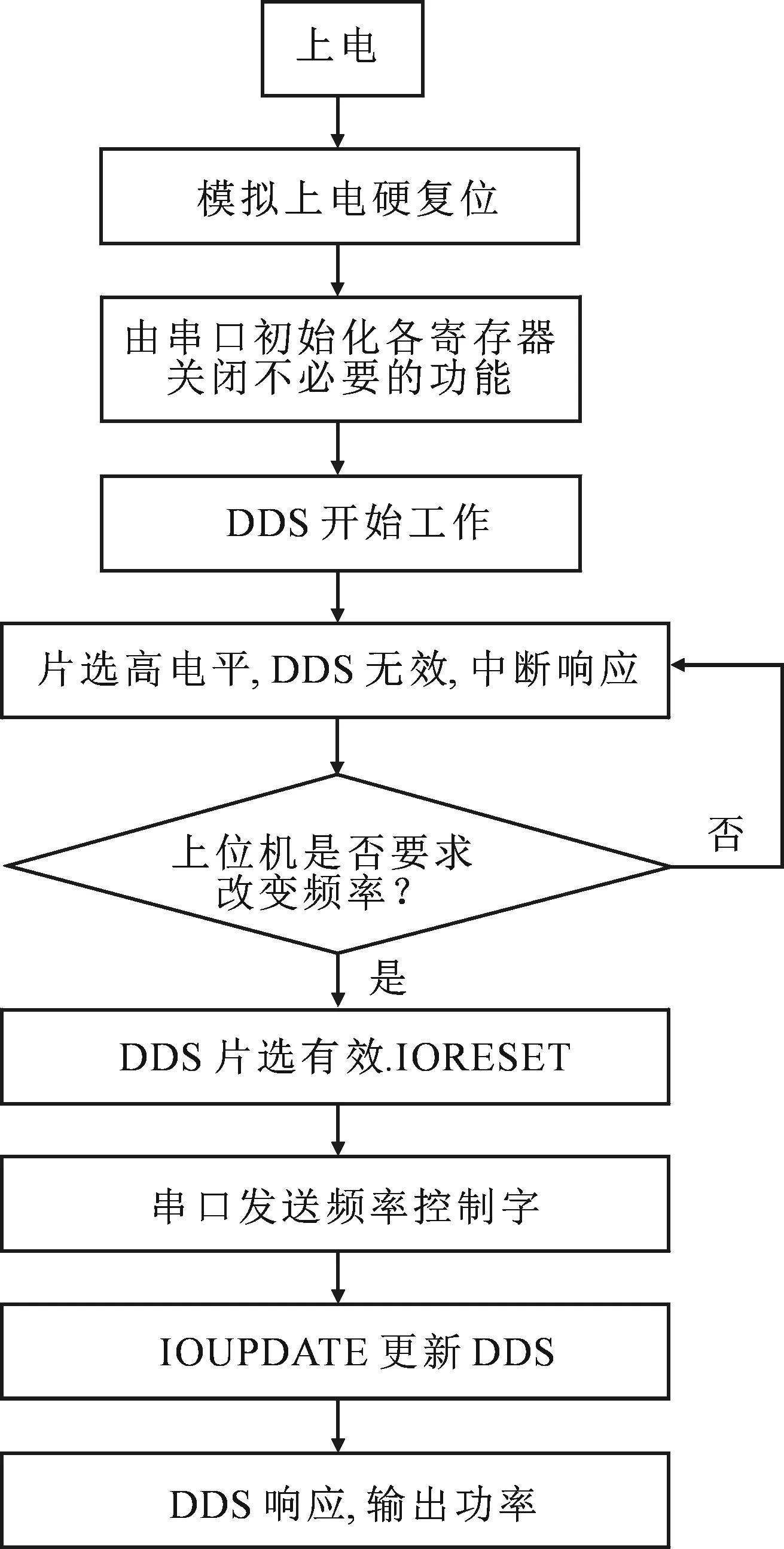

1.5 DDS工作流程

DDS是该频率源的关键电路,应对DDS工作流程特别重视,DDS工作流程设计的优劣将决定该频率源能否可靠的工作,本方案的DDS工作流程如图3所示[17-18]。

注:DDS为直接数字频率合成器;PD为鉴相器;LF为低通滤波器;VCO为压控晶振器;MIX为混频器;REF为频标

图3 DDS工作流程示意图

2 性能分析与仿真

该方案的性能分析与仿真,是基于已知芯片性能的基础上展开,因此有必要说明一下主要芯片的性能。

①PLL芯片(PE33241):整数分频,5/6预分频模式最大工作频率为4 GHz,10/11预分频模式最大工作频率为5 GHz;鉴相器基底相噪为-230 dBc/Hz(5/6预分频模式);最大鉴相频率为100 MHz,标频输入最大为100 MHz;具有并行和串行控制模式[19]。

②DDS芯片(AD9910):最大时钟1 GHz,具有时钟倍频功能,模拟输出最大400 MHz;14位DAC,32 bit控制字,频率分辨率0.23 Hz;最大串行控制速率70 Mbit/s;窄带杂散抑制大于80 dB。

2.1 相噪与频率分辨力分析

该方案锁相芯片采用PE33241,在鉴相频率为100 MHz时,其归一化基底噪声为:

Nfloor=-230+10lg100 000 000=-150 dBc/Hz@10 kHz,

(3)

那么输出1 GHz时钟时,环路分频比N=10,1 GHz时钟的相噪估算为:

NCLK=Nfloor+20lgN。

(4)

那么,NCLK=-150+20lg10=-130 dBc/Hz@10 kHz。

设置以下参数,对1 GHz时钟信号的相噪仿真和换频速度如图4和图5所示。标频输入为100 MHz,标频相位噪声为≤-155 dBc/Hz@10 kHz。标频分频比R=1;鉴相频率为100 MHz;环路分频比N=9,N=10;环路带宽取约1 MHz;锁相芯片采用PE33241,采用该公司已有建模库;环路滤波器采用有源比例4阶滤波器;VCO频率为900~1 000 MHz;调谐灵敏度38~45 MHz/V。

图4 1 GHz相位噪声仿真

图5 换频速度仿真

由以上计算和仿真可知,1 GHz时钟信号的理论相噪约为-130 dBc/Hz@10 kHz,为DDS输出高纯度超低相噪信号创造了必要条件。

DDS输出频率的相噪可用公式(5)表示:

(5)

DDS输出76.8 MHz时,理论相噪估算如式(6)所示:

(6)

DDS输出90 MHz时,理论相噪估算如式(7)所示:

(7)

DDS输出104.8 MHz时,理论相噪估算如式(8)所示:

(8)

DDS输出的频率分辨率计算如式(9)所示:

(9)

从以上分析和计算可知,DDS输出信号理论相噪优于-149 dBc/Hz@10 kHz,频率分辨率为0.23 Hz,满足设计要求。

2.2 换频速度与杂散抑制分析

对于本方案,频率源的换频速度(T)主要由两部分组成:时钟切换速度(TCLK)和DDS换频速度(TDDS)。

T=TCLK+TDDS

(10)

由时钟切换速度仿真图5可知,时钟切换速度为3 μs。

由于DDS响应极快,因此DDS的换频速度主要由送数时间决定。由于单机设计需要,DDS只能采用串行总线控制,串行总线速率为25 MHz,DDS在进行初始化后,只需发送寄存器地址和32 bit的频率控制字即可,因此送数时间不超过2 μs。

T=TCLK+TDDS=3+2=5 μs。

(11)

由以上分析可知,频率源的理论换频速度不超过10 μs,满足捷变频的要求[20]。

DDS输出信号为76.8~104.8 MHz,是由DDS的时钟(1 GHz)分频所得,因此DDS输出的杂散和相噪相对1 GHz都有一定优化,DDS输出的杂散抑制主要取决于DDS本身的杂散抑制能力,基本不受时钟制约,因此选用AD公司14位的DDS芯片,如果布线合理的话,DDS输出近端杂散抑制超过80 dB并不难[6]。

由于DDS输出信号的远端具有较大的杂散信号,因此需要使用低通滤波器加以滤除杂散信号,该低通滤波器的设计比较简单,可以采用一般的七阶chebyshev滤波器即可,仿真如图6所示。

该低通滤波器的设计参数为:L1=94 nH,L2=102 nH,L3=94 nH;C1=40 PF,C2=65 PF,C3=65 PF,C4=40 PF。

由仿真可知,该低通滤波器在200 MHz以上具有超过50 dB的抑制,为了防止该滤波器在远端有翘起情况,还可以在该低通滤波器后加一个简单的集成LTCC滤波器,加强对1 GHz以外杂散的抑制[19]。

图6 低通滤波器仿真图

3 模块系统集成

模块集成在一个100 mm×50 mm×15 mm的腔体中。为了节省体积,采用4层板布线,板材为罗杰斯5880,包括VCO、分路、放大、环路滤波、DDS、低通滤波器等电路。尤其需要关注DDS电路的设计,应注意以下几方面:①数模电源分离设计;②上电硬复位;③寄存器初始化,后续控制只发送频率控制字,以节省控制时间;④控制速率不可过高,波形容易畸变;⑤电源杂散应该处理干净,否则影响杂散抑制能力。

频率源电路如图7所示,实物见图8所示。

图7 频率源电路图

图8 频率源实物图

4 模块测试与分析讨论

模块加工完成后,课题组对模块的性能进行了测试。测试性能指标见下表1所示。测试条件为:

①常温条件下测试;

②电源输入为+5 V/12 V;

④标频输入为100 MHz,幅度为0 dBm;标频相噪:-155 dBc/Hz@10 kHz,稳定度为≤3×10-7/d;

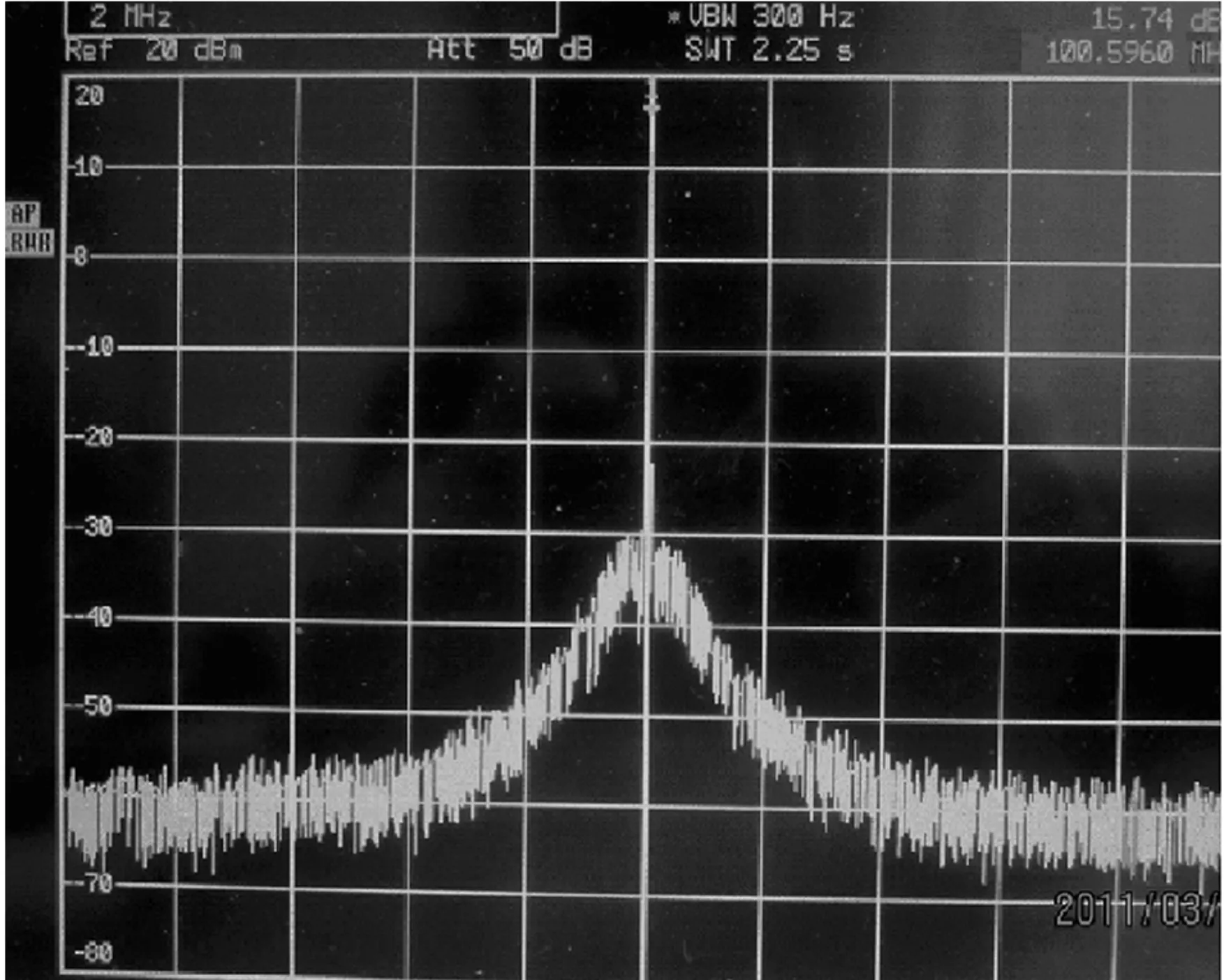

⑤采用频谱仪测试幅度与杂散抑制,示于图9;

⑥采用信号源分析仪测试相位噪声,示于图10。

图9 100.596 MHz杂散抑制测试图

图10 78.666 74 MHz相噪测试图

表1 频率源模块指标测试表

测试结果为,输出频率范围为76.8~104.8 MHz,输出幅度为13~16 dBm,杂散抑制为86~99 dB,相位噪声为-145~-149 dBc/Hz@10 kHz,频率分辨率小于1 Hz,换频速度小于10 μs,均满足设计要求。在完成测试后,课题组还对该模块进行了环境试验,试验结果表明该模块具有较好的环境适应性,为实际工程应用奠定了较好的基础。

在该模块研制完成后,课题组认为有几个方面值得总结和探讨:

①相噪方面。实测相噪比仿真稍差,原因可能是PE33241芯片的在鉴相频率为100 MHz时,底噪比理论值有较大的恶化,而芯片datasheet上又没有明确说明,这种情况在设计时应引起重视。

②杂散方面。为了降低杂散对灵敏度的影响,要求DDS输出在接收机一中频的频率(74.8 MHz)杂散抑制大于110 dB以上,这对于DDS而言是非常难的。如果批量生产时,该频率点杂散抑制超标,我们可以改变时钟的方式规避,此时要注意的是时钟切换速度必须要快。

③上电初始化。当该模块用在不同的单机和系统上时,课题组发现有上电初始化失败的情况,经过测试分析,发现原因为不同的系统和单机电源上电情况不同,在电源还没完全稳定的情况,就贸然给DDS进行了初始化,导致初始化失败。解决办法就是在单机上电后增加1~2 s延时,再进行DDS初始化,后面问题不再复现。

④数据计算方面。应选用高位数DSP进行计算,保证频率控制字计算精度,才能保证频率分辨率。另外,应优化浮点数计算算法,提高计算速度,否则会影响控制速度。

⑤通用性方面。该频率源时钟频率较高,因此DDS可以输出200 MHz以内的高质量信号,输出范围可以有比较大的拓展空间,可以满足不同体制HF接收机的需求,具有较高的通用性。

⑥相噪优化方面。如果要想DDS输出更好相噪的信号,可以对DDS的时钟信号进行改进,时钟考虑采用100 MHz直接倍频的方式得到,那么1 GHz时钟相噪可以有3~4 dB的提升,但因为受制于DDS的基底噪声(-151 dBc/Hz@10 kHz)限制,也很难具有大的提升空间。同时,灵活性和通用性会有一定的损失[20-21]。

⑦频率分辨率优化。该方案采用32 bit的AD9910,所以频率分辨率为0.23 Hz。因为目前单机的标频为恒温晶振,稳定度为≤3×10-7/d,所以频率分辨率可以满足目前单机的使用需求。但随着系统逐渐采用高稳定原子钟作为时标,0.23 Hz的频率分辨率将不再满足要求。我们后续打算对该DDS电路进行改进,DDS拟采用AD9912芯片,该DDS芯片频率控制字达到48位,理论分辨率可以做到3.5 μHz。

⑧换频速度优化。在发送顺序方面还可以做更进一步优化,可以考虑先发送锁相环的控制字,让其进入锁定状态,其锁定过程大约需要3 μs,在锁定过程中,可以再发送DDS控制字,这样可以节省DDS的发送时间2 μs,因此总换频速度可以控制在3 μs左右。

⑨国产化率方面不足。该设计的核心芯片为PE33241和AD9910,都为进口器件,因此在国产化率方面存在不足。随着国家在芯片方面进行的战略性投资, 13所及一些民品公司已经有一些射频与DDS芯片产品问世,相信在不远的将来,我们国家也能生产此类高性能的芯片。

5 结语

本文介绍了一种用于HF接收机的高纯度频率源的研制,给出了设计原理和仿真,并进行了模块系统集成和电路加工,课题组对模块进行了实际测试。测试结果表明,该频率源模块的输出频率、相位噪声、杂散抑制、频率分辨率、换频速度等指标均满足设计要求;主要指标较上一代短波接收机有了大幅提升,具有如下几方面的优点:

①更低相噪。相噪可以做到优于-145 dBc/Hz@10 kHz,相噪优化了10 dB;

②更快速度。换频速度小于10 μs,换频速度提升了4倍;

③更具通用性、灵活性,输出频率范围可进行大范围拓展,而性能不会有大的下降;

④模块化,方便批量生产和调试,方便移用和维修;

⑤体积和功耗更小,只有原来的约1/5;

⑥成本也有比较大幅度的下降。

当然该频率源也存在国产率不高方面的缺点。由于本文包含课题组的一些实际工作经验和想法,鉴于课题组成员的水平和认知局限,本文难免存在不当之处,敬请各位同行、专家不吝赐教并给予指正。