共晶焊倒装高压LED的制备及性能分析

2019-04-10刘志强王江华伊晓燕闫建昌王军喜李晋闽

尹 越, 田 婷, 刘志强 , 王江华,伊晓燕 ,梁 萌,闫建昌, 王军喜, 李晋闽

(1.中国科学院半导体研究所照明研发中心,北京 100083; 2.中国科学院大学,北京 100049;3.北京第三代半导体材料与应用工程技术研究中心,北京 100083; 4.鹤壁市大华实业有限公司,河南 鹤壁 458000)

引言

随着商业照明逐渐向大电流、高亮度、多集成方向发展,对高密度电流驱动LED的关注与日俱增。为了突破传统LED的限制,科研工作者提出了阵列式高压交/直流LED的概念[1-5]。阵列式高压交/直流LED是指在芯片制作过程中,通过多个LED微晶粒的串并联来实现交流高压供电。与传统封装高压LED相比,阵列式高压LED更节省空间,大大减小了LED的封装成本。在电流分布方面,高压LED芯片能够解决电流拥挤效应,使电流分布更均匀,从而抑制光效下降[6]。高密度电流驱动LED的最佳结构为倒装结构,即将正装结构的芯片倒扣在高热导率的支撑衬底上,从而改善LED的散热性能。

共晶焊是倒装LED常用的两种封装方法之一,是指在相对较低的温度下共晶焊料发生共晶物熔合的现象。共晶物直接从固态变到液态,不经过塑性阶段[7]。共晶焊芯片属于面面接触,与传统线焊技术和倒装焊技术相比,能够进一步提高热传导效率及机械强度。此外,共晶焊芯片无需制作凸点,工艺复杂度得到降低。

本文介绍了共晶焊制作倒装高压LED的制作工艺,制备由10颗LED微晶粒串联而成的共晶焊倒装高压LED,并且通过相关实验、Trace-pro光模拟及ANSYS热模拟,对共晶焊与倒装焊高压 LED 芯片的电学、光学及热学性能进行详尽地分析比较。

1 实验概况

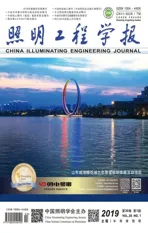

共晶焊倒装HV LED的制作流程如图1所示。首先使用ICP刻蚀暴露出n-GaN层用以制作N型接触,然后在此基础上,使用5 μm厚的光刻胶及900 nm厚的SiO2作为掩膜,刻蚀至蓝宝石衬底层来隔离各个LED微晶粒,实现微晶粒间的电隔离。随后制作P型反射电极,选用电子束蒸发法沉积Ni/Ag/Pt/Au(厚度为7/4 000/500/2 000 Å),金属薄膜覆盖整个p-GaN层,从而最大限度地提高光提取。蒸镀后为了形成良好的欧姆接触,在550 ℃空气气氛下对反射电极进行5 min的热退火。之后对PECVD沉积1 μm 的SiO2层对芯片进行钝化处理,从而防止后续N电极与P电极之间的短路。随后制作PN加厚电极Cr/Pt/AuSn(厚度为100/400/20 000 Å)。在我们的LED芯片中,P、N电极的高度差在1.9 μm左右,为了保险起见,N电极延伸至p-GaN层上,与P电极之间使用钝化层隔离开来,P加厚电极的目的是将P电极引出,使得P、N电极高度处于同一平面。这种结构对N电极的面积无特殊要求,仅需要考虑电流扩展问题。芯片制作完成后便是倒装支撑衬底的制作。基板制作完成后,采用共晶焊技术将两者键合,采用的焊料是AuSn (金80%,锡20%)。至此,共晶焊倒装HV LED器件制作完成。

图1 共晶焊倒装HV LED 工艺流程示意图Fig.1 The fabrication process of eutectic high voltage flip-chip LEDs (HV FC LEDs)

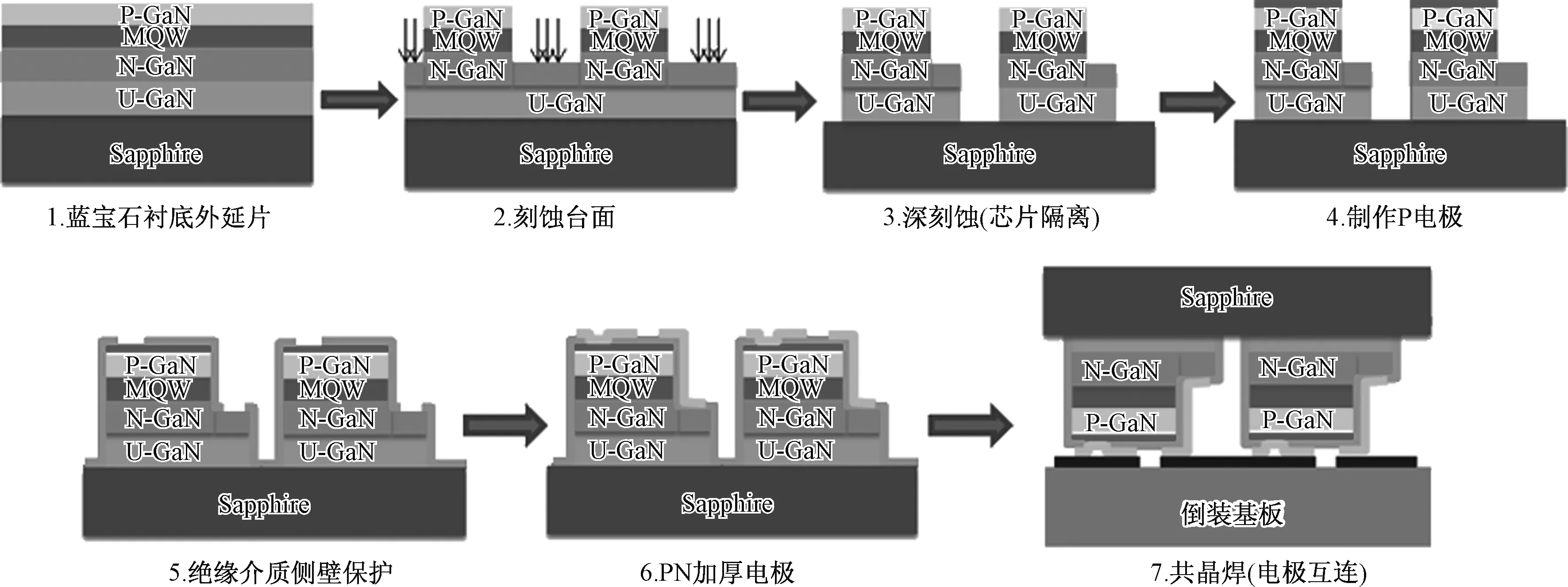

为了验证共晶焊倒装HV LED的性能,我们采用倒装焊LED与之进行对比,具体工艺流程如图2所示。首先进行ICP刻蚀暴露出n-GaN层、深刻蚀隔离以及P型欧姆接触的制作。接着制作N电极,N电极选用Cr/Pt/Au(厚度为100/400/14 400 Å)。之后PECVD沉积500 nm的SiO2层对芯片进行钝化处理,避免杂质原子的吸附,从而减少LED的漏电流。最后对蓝宝石衬底进行减薄划裂。倒装焊的工艺流程一般包括倒装基板金属化、金属凸点的制作以及芯片倒装三个步骤。Cr/Pt/Au(厚度为100/400/14 400 Å)金属体系作为互连电极被蒸发在AlN陶瓷基板上。电极制作完成后,采用植球机在电极表面植金球,金球直径为75 μm。LED芯片及Sub-mount制作完成后,采用超声倒装焊技术将两者键合[8, 9]。至此,倒装焊高压 LED器件制作完成。

共晶焊高压LED的制备过程中,我们使用的共晶焊设备为HYBOND公司的UDB141半自动共晶贴片机。而在倒装焊高压LED的制备过程中,我们采用EB方法来实现倒装基板的金属化,采用PALOMAR 8000全自动晶圆植球机实现金属凸点的制作,采用台湾旭东机械工业有限公司的FC001实现倒装焊工艺。

图2 倒装HV LED芯片工艺流程示意图Fig.2 The fabrication process of traditional high voltage flip-chip LEDs (HV FCLEDs)

2 结果与分析

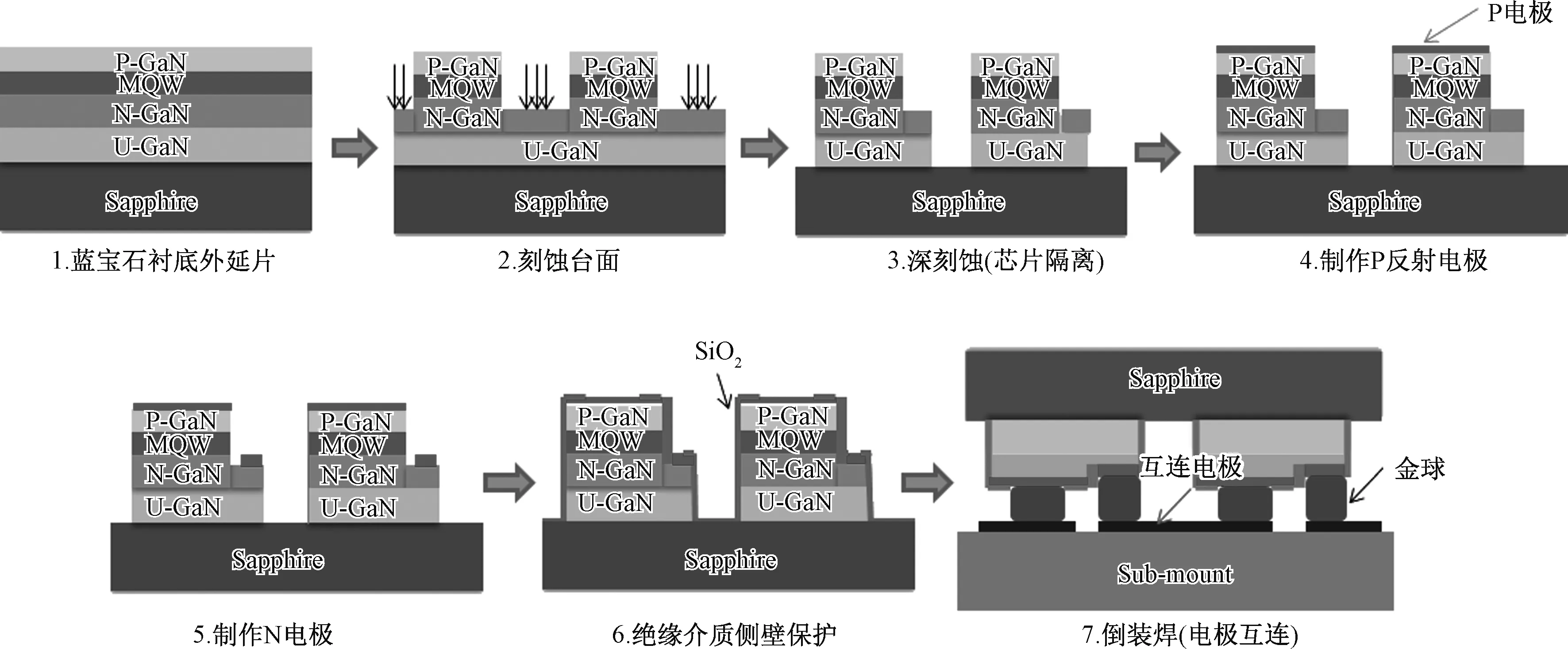

1)芯片外观。两种LED芯片的示意图如图3所示,其具体参数可参照表1。共晶焊HV LED的有效出光面积为1.09 mm2,是倒装焊高压LED的110%。倒装焊LED的金球凸点在压焊后直径扩展为100 μm左右,所以微晶粒N电极的尺寸只有超过100 μm,才能避免漏电的产生,这导致了过多有源区的损失。并且由于电极设计不合理,倒装焊LED电流分布非常不均匀。此外,由于倒装微晶粒的大小限制,每颗微晶粒仅有一个N pad与倒装基板通过金球连接,连接可靠性会影响整个倒装高压芯片。共晶焊高压LED的面面连接很好地解决了相关问题,因此它的有效出光面积得到了提升。此外,共晶焊高压LED相比倒装焊高压LED,侧壁长度更短,其侧壁出光面积是倒装焊高压LED的87.8%。

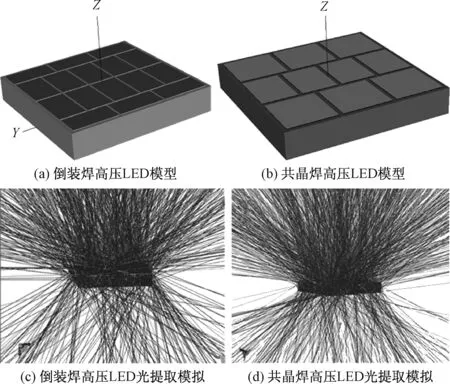

2)光提取模拟。我们使用Trace-pro光学追迹软件对倒装焊高压LED及共晶焊倒装HV LED的光提取进行了模拟。在建模过程中,我们忽略电极形貌及外延质量的差异,所建模型如图4所示。从光提取照片可以看出,与倒装焊高压LED相比,共晶焊结构的倒装HV LED光提取效率低了1.3%,这主要归因于此结构侧壁出光面积略小。

图3 两种LED芯片的结构对比Fig.3 Comparison of the structures of the two kinds of LED chips

表1 倒装焊高压芯片与共晶焊高压芯片参数对比Table 1 Parameters comparison of the traditional and eutectic-high voltage flip-chips

图4 倒装焊高压LED及共晶焊倒装HV LED 所建模型和光提取模拟Fig.4 The model and light-output simulation for traditional-and eutectic-high voltage flip-chips

图5 倒装焊及共晶焊高压LED的伏安特性曲线及光强分布图Fig.5 The I-V characteristic curve and light intensity mapping for traditional-and eutectic-high voltage flip-chips

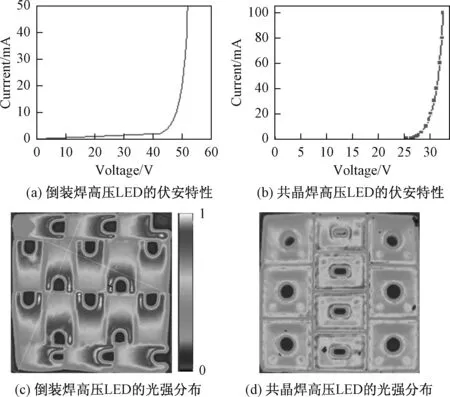

3)光电特性分析。我们通过伏安特性曲线对封装后的倒装焊及共晶焊高压LED进行了光电特性分析,结果如图5所示。倒装高压LED的开启电压基本上等于16颗微晶粒开启电压之和,在20 mA注入电流下,其单颗微晶粒的工作电压为3.1 V,总电压为49.8 V。共晶焊倒装HV LED的伏安特性显示,在20 mA注入电流下,共晶焊倒装HV LED的工作电压为30.0 V。

为了探索电极设计结构对LED光学特性的影响,我们使用LED光形分布量测仪对这两种结构的光强分布进行了检测。图5给出了两种芯片在1 W电注入功率下的光强分布照片。从光强分布图可以看出,共晶焊高压LED光强分布均匀,而倒装焊高压LED光强分布较为不均匀。由此可以推断,共晶焊高压LED具有比较均匀的电流扩展,几乎无电流拥挤效应。而倒装HV LED存在很明显的电流拥挤效应,电流拥挤现象出现在N电极边缘,这说明n-GaN的电流扩展存在一定的问题,问题的主要原因在于n-GaN层方阻与Ni/Ag电极电阻差异过大。

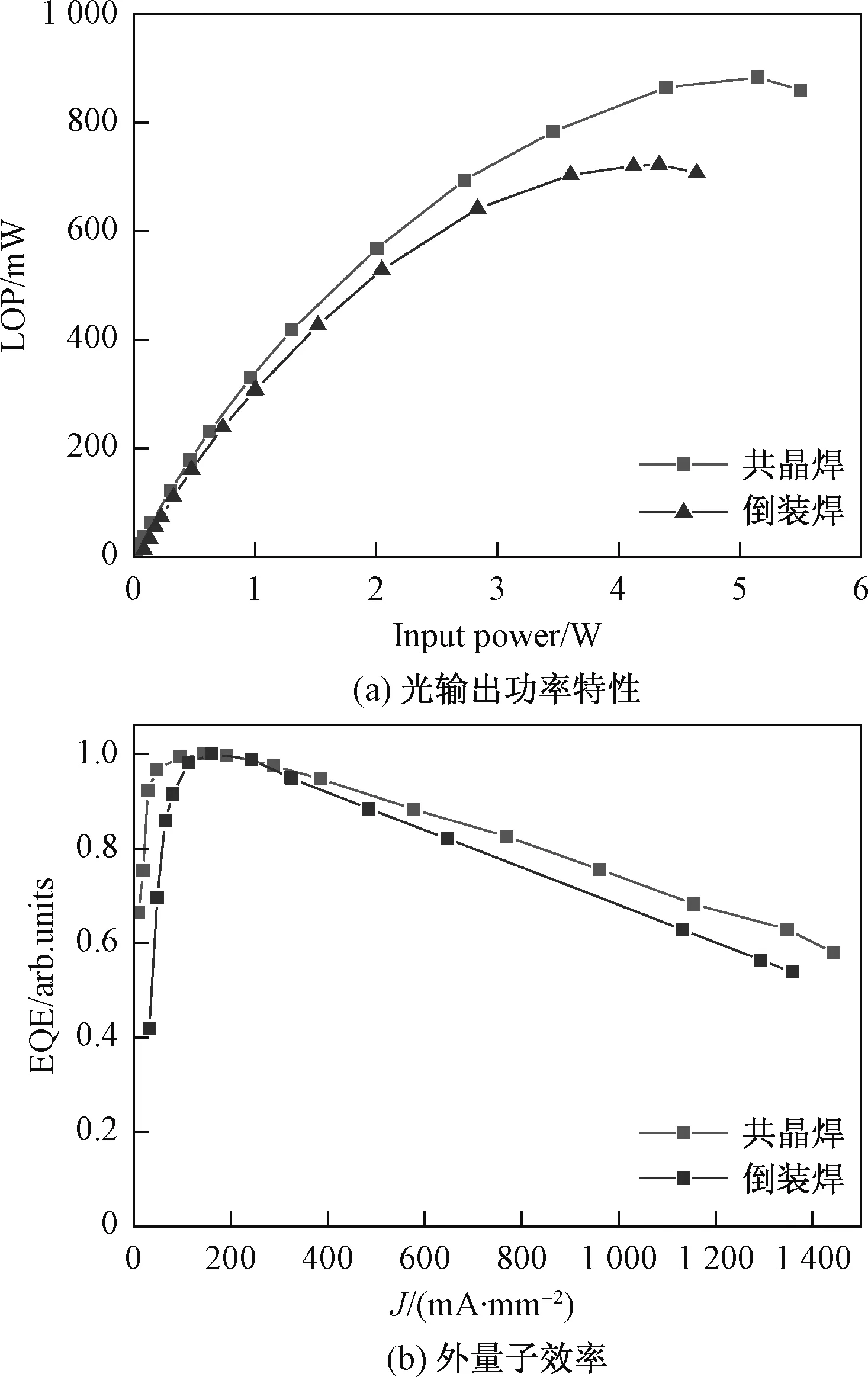

4)光输出功率及外量子效率的下降特性。随后,我们对这两种结构的光输出功率(LOP)特性进行了对比,如图6(a)所示。在1 W电注入功率下,共晶焊倒装高压 LED的光输出功率为340.6 mW,相比倒装焊HV LED提高了10.5%,这主要归因于共晶焊LED更均匀的电流扩展特性。同时,共晶焊倒装HV LED具有更好的饱和特性,光特性的饱和来源于热效应的积累,说明共晶焊HV LED具有更好的散热特性。此外,我们还对这两种结构的外量子效率(EQE)及峰值波长随电流密度的变化进行了表征,如图6(b)所示。从归一化的外量子效率曲线中可以明显观察到,在1 000 mA/mm2注入电流密度(J)下,共晶焊高压 LED的外量子效率只下降了26.2%,而倒装焊高压LED的外量子效率下降了32.2%。

图6 倒装焊及共晶焊倒装HV LED 的LOP及发光效率下降特性Fig.6 LOP curves and efficiency droop characteristics for traditional-and eutectic-high voltage flip-chips

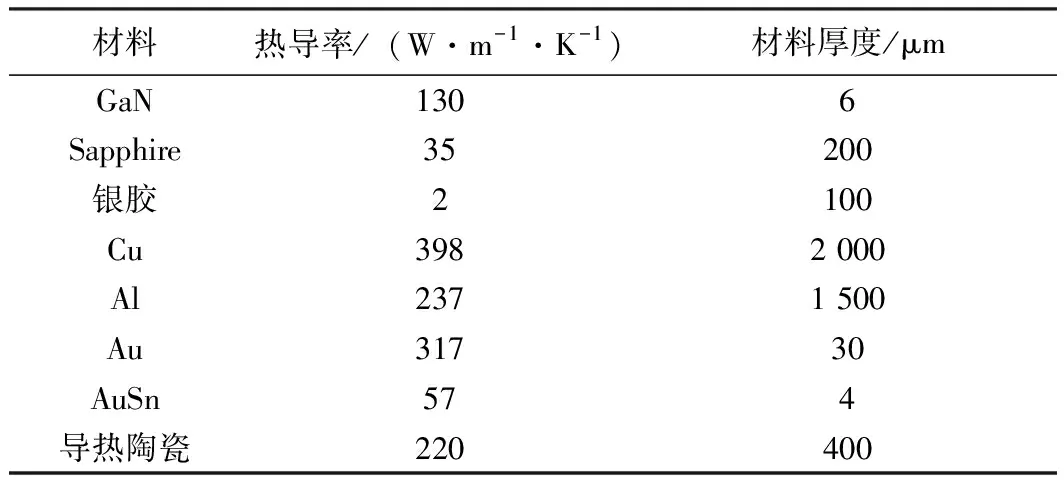

5)热分布模拟。进一步,我们使用有限元模拟分析方法对这两种LED 进行了热模拟,芯片的产热功率均设定为0.7 W。表2为模拟中所用材料的热导率及厚度。芯片产生的热量通过热传导到管壳再到散热体,最终通过对流或辐射释放到环境中。管壳选用半径为2 mm的铜制圆柱体,散热体为半径10 mm的铝基板。倒装结构中采用导热陶瓷作为倒装基板,其尺寸为1.6 mm×1.6 mm×0.4 mm。边界条件为:与空气的对流系数为15,环境温度为25 ℃。

模拟中所用的倒装焊LED器件的结构模型如图7(a)所示,右下角是倒装芯片与基板之间的侧视图。整个LED系统的温度场分布如图7(b)所示。从模拟结果来看,倒装焊HV LED的最高温度为89.3 ℃。

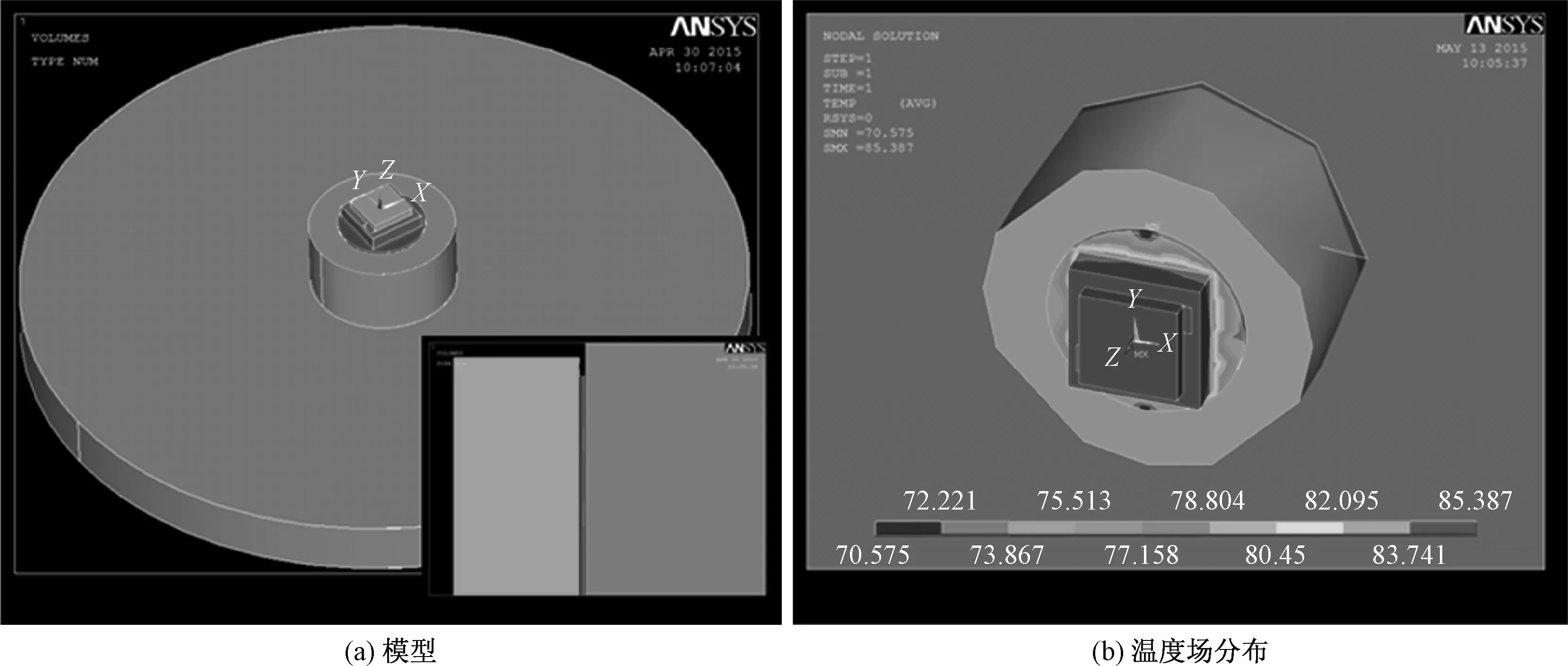

图8(a)是共晶焊倒装LED系统的模型,右下角是倒装芯片与基板之间的侧视图。可以看到,共晶焊倒装芯片属于面面接触。图8(b)显示了共晶焊倒装LED系统的温度场分布。系统最高温度为85.4 ℃,比倒装焊HV LED的最高温度低3.9 ℃,证实了共晶焊倒装LED具有更好的散热特性。

表2 模拟中所用材料的热导率及厚度Table 2 Thermal conductivity and material thickness for simulation

图7 倒装焊倒装高压 LED系统模型和温度场分布Fig.7 The model and temperature field distribution for traditional high voltage flip-chips

图8 共晶焊倒装HV LED系统模型和温度场分布Fig.8 The model and temperature field distribution for eutectic high voltage flip-chip

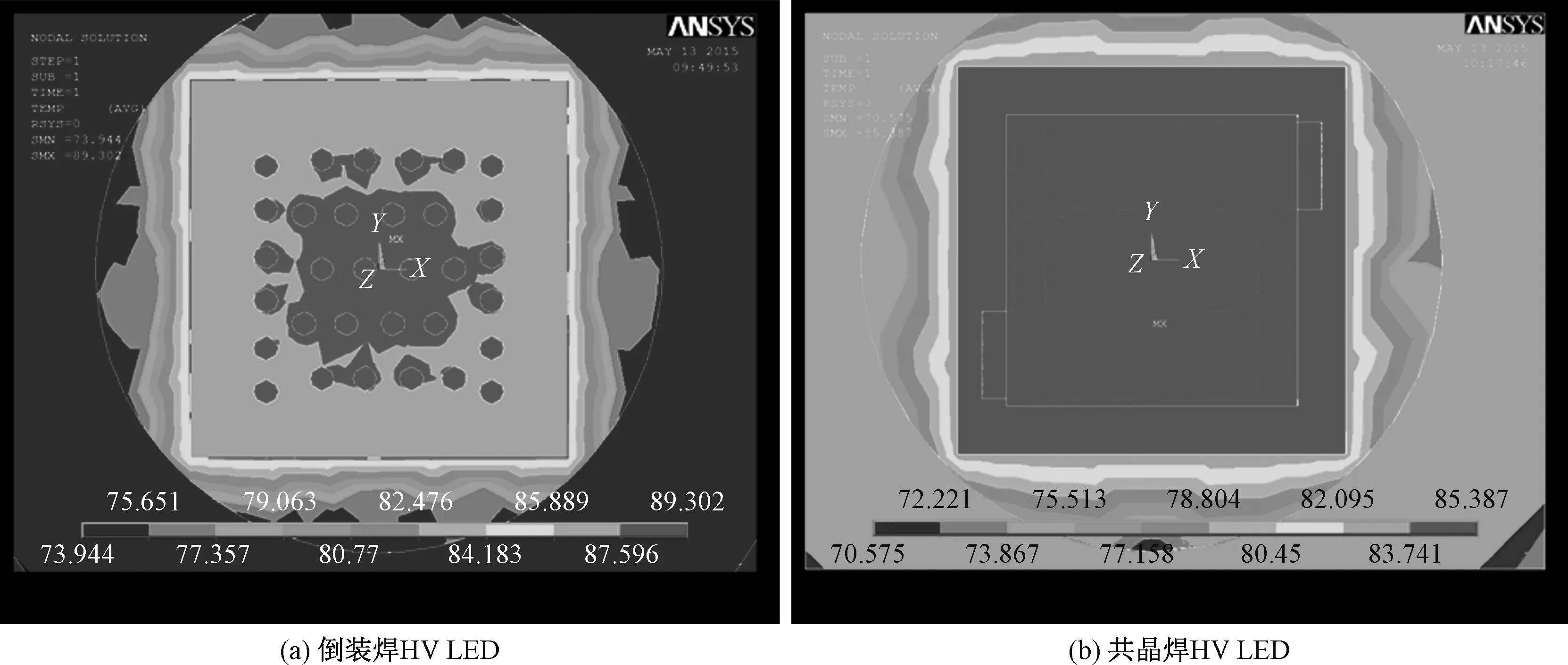

图9给出了倒装焊以及共晶焊倒装基板表面的温度分布。倒装焊高压 LED中,芯片与基板通过32个Au凸点连接。从图9(a)中可以看到,倒装焊基板的温度场分布不均匀,凸点位置的温度相对更高。相对倒装基板四周而言,基板中心位置的温度更高,说明中心位置的热量更难释放出去。然而,共晶焊倒装HV LED中,芯片与基板通过金属电极连接。倒装基板表面温度分布均匀,见图9(b),说明面面接触增加了LED的散热通道,从而提高了倒装芯片的散热能力,使其更适合于大电流的操作。

图9 倒装焊和共晶焊HV LED倒装基板表面温度分布Fig.9 Flip-chip surface temperature mapping for the traditional-and eutectic-high voltage flip-chips

3 结论

我们对共晶焊工艺进行了探索,制备了由10颗LED微晶粒串联而成的共晶焊倒装高压 LED。通过与倒装焊高压LED的性能对比,证实共晶焊倒装高压LED在1 W电注入下光功率提升10.5%,光效下降现象得到进一步的缓解。同时,ANSYS热模拟结果表明共晶焊倒装结构由于面面接触,与点面接触的倒装焊高压LED相比,增加了散热通道,具有更好的散热特性,更适合大电流驱动。