4K视频流HEVC编解码传输的异构多核方法研究

2019-04-04李毅航张宽尹雅君唐俊龙唐立军

李毅航 张宽 尹雅君 唐俊龙 唐立军

关键词: 超高清视频; 4K视频流; HEVC编解码传输; 异构多核; 视频分辨率; 编码速率

中图分类号: TN919.3?34; TP302.1 文献标识码: A 文章编号: 1004?373X(2019)06?0121?05

Abstract: The HEVC video codec standard is commonly used to compress and decompress high?definition video data, but for the ultra?high definition video data of 4K and above, the traditional video stream codec transmission method is difficult to achieve high?efficient video compression ratio and compression speed. Therefore, a heterogeneous multi?core video stream transmission method based on ARM+FPGA is proposed in this paper for the HEVC codec of ultra?high definition video stream. The Linux system is built by using the ARM, so as to realize multi?tasking processing and real?time monitoring. The FPGA is used to realize hardware acceleration, so as to receive, convert, process, encode, decode, output and display video streams. The HEVC codec transmission test was conducted on the Zynq UltraScale+MPSOC all programmable platform for the 4K video with a resolution of 3 840×2 160, frame rate of 30 f/s, pixel format of YUV420, color depth of 8 bits, and time duration of 120 s. The test results show that the time duration of the encoding is only 71s, and the compression rate of video data is as high as 6.19%, which can satisfy the codec transmission requirement of the 4K video.

Keywords: ultra?high definition video; 4K video stream; HEVC codec transmission; heterogeneous multi?core; video resolution; encoding rate

0 引 言

随着4K超高清视频(分辨率3 840×2 160)不断的推广和应用,由于图像清晰度的大幅提高,导致视频流数据量的剧增,因此,迫切需要使用HEVC/H.265高效的视频编解码标准,以解决海量的视频图像传输以及储存的问题[1]。而HEVC的编码复杂度高,传统的嵌入式方案很难满足4K视频流稳定快速的传输,保障HEVC编解码高效压缩以及提高编解码速率[2]。

本文采用Zynq UltraScale+MPSOC全可编程平台,利用软硬件协同的机制,构建异构多核的软硬件系统构架,探索一种高效的视频流编解码传输方法。针对4K视频流庞大的数据量传输问题,对视频直接内存存取进行研究,以减少数据搬运过程中资源的占用;对视频流数据类型分析,对不同的视频数据进行转换处理研究,来适配编解码器需求的格式。根据编解码器对数据的吞吐量,研究视频流传输通路的带宽、时钟以及延迟等,来保证编解码高效运行[3]。

1 视频流编解码传输方案

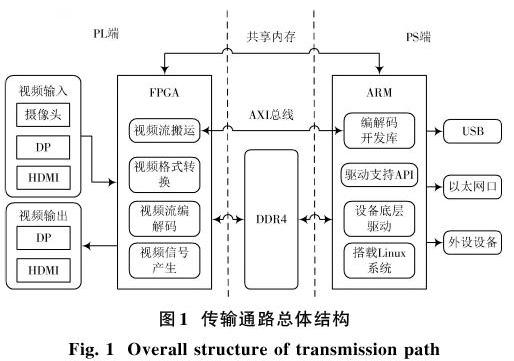

通常采用PC机进行4K视频HEVC编解码,但由于自身体积较大,不便集成和小型化,而ARM往往受限于自身的性能不足,难以进行HEVC编解码运算,单纯的FPGA因为开发周期过长,且应用形式单一,不能快速适应视频分辨率改变和视频流格式变化。本文主要探讨异构多核的视频流传输方法,利用FPGA硬件加速的特性来设计视频流编解码传输通路,利用ARM多任务处理与实时监控的特点来改变传输通路性能参数,高效灵活的方式保证4K视频流从接收、转移、处理、编解码和输出过程中稳定传输。传输通路总体结构如图1所示。

1.1 传输通路构架与速率要求

若以4K图像30 f/s,YUV420像素格式,颜色深度为8位的视频流接收,接收的数据带宽[4]将达到约5.0 Gb/s。为了更好地传输4K视频流,要求传输速率[5]最好能达到接收速率的4倍,即20.0 Gb/s左右。

视频流接收,采用DisplayPort 1.2高清数字显示接口标准,通过4路数据传输达到21.6 Gb/s,单路传输为5.4 Gb/s,能够支持4K视频流传输。

视频流转移,使用VDMA高速数据传输将视频流存储到内存中进行下一步处理,最高数据带宽能达到1 024 bit,选择以128 bit带宽,200 MHz的频率运行,传输速率约为23.8 Gb/s。

视频流处理,对采集的视频流数据类型进行分析,通过像素格式转换、像素位数改变、像素数据转移等方式来得到HEVC编解码能支持的视频流格式。

视频编解码,搭建多路高带宽的数据线,并尽可能提高时钟频率来保证视频的传输与提高编解码器效率。视频流输出,对于解码完成的数据,采用2?4路HDMI1.4高清数字显示接口标准输出分屏显示,每路HDMI数据传输速率最高达到10.2 Gb/s,2路以上即可满足性能需求。

1.2 传输通路控制方案

ARM与FPGA的数据交互。ARM与FPGA相结合的异构多核构架,有利于优势互补,ARM使FPGA处理数据以及修改配置更加灵活,FPGA使ARM数据运算以及数据存储更加迅速,ARM与FPGA通过AXI总线实现数据交互[6]。FPGA中每个IP核拥有自己的基地址,ARM通过AXI总线读/写基地址偏移的寄存器数据,来检测与控制IP核数据与参数。

FPGA与ARM内存共享。在ARM端进行PetaLinux操作系统移植,进行编解码顶层设计,使FPGA与ARM协同工作。通过FSBL(一级引导程序)对ARM进行初始化配置,加载FPGA逻辑电路固件,生成U?boot引导Linux内核启动,读取设备树文件来加载底层硬件驱动,使ARM可以控制驱动程序,分配内存地址空间,运行Linux系统,实现FPGA与ARM内存共享。从而达到与FPGA数据交互的目的。

编解码的优化。ARM通过操作系统来控制FPGA中的视频流编解码,来实现编解码优化与应用。把Linux用户空间分为三层:底层为编解码控制软件,包括定制内核模块、定制用户空间库、实现编解码基本控制;中层为OpenMAX综合层,使用开源的多媒体组件标准接口,实现编解码软硬件交互;顶层为Gstreamer应用层,利用开源的跨平台多媒体构架,提供编解码,以及视频传输通道基本操作。

2 视频流编解码传输实现

2.1 视频流高速数据传输

FPGA内部的数据传输往往采用DMA的方式,但普通DMA的传输速度[7]大约为750 Mb/s,远不能达到4K视频流的传输需求,因此,使用视频流专用的DMA来搬运庞大的视频数据。VDMA能支持数据带宽为8的倍数,最高支持1 024 bit,时钟频率能达到200 MHz左右。在视频流数据映射到内存地址之前建立一个异步行缓冲区来处理帧速率变化,最多缓存32帧数据,设计控制和状态寄存器与AXI总线连接,便可直接在ARM端配置异步行缓冲区临时保存像素数据。同时ARM也能修改VDMA的数据带宽与时钟频率等参数,实现VDMA实时改变传输速率来存储数据。建立相互独立的写入与读取线路,对内存地址映射,访问未对齐内存地址数据,允许帧缓存区从内存中任何地址开始读写,保障数据不会丢失。视频流输入/输出与外部时钟信号同步,使VDMA成为异步全双工通信模式。VDMA结构框图如图2所示。

2.3 视频流编解码传输分析

2.3.1 編解码传输线路与时钟实现

在相同质量的视频流下,HEVC/H.265编码率比AVC/H.264提高大约50%,所以HEVC编解码器需要更高的数据吞吐量[9]。设计双路的编解码数据流,数据流带宽达到128 bit,实现编解码同时进行并提高编解码数据流的传输速度。

由于整个传输通路的速率瓶颈在于编码器的编码速度,故建立编码器缓存器来保障编码器更流畅的编码。编解码器都设计有一个32位MCU来实现与硬件的交互,MCU接收到来自ARM的命令,把它分解为多个slice或者tile级命令,尽可能地降低编解码解析命令所花费的时间。

编解码在超高的工作频率下运行,必须保证时钟频率的稳定。锁相环是闭环的控制系统,可以锁定输入信号的相位,能输出精确稳定的时钟[10]。锁相环参考时钟频率高达667 MHz,实现编解码高速运算,通过分频出4路时钟,并提供给编码器、编码器的MCU、解码器与解码器的MCU,异步的时钟能使编解码器运行时互不干扰,大幅度降低编解码出错概率。同时编解码器的时钟并不是固定的,在ARM端的控制下,实现系统时钟的动态调节,以便编解码器对不同类型的视频流都能进行最优化的编解码。编解码设计框图如图4所示。

2.3.2 传输通路延迟性分析

传输通路的延迟是研究编解码传输通路一个很重要的参数属性,即指视频流从接收。经过一系列过程,再到视频数据显示所需要的时间,延迟是层层叠加的,主要包括图像采集延迟,来源帧在DMA缓冲延迟、编码器延迟、传输比特流缓冲延迟、网络传输或者存储延迟。对于解码来说,存在缓冲编码图像延迟、解码器延迟、显示帧缓冲延迟以及显示器显示延迟。编解码器的延迟基本是稳定的,为输入延迟、硬件延迟与输出延迟的总和。编码器主要延迟在于对图像重新排序时缓存一帧图像所花费的时间。解码器主要延迟在于熵解码等待的时间和像素解码等待的时间。经过FPGA硬件逻辑分析仪测试所得传输通路各段延迟时间如图5所示。

3 4K视频流编解码传输测试及结果分析

Xilinx公司的Zynq UltraScale+MPSOC ZCU106开发板包含集成FPGA与ARM的XCZU7EV异构芯片,使用该开发板对4K视频流编解码传输方法进行测试与验证。

3.1 视频流编解码传输通路测试

通过超清摄像头采集RGB视频数据,经过VDMA把视频流映射到内存地址,同时把RGB像素格式转换为YUV420像素格式,对视频流进行HEVC编码,再对视频流进行HEVC解码,把解码后的视频流通过Displayport 1.2高清数字显示接口在显示屏上显示。任意采集视频,视频图像播放正常,没有出现卡顿、失帧、错位等情况,显示成像效果如图6所示,表明视频流传输通路正常运行。

3.2 编解码压缩效果

为了证明传输路通能够保证4K视频经HEVC编解码后能稳定输出显示,对传输通路中耗时最长,也是传输瓶颈所在的编码部分进行测试。对视频分辨率为3 840×2 160,帧率为30 f/s,时长120 s,像素格式为YUV420,颜色深度为8位的视频进行H.265编码。测试结果表明,编码所用时长为71 s,远小于视频时长120 s,能满足对4K视频播放需求。为了测试在传输通路中编解码的压缩率,对以上的编码视频进行HEVC解码,测试结果表明,解码后的视频原始文件大小为1 307 MB,经过HEVC编码后的文件大小为81 MB,压缩率达到6.19%。

4 结 语

本文采用异构多核体系构架,利用FPGA实现4K视频流编解码传输硬件加速,ARM对其进行多任务处理和实时监控,搭建VDMA对采集的视频流进行搬运,提高了视频流传输速度,保证了视频传输的稳定性。同时对视频流格式进行处理,转换为编解码支持的视频流,采用多通道、高带宽的数据通道大幅提高了编解码传输率,搭载Linux系统也使编解码更具灵活性。这种视频流编解码传输方法,比传统处理器在编解码速率上有着明显的优势,其压缩率和压缩速率能很好地满足4K超高清视频流的传输要求。

参考文献

[1] SUZUKI K, TAJIRI T, TAKABA N, et al, Method of downsizing the 4K uncompressed video signal generator [C]// Proceedings of IEEE 6th Global Conference on Consumer Electronics. Nagoya: IEEE, 2017: 1?3.

[2] OH J G, WON Y J, LEE J S S, et al. A convergence broadcasting transmission of fixed 4K UHD and mobile HD services through a single terrestrial channel by employing FEF multiplexing technique in DVB?T2 [J]. Electrical engineering, 2017, 99(3): 1021?1042.

[3] KIM Y, CHOI J S, KIM M. A real?time convolutional neural network for super?resolution on FPGA with applications to 4K UHD 60 fps video services [J]. IEEE transactions on circuits and systems for video technology, 2018, 8: 1.

[4] PETRIN?AK L, GRBI? R, KAPROCKI Z, et al. Challenges in 4K UHD multimedia device testing [C]// Proceedings of International Conference on Zooming Innovation in Consumer Electronics. Novi Sad: IEEE, 2017: 5?8.

[5] HWANG S, SONG J, LEE Y, et al, A 1.62~5.4 Gb/s receiver for display port version 1.2a with adaptive equalization and referenceless frequency acquisition techniques [J]. IEEE transactions on circuits and systems I: regular papers, 2017, 64(10): 2691?2702.

[6] 黄超,鲁湛,贺健,等.基于ZYNQ的微型光谱仪高速数据采集系统设计[J].现代电子技术,2016,39(3):109?111.

HUANG Chao, LU Zhan, HE Jian, et al. Design of ZYNQ?based high?speed data acquisition system for micro?spectrometer [J]. Modern electronics technique, 2016, 39(3): 109?111.

[7] KAVIANIPOUR H, MUSCHTER S, BOHM C. High performance FPGA?based DMA interface for PCIe [J]. IEEE transactions on nuclear science, 2014, 61(2): 745?749.

[8] SON T N, HOANG T M, DZUNG N T, et al. Fast FPGA implementation of YUV?based fractal image compression [C]// Proceedings of IEEE 5th International Conference on Communications and Electronics. Danang: IEEE, 2014: 440?445.

[9] ARAYACHEEPPREECHA P, PUMRIN S, SUPMONCHAI B. Flexible input transform architecture for HEVC encoder on FPGA [C]// Proceedings of 12th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology. Hua Hin: IEEE, 2015: 2?5.

[10] XIE Changying, ZHANG Maosong, LI Guoli, et al, Design of PLL based On FPGA under unbalanced conditions [C]// Proceedings of IEEE 11th Conference on Industrial Electronics and Applications. Hefei: IEEE, 2016: 315?320.