基于FPGA的全数字延时锁相环的设计

2019-04-04李锐田帆邓贤君单长虹

李锐 田帆 邓贤君 单长虹

关键词: 全数字延时锁相环; 锁相精度; 时钟延时; Quartus Ⅱ; 现场可编程门阵列; 电路仿真

中图分类号: TN402?34 文献标识码: A 文章编号: 1004?373X(2019)06?0069?03

Abstract: In allusion to the problems such as low phase?locking accuracy, slow phase?locking speed and low integration level of the traditional analog delay?locked loop (DLL), an all?digital DLL is proposed. The DLL is designed by using the electronic design automation technology. The editing and analysis of the DLL are conducted by using the Quartus Ⅱ software. The simulation results show that the DLL can perform quick lock with high precision, has strong portability, and is suitable for various application fields such as microprocessor, memory and general IC designs.

Keywords: all?digital DLL; phase?locking accuracy; clock delay; Quartus Ⅱ; FPGA; circuit simulation

0 引 言

延迟锁相环(DLL)是通过负反馈回路,将一段延迟线的延迟锁定在一个特定的值上。延迟锁相环是围绕着一条延迟可控的延迟线的负反馈系统,相对而言,锁相环(PLL)则是围绕着频率可控振荡器的负反馈系统[1],其已被广泛用作片上系统(SoC)微处理器的时钟发生器[2?3]。DLL与PLL的主要区别是DLL用压控延迟线(VCDL)取代了PLL中的数控振荡器(DCO),由于这个区别,DLL能快速对信号进行锁定,而且抗干扰能力强、抗抖动性能好。所以DLL越来越多地被引入芯片中,作为生成稳定的延迟或多相位的时钟信号[4]。现实中,一般将DLL分为模拟型DLL和数字型DLL。模拟DLL抗抖动的能力虽然强于数字DLL,但是其锁定时间较长,需要反复调整才能实现锁定。而对于数字延迟锁相环来说,在保持足够高的锁相精度情况下,经过数次延时的调整就可以实现同步。

另外,模拟DLL设计较复杂,可移植性差,随着工艺的改变,其功耗也随之增加[5]。针对模拟DLL锁相精度不高、锁相速度慢、集成度低等问题,本文提出一种全数字延迟锁相环,阐述了其工作原理,介绍了系统的电路结构以及各个模块的设计方法,并利用Modelsim进行了仿真验证。

1 全数字延迟锁相环的系统结构与工作原理

全数字延迟锁相环主要由鉴频鉴相器模块、相位测量模块、相位调节模块和移相输出模块构成,其结构见图1。

图1中:Clkin为给定的时钟信号;Clkfb为经过系统内部的时钟网络所产生的时钟偏移信号;鉴频鉴相器检测输入信号Clkin和反馈信号Clkfb的相位差,可产生超前或滞后的相位差信息。当相位超前信号up是高电平时,对其进行计数得到超前相位差值upnum;当相位滞后信号dn是高电平时,对其进行计数得到滞后相位差值dnnum。

同时,测量Clkin的频率,并产生一个同频率的时钟。相位测量模块根据超前或者滞后信号选择粗调或者精调,并产生相位调节的延时级数信息。相位调节模块在同频时钟的作用下,根据超前或者滞后的相位差值,通过调节延时级数来调整相位的大小,最终达到相位锁定的目的。相移输出模块可以将锁定后的信号移相90°,180°,270°,得到多种相位的输出信号,以满足不同用途的需求。

2 相位调节模块的设计

相位调节模块主要由延时控制器构成,其结构框图如图2所示。

控制器根据相位测量模块所产生的延时级数信息,分别对粗调或精调电路模块进行延迟控制。当输入信号超前于反馈信号时,其延时时间调整为输入时钟周期T减去相位超前信号up为高电平的持续时间,调整方式为粗调加精调;而当反馈信号超前于输入信号时,只采用精调来实现延时调节。粗调一次延时[12]时钟周期,精调分4层,每层16级。根据采样定律,每级最多延时输入信号的[T2],一共可以调4次,可以精确地对延时进行调整。延时链主要由D触发器构成,每经过一个D触发器可延时一个时钟周期,粗调和精调的电路模块中都有64級延时单元。

3 各个模块的设计与仿真

3.1 鉴频鉴相器模块

鉴频鉴相器采用Verilog语言进行设计,其实现原理是通过检测输入与反馈信号的上升沿,判断其相位差,并生成超前或者滞后信号,同时对输入信号进行计数,生成一个与输入信号同频率的时钟。图3为仿真波形。

当输入信号 clock_in超前于反馈信号clock_fb时,产生超前信号up;当输入信号 clock_in滞后于反馈信号clock_fb时,产生滞后信号dn。由于外部时钟信号进入系统内部可能产生亚稳态,故需要使作用于相位调节模块的时钟信号与输入信号同频,这主要是通过采样与变换电路来产生一个与输入信号同频异相的时钟信号clockgen_out。

3.2 相位测量模块

本方案是基于计数器思想的延时设计方法,延迟模块以数字信号的上升沿和下降沿作为触发信号分别控制输出高低电平[6?7]。

相位测量模块的波形图如图4所示,当up信号为高电平时,进行计数,输出超前相位差值upnum;当dn信号为高电平时,进行计数,输出滞后相位差值dnnum。其中up_cnt为相位超前时需要调节的延时级数;dn_cnt为滞后时需要调节的延时级数。

3.3 相位调节模块

相位调节模块的仿真波形如图5所示,clk_d为经过延时链的时钟,其频率与输入信号相同。Sel为选择超前或者滞后信号。相位调节模块分为粗调和精调[8],当up为高电平时,启用粗调,粗调分为64级,然后启用精调,精调分4层,每层16级,一共调4次。当dn为高电平时,启用精调。该延时模块取代了传统DLL中的压控延迟线,改用全数字延时模块,使其可控性更高,受温度的影响更小,且易于集成。

3.4 相移模块

相移模块中时钟周期测量电路将输入信号的周期转化为延迟单元数N,然后,相移电路根据周期测量结果将相位锁定后的电路输出信号分别延迟[N4],[N2],[3N4]个单元,即分别延迟[14]周期、 [12]周期、[34]周期。得到4个时钟相位,4个不同相位时钟的相位差均为90°。

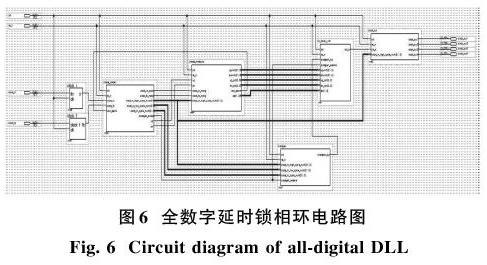

4 整体设计和仿真

全数字延时锁相环的系统设计采用自顶向下的方法,首先,利用Verilog语言设计各个模块,然后将各模块的端口连接,其电路图如图6所示。为防止外部信号进入系统内部可能产生的亚稳态,在输入和反馈端口后接两个三级D触发器clock_i与clock_f。图中:phase_detect为鉴频鉴相器;phase_measure为相位测量模块;clockgen为测频模块;ctl_delay_link为相位调节模块;clock_out为移相模块。

本系统设计完成后,在输入信号的频率范围5~100 MHz内取值,分别进行了系统仿真。仿真实验证明,输入信号在该频率范围内,其锁定时间为12个输入信号周期,锁定精度为20 ps。以输入频率取5 MHz和25 MHz为例,给出了系统仿真波形如图7和图8所示。

图中:clk为系统时钟;rst_n为复位信号;clock_in为输入信号;clock_fb为反馈信号;clock_out1,clock_out2,clock_out3,clock_out4分別为移相0°,90°,180°,270°后的系统输出信号。

与传统锁相环的设计方法相比较[9],本文所提出的全数字延迟锁相环不仅在性能上有了较大的提高,而且其延迟单元数目也大大减少,既提高了锁相环的锁定精度和锁定速度,也简化了电路结构、降低了功耗。

5 结 语

本文提出的全数字延迟锁相环,其锁定时间为12个输入信号周期,锁相范围为5~100 MHz,锁相精度为20 ps。仿真结果表明,该全数字延迟锁相环具有锁相速度快、锁相精度高、电路结构简单、可移植性好和易于集成的特点,可广泛应用于系统时钟管理,满足不同用途的需求。

注:本文通讯作者为单长虹。

参考文献

[1] 张刚.CMOS集成锁相环电路设计[M].北京:清华大学出版社,2013.

ZHANG Gang. Design of CMOS integrated phase?locked loops [M]. Beijing: Tsinghua University Press, 2013.

[2] CHEN X, YANG J, SHI L. A fast locking all?digital phase?locked loop via feed?forward compensation technique [J]. IEEE transactions on very large scale integration systems, 2011, 19(5): 857?868.

[3] FAISAL M, WENTZLOFF D D. An automatically placed?and?routed ADPLL for the medradio band using PWM to enhance DCO resolution [C]// Proceedings of IEEE Radio Frequency Integrated Circuits Symposium. Seattle: IEEE, 2013: 115?118.

[4] 保慧琴,尹国福.快速锁定的全数字延迟锁相环研究[J].微处理机,2016,37(1):11?14.

BAO Huiqin, YIN Guofu. A fast?locking all?digital delay?locked loop [J]. Microprocessors, 2016, 37(1): 11?14.

[5] 张健.基于数字DLL时钟发生器的设计[D].西安:西安电子科技大学,2013.

ZHANG Jian. Design of digital DLL clock generator [D]. Xian: Xidian University, 2013.

[6] 邱有刚,黄建国,李力.基于FPGA数字延迟单元的实现和比较[J].电子测量技術,2011,34(9):65?68.

QIU Yougang, HUANG Jianguo, LI Li. The implementation and comparison of DDL based on FPGA [J]. Electronic measurement technology, 2011, 34(9): 65?68.

[7] BRANDONISIO F, KENNEDY M P. First order noise shaping in all digital PLLs [C]// Proceedings of IEEE International Symposium of Circuits and Systems. Rio de Janeiro: IEEE, 2011: 161?164.

(上接第71页)

[8] 罗宁,陈原聪,赵野.应用于全数字锁相环的高性能数控振荡器设计[J].微电子学与计算机,2015,32(12):59?62.

LUO Ning, CHEN Yuancong, ZHAO Ye. Design of high performance digitally controlled oscillator for all?digital phase?locked?loop application [J]. Microelectronics & computer, 2015, 32(12): 59?62.

[9] NGUYEN A T, JOSE S. Fast?locking DLL circuit and method with phased output clock: 6501312B1 [P]. 2002?12?31.

[10] 赵雯,尹军舰,赵潇腾,等.PLLFS快速锁定方法的研究与设计[J].电子设计工程,2017,25(9):162?166.

ZHAO Wen, YIN Junjian, ZHAO Xiaoteng, et al. Analysis and design of fast?lock methods for PLLFS [J]. Electronic design engineering, 2017, 25(9): 162?166.