多芯片组件电源分配系统(PDS)的建模与仿真

2019-03-23畅艺峰邹旭军尤海艳谭宪文雷群龙

畅艺峰,邹旭军,尤海艳,谭宪文,雷群龙

(深圳市中航比特通讯技术有限公司 专用通讯承载网络重点实验室,广东 深圳 518000)

0 引 言

多芯片组件(MCM)是将2个或2个以上的大规模集成电路裸芯片和其他微型元器件电连接于同一块高密度互连基板上,并封装于同一外壳内所构成的具有一定部件或系统功能的高密度微电子组件。MCM封装技术具有降低互连延迟和提高封装密度的优势,可广泛应用于高性能系统[1]。随着MCM工作频率的升高和上升沿的缩短,电源的波动将对系统影响较大,出现电源完整性问题(PI)。电源噪声的产生可归因为非理想电源分配系统(PDS)。电源分配系统包括系统和局部电源分配网络,作用是给系统内器件提供电源。这些系统器件均对电源平稳性有一定要求。

目前,国内外对MCM电源分配系统已有相关研究[2],如采用有限时域差分法(FDTD)对局部电源分配系统进行仿真和优化。该方法只限于一阶近似,且对有源电路建模所得的封装响应不够精确。通过对MCM高速电路的电源阻抗分析,说明增加去耦电容的必要性。基于此,建立包含去耦电容的PDS模型,并仿真得到参考平面对信号传输质量的影响,而两驱动端波形在电压参考位置的波形相差15 ps。相较于SPICE模拟结果,本文方法得到的电压波动减小了10 mV,验证了方法的正确性。

1 电源阻抗设计

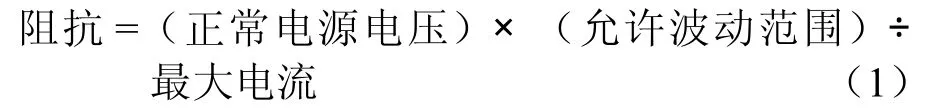

由于电源平面存在阻抗,瞬间电流通过时会产生一定的电压降和电压波动,而高速电路器件要求电源工作在正常电压的±4%之内。为保障器件正常工作,需降低电源阻抗。由电源阻抗表示式(1)可知,随着电源电压的减小,瞬间电流不断增大,大大降低了所允许的最大电源阻抗。

在时钟的上升沿和下降沿,电源系统的瞬间电流发生变化。电源电压波动与阻抗的关系式为:

其中,R、L分别为电源电阻和电感。

通过分析可知,增加去耦电容可满足电源阻抗要求。去耦电容的主要参数是等效交流阻抗,可表示为:

其中,RESR为电容串联电阻;Xac为电容等效交流阻抗;L为分立电容的电感之和。

2 电源分配系统建模

图1为电源层为参考平面的缓冲器驱动微带线的等效电路模型。由图1可知,信号在上拉转换时,无电流通过去耦电容;信号在下拉转换时,流经去耦电容的电流是信号电流的2倍。因此,应选择地层为参考平面,并保证回流通过时信号不失真。

本文选择地层作为参考平面,建立的等效电路模型如图2所示。由图2可知,当NMOS导通或关闭时,电源须快速提供电流,但电源路径上的串联电感会阻碍电流通过。若该电感较大,则当瞬间电流变化较快时,输出缓冲器和电源会被完全分隔,导致电源无法提供所需电流。I/O单元上的电压偏低,即出现地弹。设计中增加的去耦电容作为局部电源或I/O的电源供给系统,可在开关输出时提供必要的瞬间电流,保证信号的完整。

图1 参考平面为电源层时缓冲器驱动微带线的等效电路模型

图2 虚线左边部分的电源分配网络等效电路模型可表征输出缓冲器的电源供给情况。其中,L1为电压调节模块(Vdd)和去耦电容之间的电感路径,L1=10 nH;L2为去耦电容和芯片I/O单元间的电感路径,L2=5 nH;C为器件I/O单元的去耦电容。对该模型仿真,可得一阶近似结果。

由于该模型中电源的电感阻止高频AC信号通过,即回流必须经过电容返回,图2选择地层作为参考平面,以使流经去耦电容的电流最小。例如,假设NMOS的输出阻抗为5 Ω,信号由高到低跳变,则可计算电路处于下拉状态时流经去耦电容的电流仅为83 mA。

图2 参考平面为地层时缓冲器驱动微带线的等效电路模型

3 仿真结果与分析

分别对图1和图2的两种不同电路结构模型仿真,得到选择不同参考平面时的信号传输质量随去耦电容的变化曲线,如图3所示。由图3可知,相较于电源为参考平面,以地为参考平面时的信号传输质量更高;随着去耦电容容量的增大,仿真得到的两种不同电路结构模型的传输特性均改善较大。

图3 选择不同参考平面时信号完整性随去耦电容的变化

以多驱动芯片封装电路为例,比较本文方法和SPICE仿真结果。图4、图5分别为采用本文方法和SPICE软件仿真得到的驱动端和负载端输出波形。由图4、图5可知,两驱动端波形很接近,且在电压参考位置波形相差15 ps;本文方法比SPICE仿真得到的结果提高了约20 mV;SPICE仿真波形的电压波动为120 mV,而采用本文方法模拟的结果约为110 mV。这是因为SPICE模拟中的封装模型仅包括等效感抗和封装电容,未考虑电地系统与信号系统间的耦合。本文建立的分布式封装模型包含了所有回流路径,而仿真结果验证了本文方法的正确性。

图4 驱动端输出波形

图5 接收端电压波形

4 结 论

随着MCM工作频率的升高和上升沿的缩短,芯片封装中的电源管脚、连接器接口及高频谐振等因素造成MCM电源层阻抗较大,无法满足低阻抗设计要求。本文在电源分配系统模型中增加去耦电容,以减小电源阻抗,并针对不同参考平面和去耦电容容量时的情况分别进行仿真。仿真结果表明:相较于电源为参考平面,以地为参考平面时的信号传输质量更高;随着去耦电容容量的增大,两种不同电路结构模型的传输特性均改善较大;两驱动端波形在电压参考位置波形相差15 ps;SPICE得到的电压波动为120 mV,而本文方法得到的电压波动减小了10 mV,证明了本文方法的正确性。