面向应用型本科教育的FPGA课程教学探索

2019-03-14黄金凤

黄金凤

摘要:该文通过本科教学应用型人才培养目标,针对FPGA这门课程,将理论和实践结合起来,从软件平台和硬件内部结构相结合的方式对课程进行了教学探索。

关键词:应用型人才培养;FPGA;教学探索

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2019)01-0138-03

对于普通高校电子与通信专业的学生,FPGA课程是实践应用性非常强的一门课程,不但涉及数字逻辑电路的相关知识,还涉及现代电子系统设计的相关知识,需要掌握软件平台的设计、硬件内部结构和外围电路的设计,理论教学和实践教学的偏重性,使教学施用于学生产生的结果有所不同,如何使学生既能掌握理论知识,又能将理论知识应用到实践中去,通过实践应用又能更好地巩固理论知识,这个问题关乎到了FPGA课程的教学模式。传统的教学是侧重软件的使用和硬件描述语言的编写这两方面,这种教学模式使学生加强了软件算法编程思维,而忽视了硬件电路设计思维。学生即使很好地掌握了硬件描述语言编写,但对于硬件电路需要考虑的延迟、功耗、电气连接等方面知之甚少,编写的代码有的综合优化过程出问题,有的适配、布局布线过程出问题,有的时序约束不可测,有的电气连接不标准等。所以在很好掌握硬件描述语言编程的同时,学生要结合可编程逻辑器件内部结构来看综合优化过程,适配、布局布线过程是否合理。本论文针对传统教学方式的不足,从软件平台和硬件内部结构相结合的方式对课程进行了教学改革方面的探索。

2 软件平台和硬件内部结构相结合

2.1 软件平台介绍

目前,可编程逻辑器件CPLD/FPGA的供应厂商主要有四家,Altera、Xilinx、Lattice和Actel公司,每一個供应厂商都有各自的软件开发工具,如Altera公司的Quartus II,Xilinx公司的ISE,Actel公司的libero。针对各所学校采购的CPLD/FPGA型号不一样,可以选用相应的软件开发工具进行设计。由于我院采购的是Altera公司的FPGA芯片,所以学生应利用Quartus II软件进行电子系统设计。

Quartus II是进行电子系统设计的集成开发软件,里面集成了设计输入所需的编辑器,设计处理所需的综合器、适配器、布局布线优化器、时序分析器、仿真器、编程下载器等多种软件,通过这些软件相互结合使用,可以实现电子系统设计的自动化。 图1所示的是利用Quartus II软件对PLD进行设计开发的流程图。

第一步,分析当前的设计任务要求,针对电路系统的功能、复杂程度及一些性能参数,选择合适的设计方法,器件资源等准备工作。

第二步,选择适合的设计输入方式,如画电路原理图的方式,用HDL描述电路方式,或者各种方式相互结合。

第三步,对设计的电路系统进行处理,如综合、适配、布局布线优化等操作。

第四步,可以对设计的电路系统进行功能仿真和时序仿真。

第五步,对设计的电路系统进行编程下载及硬件测试。

在设计过程中,如果出现错误,则需要重新回到设计输入阶段,在改正错误或调整电路后重复上述过程。

2.2 FPGA硬件内部结构

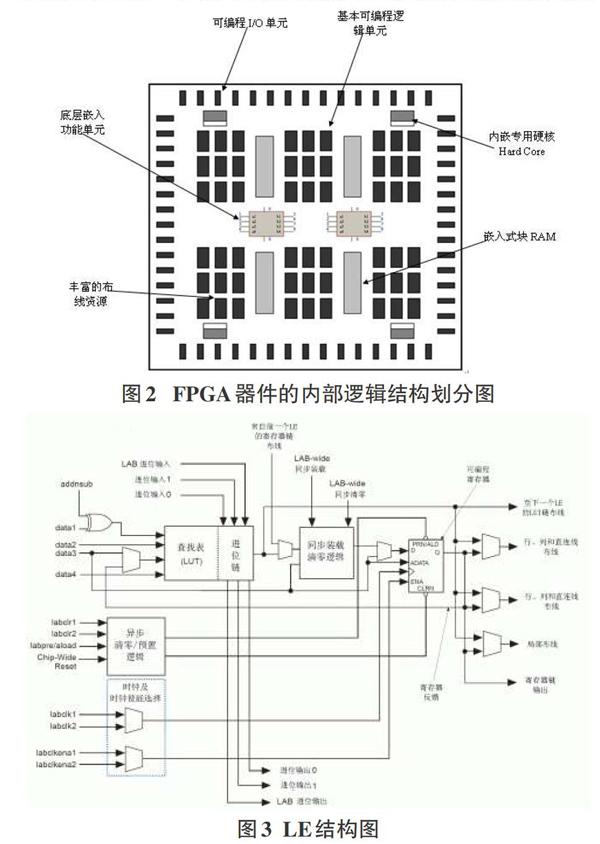

FPGA的内部结构如图2所示,都包含以下3个部分,芯片四周引脚端的可编程I/O单元,内部主体区域的可编程LE,每个单元间的局部可编程连线,有些芯片内部还可嵌入专用存储块RAM,内嵌功能单元和专用硬核等,可编程LE内部结构如图3所示,主要由一个有四个输入端的SRAM 加上D触发器构成。

2.3 采用软件平台和硬件内部结构相结合的方式进行教学

关于通过软件平台进行PLD设计开发过程在前面已经阐述过,第一步通过任务分析进行设计输入,输入方式通常有原理图和HDL文本输入两种,原理图输入方式比较直观,电路内部结构一目了然,然而HDL文本输入方式就比较抽象,和软件编程语言类似,也有语法规则、编程格式等需要注意的,如何正确地编写成可综合、适配的硬件电路结构,需要教师在课堂教学上改进教学模式,以帮助学生更好的理解HDL语言。对于组合逻辑电路,输出信号的变化随着输入信号的改变而改变,且不具有值存储功能,在编写时各种信号相互之间的逻辑关系运算符可以看成是各种逻辑门互相连接,例如赋值语句y = ~s & a | s & b,其中的运算符“~、&、|”可以理解为“非门、与门、或门”。对于时序逻辑电路,输出信号具有值存储功能,在HDL描述时需要加入时钟信号,清零或置位信号,硬件电路结构里需要用到触发器,而触发器需要时钟信号来控制。

第二步,对设计输入文件进行编译,包括综合和适配、布局布线优化,在讲解综合器的作用时,可以通过Quartus II软件中的Netlist Viewers观看综合得到的硬件电路结构。例如三人投票表决器设计实验,用HDL描述电路如下所示:

module bj3(a,b,c,l1,l2); //a,b,表示投票的三人,l1表示通过,l2表示不通过(少于2人投票)

input a,b,c;

output l1,l2;

assign l1=(a&b)|(b&c)|(c&a)|(a&b&c);

assign l2=~l1;

endmodule

HDL描述的电路比较抽象,将抽象的描述语言转化成具有内部结构的电路就是综合器的主要作用,通过Netlist Viewers查看电路内部结构如图2所示:

从图2中可以看出,HDL中的位运算符综合成了电路的各个逻辑门,在软件学习过程中,教师可以通过这种举例的方式直观地让学生感受到,综合器的作用。

第三步,对综合得到的网表文件进行适配,适配器的主要作用是将电路与目标器件FPGA中的可编程单元进行映射,通过FPGA 生成实际的硬件电路。在实际讲授过程中,我们可以通过Quartus II软件中的Chip planner观看适配结果,仍以三人投票表决器设计为例,在Chip planner观察窗口,可以看到实际的FPGA内部硬件结构,如图3所示,FPGA型号选用Cyclone系列的EP1C12Q240C8,图3和图1所示的FPGA 内部结构划分类似,其中该例子中的输入、输出管脚在可编程I/O单元区域用深棕色标出,三人投票表决器逻辑值用逻辑单元中的查找表存储,占用的LE单元用深蓝色标出。通过放大按钮,可以清楚地看到电路资源分配情况,如图4和图5 所示。

从适配后电路资源分配情况,可以更清楚地掌握FPGA内部结构,从而更好地理解可编程逻辑器件的编程原理。

通过软件平台和硬件内部结构相结合的方式进行教学,学生更容易理解硬件描述语言的本质,综合器和适配器真正的作用,他们都是为了配合可编程逻辑器件内部结构而使用的工具。

3 结语

FPGA课程是实践应用性非常强的一门课程,虽然大部分工作都是在软件开发设计这块,但是如果对可编程逻辑器件内部结构不了解,数字电路基本原理不清楚,软件开发设计这块就会遇到很多问题。如何有效地将软件平台和硬件电路结构结合起来,使学生高屋建瓴地进行电子系统设计,需要教师对于这门课程的教学不断的探索、改进。

参考文献

[1] 李兆光.数字电子技术课程中FPGA技术教学内容的改革[J].山西电子技术,2015(2):23-24,31

[2] 高一沅.应用型本科专业FPGA相关课程教学模式的探讨[J].湖北科技学院学报.2016(4):84-86

[3]庞前娟.应用型本科EDA技术教学改革的研究[J].大学教育,2015(7):125-126

[4] 郑利浩,王荃,等. FPGA数字逻辑设计教程[M].电子工业出版社,2010.

[5] 吴厚航.深入浅出玩转FPGA[M],北京航空航天大学出版社,2010.