FPGA控制DDS与AGC的精密信号发生系统研究

2019-02-22王振瑜吴校生叔晟竹

王振瑜,吴校生,叔晟竹

(上海交通大学电子信息与电气工程学院微纳电子学系,微米纳米加工技术国家级重点实验室,上海 200240)

0 引言

信号发生源在生产和研发过程中能够提供信号驱动、参考及运算等功能,具有重要意义[1]。目前广泛使用模拟信号源进行驱动,模拟信号源便于集成,操作简单,且频谱纯度较高,使用比较广泛。但是在自动化控制方面,信号发生源生成的驱动信号较难根据系统需求实时调整频率和幅值,或者调整精度较低,频率范围较小,存在高分辨率和快速转换速度之间的矛盾[2]。

现场可编程逻辑门阵列(FPGA)在数字信号处理、逻辑运算、高速信号收发等方面具有强大的能力,能够对外设电路进行精确的控制,目前在很多系统中已经作为主芯片应用[3]。基于FPGA的特点,本文设计了FPGA控制下采用直接数字合成(DDS)和自动增益控制(AGC)技术的信号发生系统。DDS是采用直接合成所需波形的一种新的频率合成技术,与传统的产生模拟波形的方法相比,DDS具有频率分辨率高、频率转换速率快、稳定度较高等优点[4]。AGC分成增益受控放大电路和控制电压形成电路2部分,通过输出反馈改变增益控制电压,能够实现信号的幅值可调[5]。

本文基于FPGA的控制,结合DDS技术和AGC技术设计了精密信号发生系统。系统包括FPGA的软件控制部分和驱动的硬件电路部分,2部分结合设计实现信号发生以及信号频率、幅值的变化。将设计的信号发生系统用以器件驱动,能够得到器件有关工作特性。本文为基于FPGA的频率及幅值精确可调的信号发生系统设计提供了理论参考。

1 信号发生系统整体框架

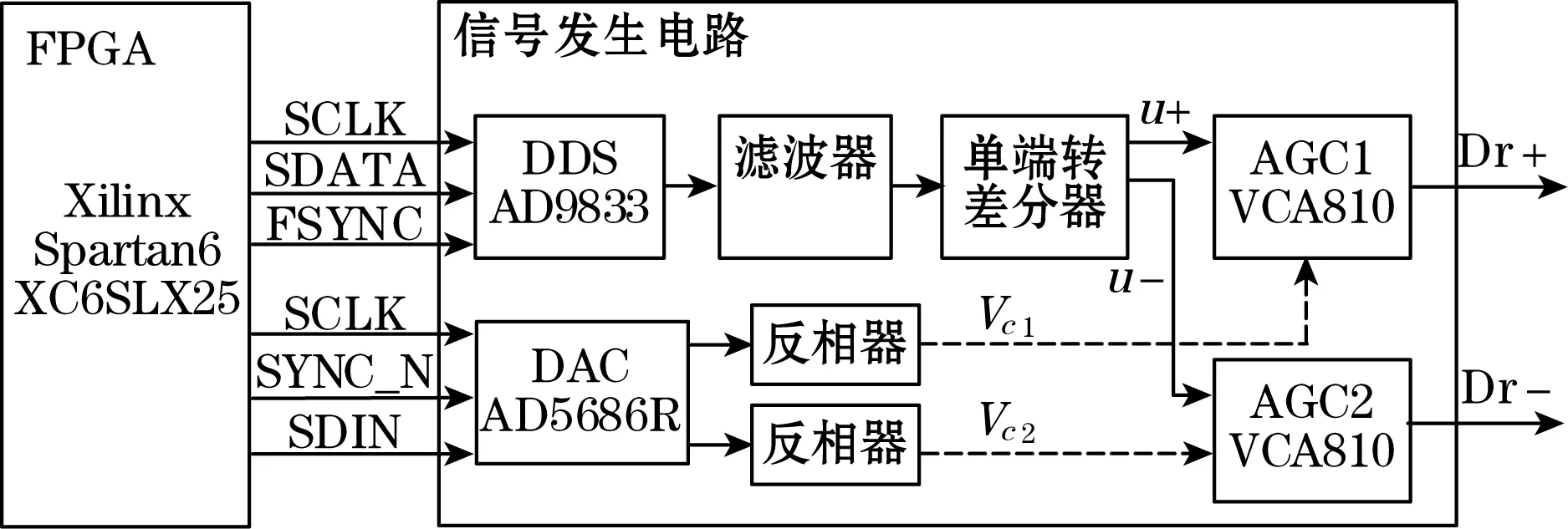

基于FPGA及DDS和AGC技术的信号发生系统整体框架如图1所示,整个信号发生系统分为电源模块、DDS模块、单端转差分模块、AGC模块和DAC模块等几个部分。通过FPGA对信号发生系统中DDS模块和数模转换器(DAC)模块的控制,能够控制发生信号的波形、频率以及幅值。信号发生系统中各模块相互独立,根据不同需求接入对应的模块,能够满足不同系统的信号需求,系统框图如图1所示。

图1 FPGA控制DDS和AGC的信号发生系统框图

在FPGA部分,本文使用Spartan6系列FPGA芯片,通过芯片向电路系统中的DDS模块和DAC模块提供控制时钟、数据读写、同步异步等命令,使DDS模块产生频率可调的正弦电压信号及在DAC上产生AGC增益控制电压模拟信号。系统电路主要包括DDS、DAC、AGC等模块。其中DDS模块主要通过DDS芯片AD9833产生波形信号,由FPGA通过控制信号改变DDS的频率控制字及输出波形。DAC模块主要是通过DAC芯片AD5686R产生AGC增益控制电压模拟信号,其中DAC芯片能够输出4路波形,由FPGA通过改变控制命令使DAC产生后续AGC需要的增益控制电压模拟信号,从而实现波形幅值可调。

2 DDS和AGC模块工作原理

根据DDS芯片模块的控制信号时序要求,本文设计完成FPGA的DDS信号控制算法。FPGA控制算法采用同步时钟控制,对系统时钟进行分频产生DDS芯片的工作时钟fclk。同时,在FPGA内部算法中利用分频后产生的时钟fclk对信号处理,数据传输提供频率参考。FPGA对DDS模块控制的命令根据DDS芯片的工作时序决定。在同步信号下降沿的后16个时钟周期内,DDS芯片读入16位二进制数作为控制命令,决定DDS芯片的工作方式。DDS的输出满足式(1):

(1)

式中:fout为DDS输出信号频率,Hz;fDCLK为外部晶振提供数字时钟,Hz;M为频率控制字;N为芯片相位累加器位数。

对于采用的AD9833芯片而言,其内部包括一个28位的相位累加器,即N=28[6]。因此,M的取值范围是0~228-1。fDCLK由外部晶振提供,输出信号的频率fout的大小不会超过外部晶振产生的时钟频率。

FPGA不仅对输出信号的频率进行控制,还对信号的幅值进行控制。FPGA通过控制DAC的输出电平控制AGC的增益,实现幅值的改变。根据DAC芯片的时序要求,本文完成对DAC的控制算法。本文采用的DAC芯片是AD5686R,这是一款16位的数模转换芯片,可以4通道同时输出波形。根据AD5686R的时序要求,在同步信号下降沿之后的24个时钟周期内,FPGA对DAC芯片输出24位串行数据,其中高4位为命令位,之后4位为地址位,低16位为数字位[7]。DAC的输出满足式(2):

(2)

式中:VOUT为DAC输出模拟信号,V;VREF为DAC参考电压,V;D为DAC输入数字量;N为DAC的位数。

式中N根据选用的DAC芯片而定,本文选用的DAC芯片为16位,故N=16。D为16位数据,DAC根据D的大小决定输出的模拟信号的值。

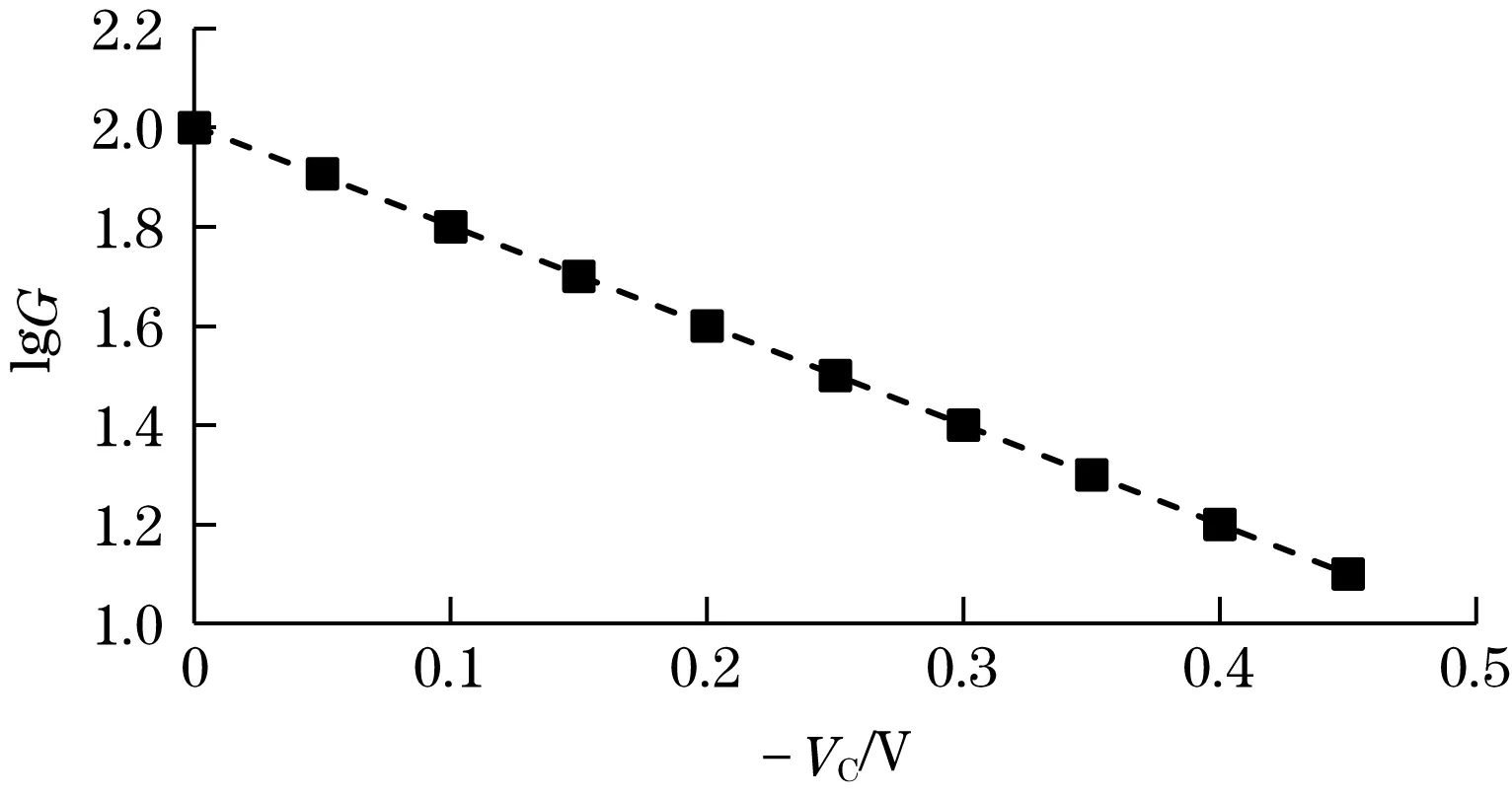

根据系统框图1可知,DAC产生的信号经过反相器成为AGC的增益控制信号Vc,根据AGC控制芯片VCA810数据手册可知,Vc值的范围在0~-2 V[8]。其增益的范围G满足式(3):

G=10-2(Vc+1)

(3)

式中:G为AGC增益倍数;Vc为AGC的增益控制电压,V。

由式(3)可知,增益范围为0.01~100。AGC的增益倍数与增益控制电压之间是指数的关系。

3 FPGA控制命令与波形仿真

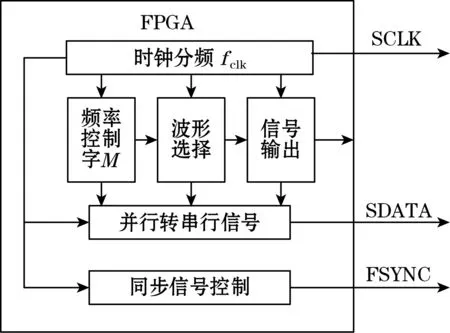

FPGA根据对有关器件工作状态的检测结果或预设的控制命令,判断对DDS频率控制字M是否进行增减,决定输出信号的频率。根据AD9833的工作时序及命令格式,FPGA在确定了DDS的输出频率后,需要继续控制其输出特定的波形,AD9833根据得到的命令可以输出正弦波、方波、三角波等波形。通过不断改变频率控制字的值,实现波形的变频效果。FPGA对DDS的控制命令流程如图2所示。

图2 FPGA对DDS的控制命令流程

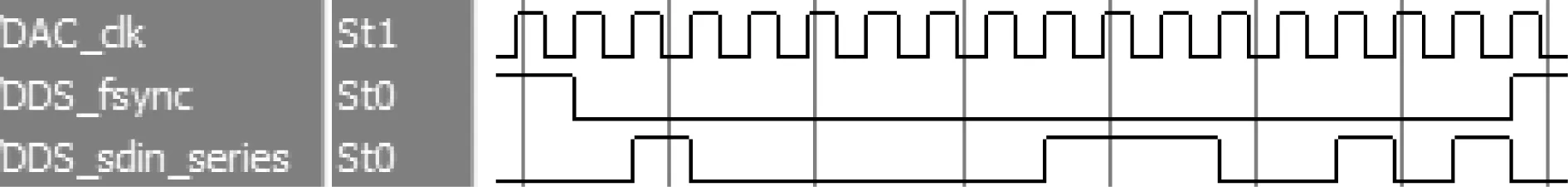

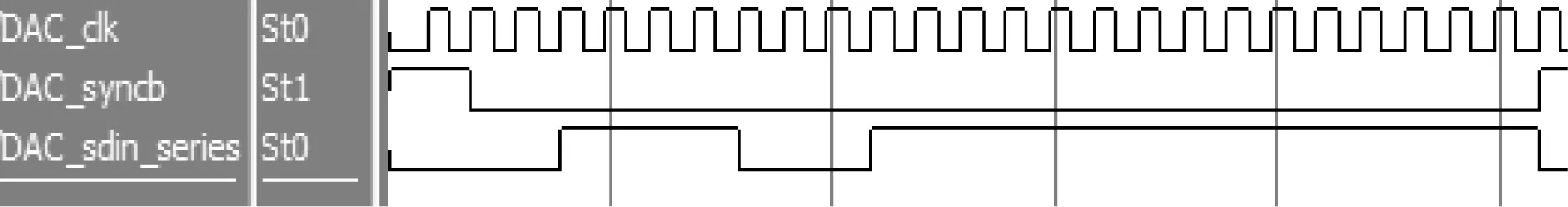

根据设计方案,FPGA对DDS模块的控制采用Verilog硬件描述语言编程设计,在ISE环境下进行编程、仿真和调试。根据DDS芯片的工作时序,仅当FSYNC处于低电平时,才可将数据传输至DDS芯片。SCLK为同步时钟,串行数据SDATA在FSYNC变为低电平后,串行数据即会在16个时钟脉冲的SCLK下降沿移入器件的输入移位寄存器。仿真波形如图3所示。

图3 FPGA对DDS控制信号仿真波形

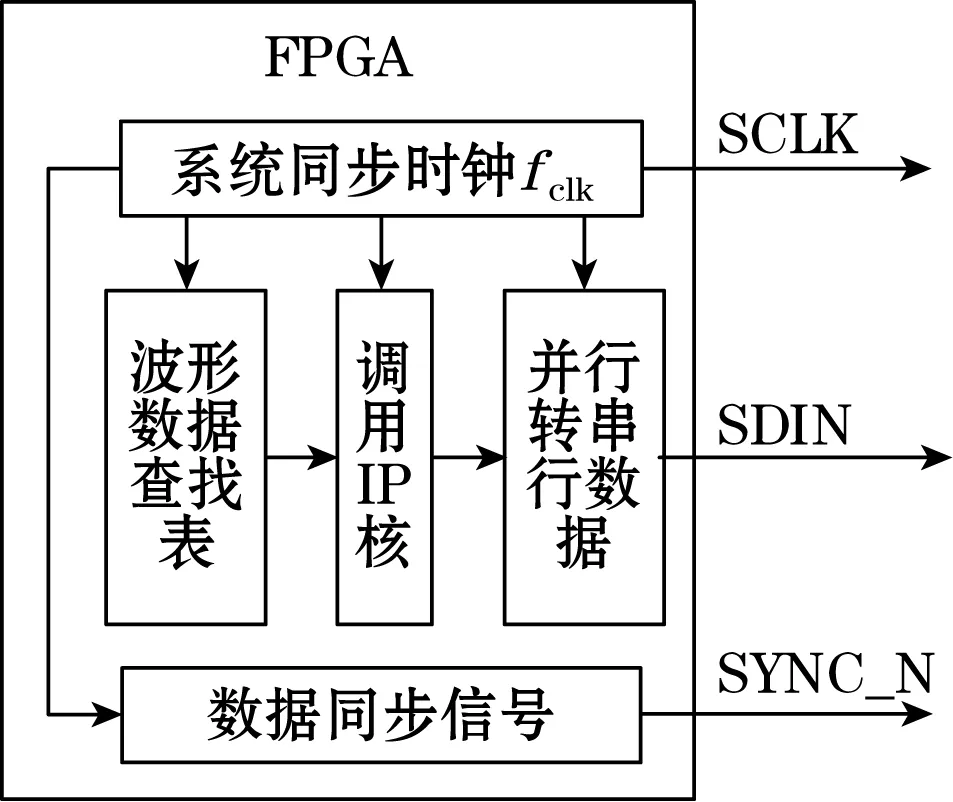

在控制AGC方面,FPGA通过查找表的方法,将D值通过一定的顺序存放到IP核中,通过检测部分对器件的工作状态进行判断或根据预设控制命令,决定调用IP核中不同地址储存的D值,从而控制DAC的输出。在对DAC进行控制时,FPGA使用与控制DDS相同的时钟参考fclk,使得各部分的控制在同步时钟下进行。FPGA采用同步时钟有利于各个控制部分能够同时工作,同时不易产生延迟与误码。FPGA对DAC的控制命令流程如图4所示。

图4 FPGA对DAC的控制命令流程

根据设计方案,FPGA对AGC模块的控制同样采用Verilog硬件描述语言编程设计。FPGA通过控制DAC的输出电平控制AGC的增益,实现幅值的改变。根据DAC芯片的工作时序,仅当SYNC_N处于低电平时,才可将数据传输至DAC芯片。SCLK为同步时钟,串行数据SDIN在SYNC_N变为低电平后,串行数据即会在24个时钟脉冲的SCLK下降沿移入器件的输入移位寄存器,仿真波形如图5所示。

图5 FPGA对DDS控制信号仿真波形

4 信号发生系统硬件设计

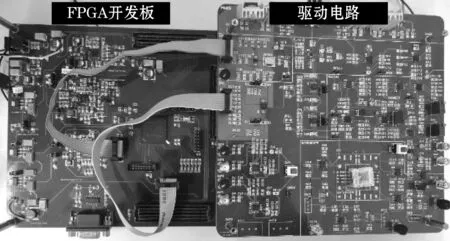

根据系统设计的框图,本文对基于FPGA的信号发生系统进行了硬件设计,如图6所示。驱动电路系统主要包括FPGA开发板和驱动电路2部分。2部分分别供电,但是进行共地处理,FPGA通过SPI接口与驱动电路的DDS和DAC部分进行通信控制。信号发生系统各部分联合工作,也可根据实际需求独立工作,能够满足不同驱动方式的需求。

图6 FPGA控制的信号发生系统

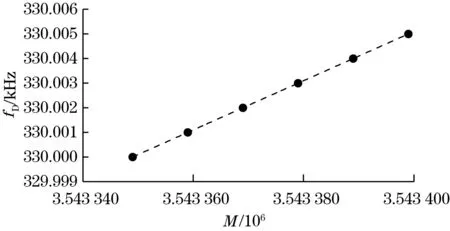

信号发生系统的分辨率和稳定性是衡量驱动电路性能的2个重要指标。本文对设计的信号发生系统的频率分辨率和幅值控制情况进行了测试,测试结果如图7所示。DDS的信号输出频率与频率控制字M之间是线性关系。当ΔM=10时,输出信号的频率步长为1 Hz,如图7(a)所示。DDS的分辨率可达0.1 Hz。由于AGC的增益倍数与增益控制电压之间是指数的关系,对增益倍数G取对数,显示其与增益控制电压Vc是线性关系,如图7(b)所示。

(a)

(b)图7 信号发生系统分辨率测试图

通过实验分析,驱动电路系统具有非常精确的分辨率和稳定性。FPGA能够准确根据频率控制字M控制DDS的频率输出和AGC的增益大小。

5 信号发生系统输出测试

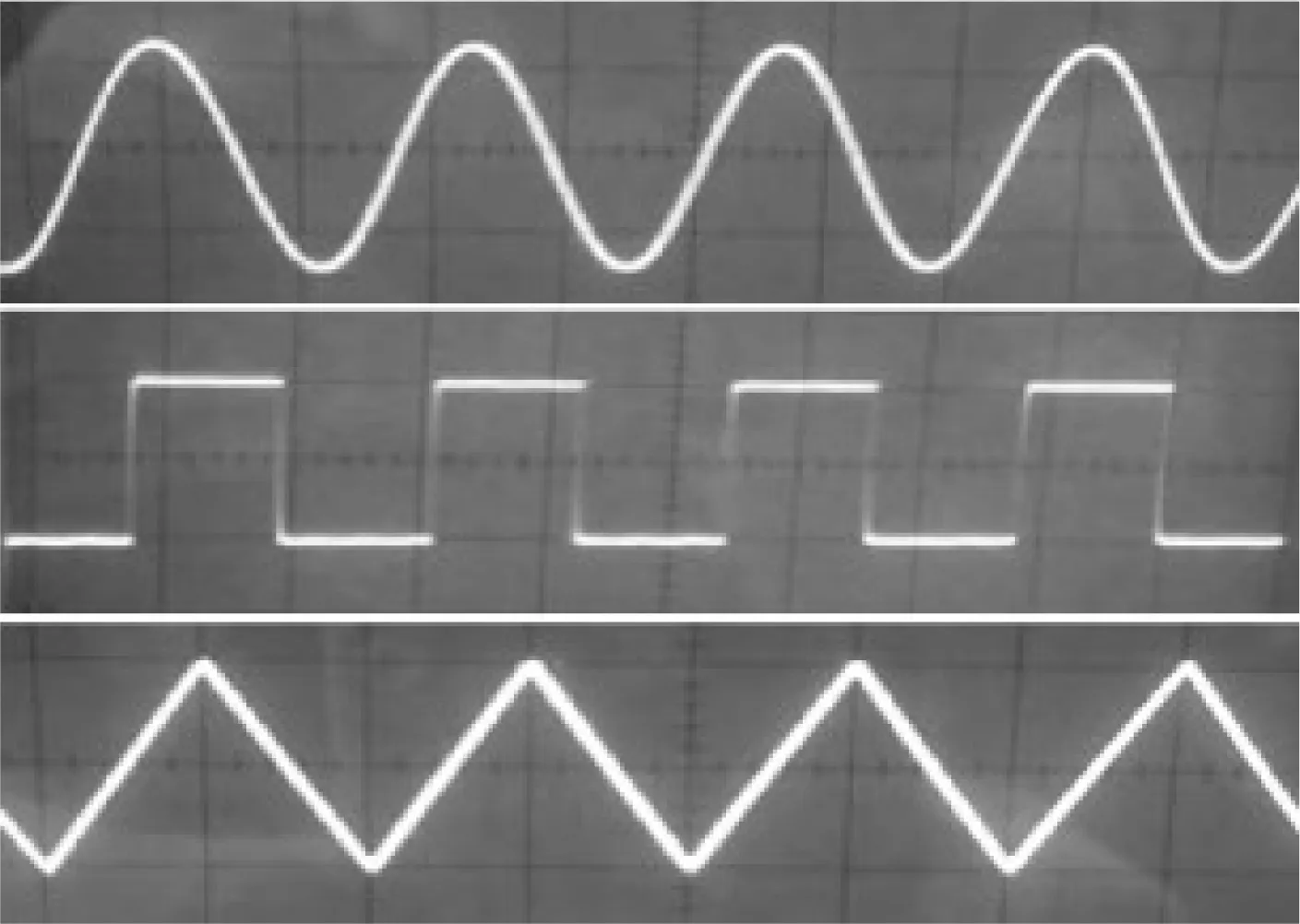

本文设计的基于FPGA及DDS和AGC技术的精密信号发生系统具有较高的信号频率分辨率及波形稳定性,同时信号发生系统能够输出正弦波、方波和三角波等多种波形。利用示波器观察信号发生系统的各输出波形,得到信号发生系统的波形输出情况,如图8所示。

图8 信号发生系统波形输出情况

信号发生系统输出波形稳定,频率分辨率高,幅值精确可调。信号发生系统频率分辨率可达0.1 Hz,幅值分辨率也可以达到0.1 V,能够满足MEMS谐振器的驱动需求。如图9所示,系统能够输出频率和幅值可调的正弦信号对器件进行驱动控制。

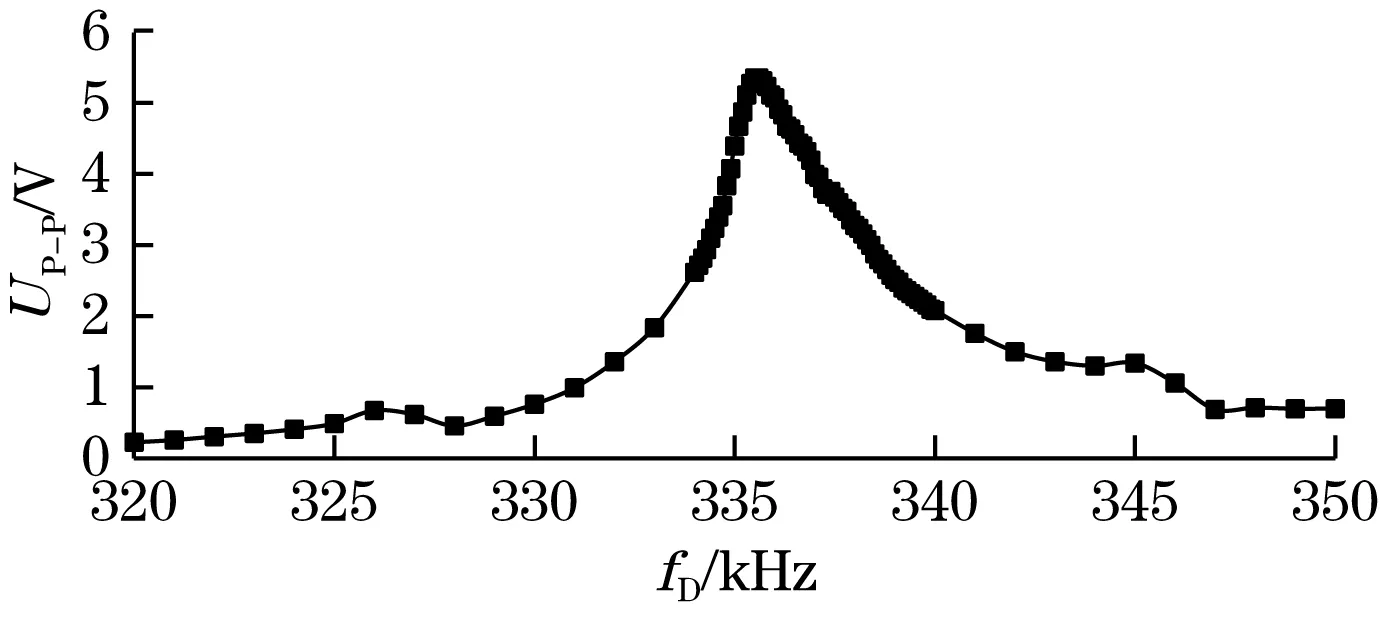

利用设计的信号发生系统,对PZT压电式谐振器进行驱动实验测试,得到谐振器在不同频率驱动信号下的振动情况。根据PZT压电式谐振器的驱动原理[9],在谐振器上表面施加交流驱动信号,在不同频率的驱动信号作用下,PZT压电式谐振器在不同驱动信号频率fD下表现出不同的振动应电压峰值UP-P,如图10所示。从扫频测试中看出,在单边驱动的情况下,PZT压电式谐振器在正常室温的环境中,共振频率点位于335~336 kHz之间,实测得335.570 kHz。

图10 压电谐振器扫频测试波形

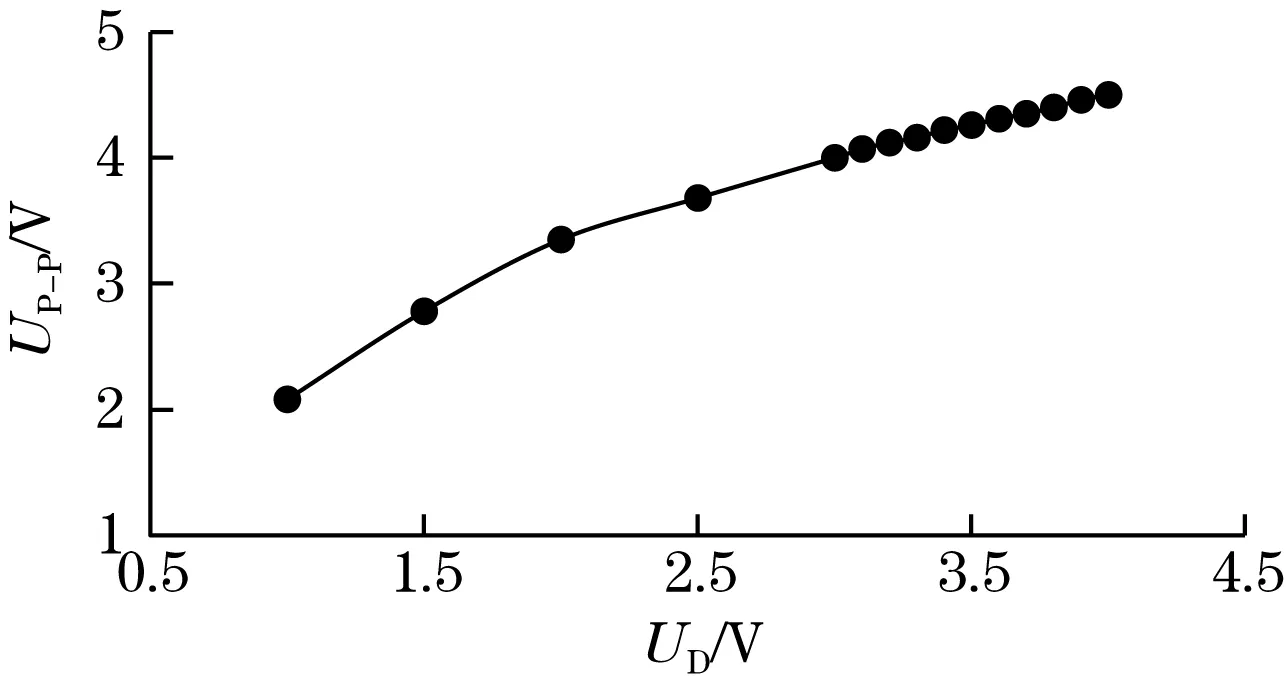

由于信号发生系统具有较高的频率分辨率,因此在扫频测试时能够调整系统输出信号的频率步长,在谐振器谐振点位置减小输出波形频率增量,增大采样数量,能够更准确得到器件的谐振点频率。信号发生系统的输出波形幅值精确可调,改变驱动信号的幅值,观察谐振器的振动情况。如图11所示,系统能够输出不同幅值步长的驱动信号,得到谐振器在不同幅值驱动信号下的振动感应电压峰值UP-P。

图11 不同幅值驱动信号下的感应电压图

6 结束语

本文基于FPGA设计了一种信号发生系统,该系统运用DDS和AGC技术,并由FPGA进行控制,实现驱动信号的频率和幅值精确可调。FPGA采用同步时钟控制,通过改变频率控制字实现对DDS变频控制,同时改变DAC的输出数字量,从而改变AGC的增益控制电压,实现对AGC的调幅控制。驱动系统输出信号的频率分辨率能够达到0.1 Hz,能够输出正弦波、方波和三角波等多种波形,输出波形稳定性强,幅值变化步长可达0.1 V。本文设计的精密可调的信号发生系统基于FPGA进行控制,能够方便增减频率控制字长以及幅值增益倍数,实现了信号源的频率高分辨率与幅值精确可调。本文将设计的信号发生系统对PZT压电谐振器进行了驱动测试实验,能够得到PZT压电谐振器的谐振特性,可以为压电式谐振器工作振动模态的正确激励提供参考,具有实际应用价值。