面向商用APSoC器件的双核锁步机制①

2019-02-06孙越伍攀峰马宗峰李杰

孙越 伍攀峰 马宗峰 李杰

摘 要:商业卫星的迅速发展,具备灵活性和可配置性的商用APSoC(All Programmable System-on-Chip)器件成为提高卫星性能、降低成本的重要途径之一。具备多种优点的APSoC器件受到国内外商业卫星领域广泛关注。但APSoC器件抗辐照能力较低。因此,针对单粒子翻转引发的软错误,本文提出面向商用APSoC器件的双核锁步机制,能够检测单粒子效应导致的软错误并纠正,提高APSoC应对单粒子翻转引发的软错误能力。

关键词:APSoC 双核锁步机制 Checker模块 检查点 回卷恢复

中图分类号:TN47 文献标识码:A 文章编号:1674-098X(2019)09(b)-0009-02

近年来,已开发出基于多核架构的新嵌入式片上系统来满足高性能处理器要求,将FPGA与嵌入式处理器相结合架构称为APSoC[1]。APSoC是工业级或商业级器件,与宇航级器件相比,其抗辐照能力较低。其中对于低轨空间辐射效应中的总剂量效应,在文献[2]中经试验证明APSoC中的Zynq 7000 XC7Z020和Zynq UltraScale+ XCZU9EG在105MeV下的总剂量分别为110.4×109p/cm2、120.0×109p/cm2,相当于10.0krad(Si)、10.9krad(Si),该总剂量能够适用于许多低轨卫星任务。另外,随着集成电路工艺尺寸的不断缩减,由单粒子效应引起的软错误所需的能量阈值在不断降低,因此发生软错误的几率也在不断提高,软错误已成为小卫星技术甚至空间技术领域亟待解决的关键问题。

面向商业航天对APSoC器件的应用需求,本文主要从双核处理器的抗软错误防护入手,研究一种适合APSoC的双核锁步容错机制,该机制可以防止系统发生功能中断以及检测单粒子效应导致的软错误并纠正。

1 双核锁步机制

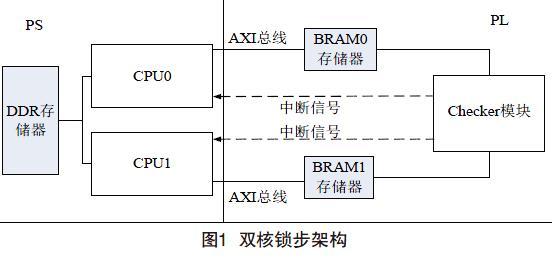

双核锁步(简称DCLS)机制是在两个相同的处理器中同时运行相同的应用程序,由检查器模块对比两个CPU应用程序的执行输出,在输出结果一致的情况下,由检查器模块产生中断,将两个CPU当前状态以检查点文件的形式保存到存储器上。在输出结果不一致的情况下,由检查器模块产生中断,两个CPU处理器调取最近一次保存的检查点文件实施回卷以恢复系统。由此可以看出,在软错误发生后,双核锁步机制能够用于错误纠正,将系统恢复到安全状态。

1.1 架构

本文提出双核锁步机制是在APSoC器件中的一款Zynq UltraScale+上设计和实现的,该方法通过一些调整,便可以扩展到不同的APSoC器件中使用。双核锁步机制架构设计图1所示,每个CPU都连接到其专用BRAM存储器,所有应用程序数据和处理器的检查点文件都存储在BRAM中。处理器与外部共享DDR存储器连接,该存储器存储两个CPU的程序指令,此外,DDR还作为检查点的备用存储器。Checker模块是一个负责验证处理器一致性的模块,它与两个BRAM存储器连接以访问两个CPU的输出,并产生中断信号以控制CPU执行检查点或者回卷恢复操作。

1.2 Checker模块

在双核锁步机制中,Checker模块用IP核实现,采用Verilog语言设计,它负责验证处理器一致性。在本设计中采用应用程序输出应用签名的方法进行比较,该方法在应用程序上附加代码,在验证点之前在应用程序上计算签名,虽然提高了应用程序复杂度,但能够降低Checker模块进行数据对比的时间。这个签名可以是所有元素的总和、XOR掩码、校验等方法来实现。

关于处理器寄存器的验证,要考虑以下问题:(1)本文主要使用通用寄存器R0~R12、堆栈指针(SP)、链接寄存器(LR); 和程序计数器(PC)。(2)在程序执行开始时,寄存器必须执行初始化程序,使两个处理器的寄存器状态保持一致。

2.3 检查点和回卷操作

检查点是一种将处理器一致状态保存在内存中的操作,回卷操作是通过恢复先前的状态从错误中恢复系统。在双核锁步机制中,执行检查点操作时将寄存器状态存储在BRAM和DDR存储器中。在回卷操作中,从存储器读取检查点文件。执行回卷并且系统仍然出现错误,则执行序列下一个回卷级别。回卷级别如下:

1、第一级回卷从BRAM存储器读取检查点文件以恢复系统。

2、第二级回卷从DDR内存读取检查点文件以恢复系统。

3、如果上述两个级别回卷都没有效果,则重新启动应用程序以恢复系统。

如果在应用所有回卷级别后,仍无法成功恢复系统,则硬件系统看门狗会由于长时间没有“喂狗”产生看门狗复位信号,系统重新运行。

3 总结

锁步技術是一种错误检测机制,可以保持多个CPU,在相同时钟周期内执行相同的指令。在APSoC器件上使用双核锁步机制(DCLS)作为容错解决方案,系统能在不间断处理和不损失数据的情况下恢复正常运行,以提高嵌入APSoC的硬核处理器的可靠性,而且本文提出的双核锁步机制可以通过简单调整扩展到不同的APSoC器件中使用。该机制的提出为商用航天选用高性能、低成本的处理器提供了一种方案思路。

参考文献

[1] ?dria Barros de Oliveira, Lucas Antunes Tambara, Fernanda Lima Kastensmidt. Exploring Performance Overhead Versus Soft Error Detection in Lockstep Dual-Core ARM Cortex-A9 Processor Embedded into Xilinx Zynq APSoC. Lecture Notes in Computer Science, p.189-201, 2017.

[2] David M. Hiemstra, Valeri Kirischian and Jakub Brelski. Single Event Upset Characteriza- tion of the Zynq-7000 ARM CortexTM-A9 Processor Unit Using Proton Irradiation. 2015.