基于JESD204B协议的多路同步应用

2018-12-29胡瑾贤李春来

钟 文,顾 军,胡瑾贤,李春来

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

多通道数据同步传输是大带宽电子战数字波束合成系统研发的关键之一。下行采样通道输出延迟和数据传输技术中传输延迟的确定性设计是保持下行数据同步采集、相位差保持稳定的核心技术[1]。2011年JEDEC针对数据转换器与逻辑器件之间的JESD204协议B版本,此版本将串行链路数据率提高到12.5 Gbps,并且使其能够满足确定性传输延迟的需求。在JESD204B中引入了3个子类[2]。子类0向后兼容JESD204 A标准;子类1引入外部同步参考信号SYSREF,实现确定性延迟;子类2将同频触发信号SYNC~作为系统的时序基准。目前JESD204B协议多用于逻辑器件与转换器之间的数据同步,本文将协议的子类1引入现场可编程门阵列(FPGA)间的多通道数据同步传输中,通过与传统数据同步传输方案做对比,详细分析同步设计的关键要点,并对SYNC信号的传输进行改进,节约系统走线资源,提高FPGA收发器利用率,最后给出验证结果。

1 片间JESD204B协议的优势

对于电子战数字波束合成系统而言,数据量庞大,所以片间数据一般采用Aurora协议或基于高速串行收发器的自定义协议完成。以Aurora协议为例,典型的片间传输框图如图1所示。此类传输方案存在2个不可避免的缺点。算法模块(例如数字波束合成)工作在时钟域CLK_A,该时钟域一般与模数转换器(ADC)的接收时钟域同源,但是Aurora协议工作在时钟域CLK_B,该时钟域一般由协议的编码类型和线速率决定。这造成了算法模块与Aurora协议间需要采用异步先进先出(FIFO)去进行时钟域的划分,异步FIFO带来的结果就是每次FPGA上电后传输延迟的不确定以及群延时的增加。

图1 典型片间传输系统

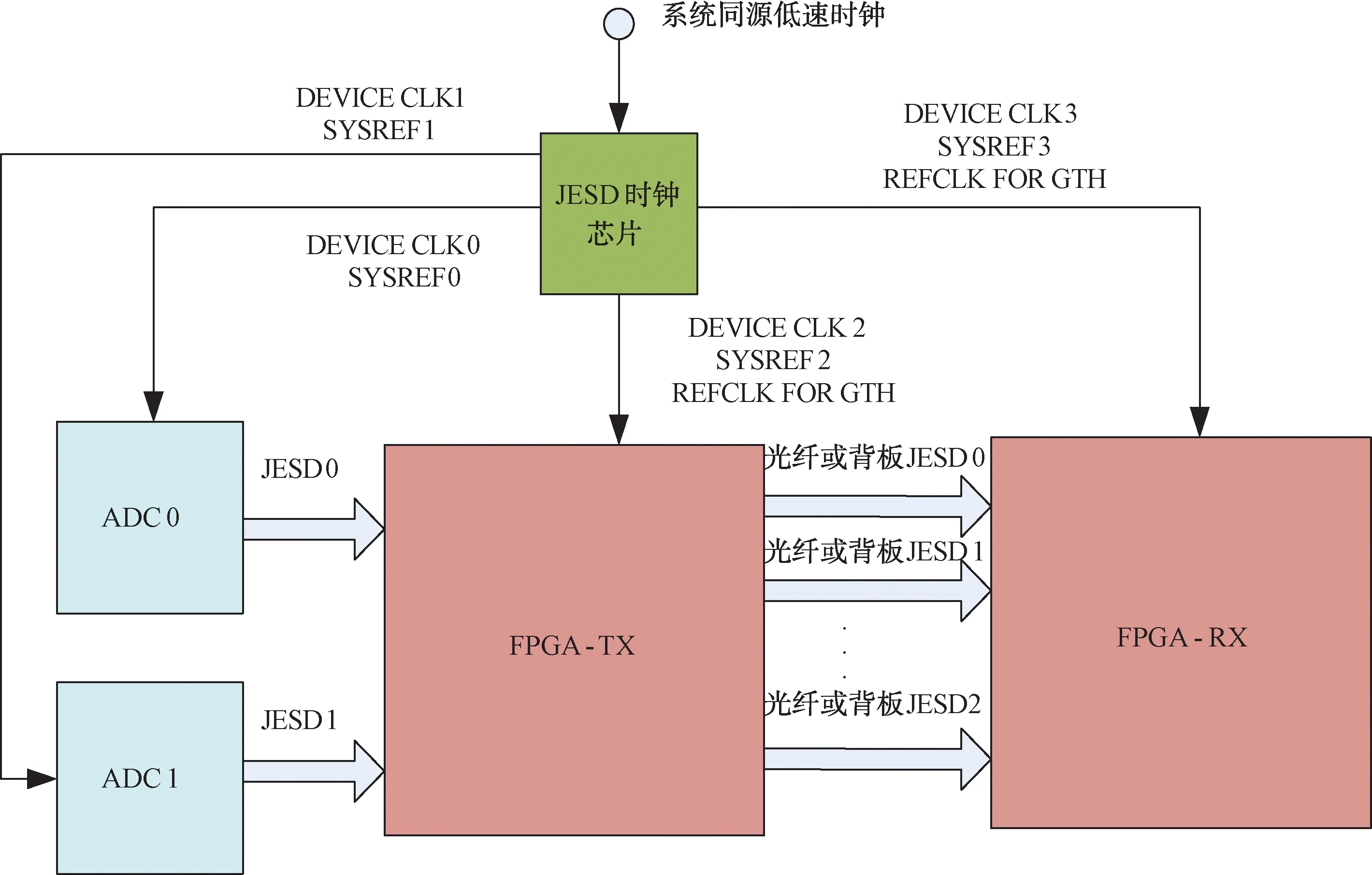

JESD204B协议的引入可以同时解决上述2个问题。首先JESD204B协议具有提供传输链路确定性延迟的功能,其次它延迟相对较低。结合ADC与FPGA间JESD204B协议的运用,能够使得ADC采样的时钟域、算法模块时钟域、数据传输模块时钟域完成同源与统一,简化了FPGA的时钟域划分,规避了数据传输模块带来的延迟不确定性,降低了系统的群延时。系统的同步算法只需要补偿硬线带来的延迟差异即可,从很大程度上减轻了系统同步负担。基本设计框图如图2所示。

图2 基于JESD204协议的同步设计

2 JESD204B协议的同步要求及改进

在FPGA间实现JESD204B协议的同步传输可以分解为4项基本要求[3]:

(1) SYSREF信号

对于实现系统的固定延迟以及同步而言,SYSREF信号是最为重要的,它用于完成本地多帧时钟(LMFC)的对齐。针对SYSREF信号提出2个要求:其相对于器件时钟满足建立及保持时间要求,并且以一个适当的频率运行,也可配置为单个脉冲,取消频率约束。

在传输系统的设计之初首先确定SYSREF的频率(如采用SYSREF周期模式)。主要要求是SYSREF信号必须以1个等于或者整数分频本地多帧时钟(LMFC)的频率运行,即:

(1)

式中:fbitrate为高速串行收发器的接口速率;F为每帧8位的字节数;K为每个多帧的帧数;n为任意正整数。

其次系统设计需要让SYSREF满足核时钟建立保持时间的要求。FPGA片外时钟芯片一般会设置为SYSREF信号与其提供的器件时钟(device clk)或者参考时钟(refclk)同步,也就是输出边沿对齐。此时下降沿采样能够获得最好的时序特性。考虑到实际印制电路板(PCB)布线带来的延迟差异,对进入FPGA IO的相关信号做如下时序约束,保证在1 ns的时间差内对齐SYSREF信号和refclk信号:

set_input_delay -clock jesd204_0_refclk -max 0.5 [get_ports *x_sysref]

set_input_delay -clock jesd204_0_refclk -min -0.5 [get_ports *x_sysref]

(2) 多帧周期

选择多帧周期实际就是设置合适链路延迟,使得延迟满足协议所需的固定延迟要求。协议的总延迟T可以表述为:

T=NTLMFC-TTXLMFC+TRXLMFC

(2)

式中:TTXLMFC为发送端SYSREF到TLMFC的固定延迟;TRXLMFC为接收端SYSREF到TLMFC的固定延迟;N为整数;TLMFC为LMFC周期。

为保证每次上电时延迟固定,首先最大传输延迟必须满足:

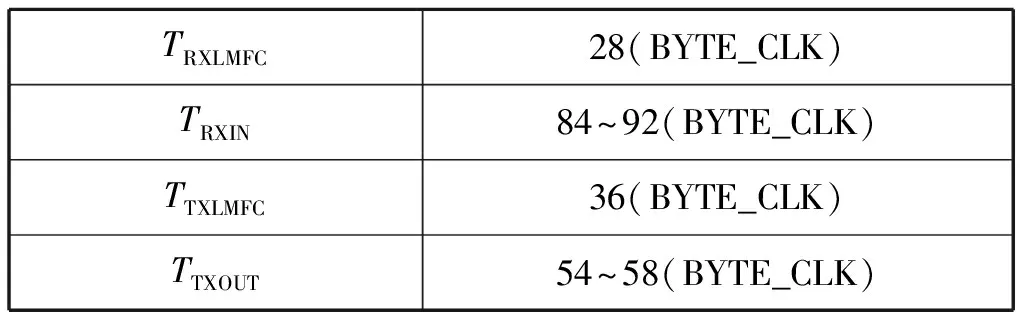

TTXOUT(MAX)+TWIRE(MAX)+TRXIN(MAX) (3) 式中:TTXOUT为发送端LMFC到输出串行数据间的延迟;TWIRE为传输线路上的延迟;TRXIN为接收端LMFC到并行数据数据输出的接口的延迟。 其次,最小延迟须满足: TTXOUT(MIN)+TWIRE(MIN)+TRXIN(MIN)>T (4) 下面以Xilinx FPGA 内的型号(GTH)为例,计算LMFC周期和相应N的值,GTH相关参数如表1所示,GTX、GTP参数请参考文献[2]。 将以上参数以及式(2)代入式(3)、(4),并且假设TWIRE(MIN)、TWIRE(MAX)均为0,得到如下表达式: (5) 进一步推导得: (6) 由上式得到当N=1,TLMFC=FK=128时,满足固定延迟的要求,且余量足够。 (3) 缓冲器释放点 弹性缓冲器是实现确定性延迟的关键部件[5]。它是通过在串行化数据从发送端行进至接收端的过程中补偿其传播延迟变化来做到这一点的。正确的释放点是一个可针对延迟变化提供充足余量的点,错误的释放点会产生一个LMFC周期的延迟变化。 选择一个正确的释放点需要了解数据在弹性缓冲器上的平均到达时间(对于一个LMFC边沿)以及所有器件的总预期延迟的变化。利用该信息即可确定一个LMFC周期内的无效点释放区域。最终应该保证需要同步各个发送端的数据均在释放点到来之前到达接收器件内的缓冲器。下面用1幅时序图来说明(如图3所示),从图3可以明显看出,发送路径2具有较长的路由距离,导致传输延迟较长。JESD204B IP的缓冲释放点调整是通过修改SYSREF延迟(DELAY)参数来完成的,延迟SYSREF实际上等同于延迟LMFC的出现时间。从图3中可以看出此时选择默认值0比较合适,左右都有一定的余量。若LMFC出现在条状无效区域则2路的同步结果有可能存在1个LMFC的周期延迟。 (4) SYNC信号的要求及传输改进 JESD204B 协议对SYNC的定时要求只在一些特殊的场合适用[3]。对于FPGA间的应用SYNC信号并不起到定时作用,当接收端收到连续K28.5后,会拉高SYNC信号通知接收端启动发送ILA序列。 通常情况该信号都是由低压差分信号(LVDS)差分线完成传输,在传输规模较大、发送端板卡及通道数较多情况下,需要大量的差分线完成SYNC的信号传输。但是实际应用场景对体积和走线规模有严格要求,比如天线阵面集成模块和处理机箱间,所以需要对SYNC信号的传输进行改进。正常模式下FPGA内JESD204B协议的发送端只利用收发器的发送部分完成数据传输,接收端只利用收发器的接收端,这也造成了收发器资源的浪费。这里采用收发器共享技术将某个通道JESD204B协议的反向通道的收发器以自定义协议报文的方式传送SYNC信号,同时还能够传送反向控制报文,控制发送端的工作模式与运行状态,具体示意图如图4所示。 图3 确定缓冲释放点的LMFC有效区域 图4 JESD204B SYNC信号传输改进方案 该方案在不增加FPGA功耗的同时解决了多路SYNC传输的需求,提高了FPGA收发器的利用率。 测试的目标FPGA芯片选择2片Xilinx公司的XC7V690T,基本设计环境如下:片间同步系统由6个JESD204B协议发送和接收通道组成;每个通道由8个子通道(LANE)组成;每个LANE线速率10.24 Gbps;多帧周期值为128(F=4,K=32),SYSREF设置为周期模式,频率为8 MHz;选择高度锁相环(QPLL)作为收发器的时钟源降低时钟抖动带来的影响。 (1) 片内多通道的同步实验 JESD204B通道的所有发送端位于同一片发送FPGA中,接收端通道位于接收FPGA中,在发送端FPGA将某路A/D采样后频率为2 561 MHz的正弦信号同时分发给6个JESD204B TX IP作为数据源,SYNC信号通过反向通道传输自定义报文传输,得到的接收端测试结果如图5所示。 图5 片内 JESD204B同步测试结果 测试结果表明JESD204B协议初始化成功,为了更直观地显示同步结果,每个通道只抽取其中的一路进行比较,从测试结果可以看到,6个通道接收到的采样数据相位一致,接收到的采样数据是同步的。 (2) 板间多通道同步实验 4个发送通道分别位于2块板卡的FPGA内,发送通道1、2位于发送板卡a中,发送通道3、4位于发送板卡b中,板卡间通过全双工光纤连接。通过上述参数设置的JESD204B协议向接收板卡传输同步数据,接收端板卡通过收发器自定义命令报文向2块发送板卡发送SYNC信号的信息,并通过控制报文同时将发送数据切换到计数器模式,接收端得到实验结果(如图6所示)。 图6 板卡间 JESD204B同步测试结果 此时接收端4路通道接收到的计数值和波形相同,说明此数据是严格同步的。实验结果表明该设计能够保证SYNC信号与命令控制报文的正确传输,并保证板间及通道间的数据同步。最后通过反复多次加电进行可靠性测试,均能满足同步设计需求,证明了同步设计的正确性与可靠性。 本文在比较基于Aurora协议与基于JESD204B协议的数据同步传输方案的基础上,重点分析了基于JESD204B协议的FPGA片间数据同步传输要点,并对协议SYNC信号的传输进行了改进,提高了FPGA收发器利用率,节约了系统的走线资源。最后在板卡上验证同步传输功能,实验结果表明该方案能够有效完成系统数据的同步传输,为工程应用奠定了基础。

3 片间JESD204B同步功能验证

4 结束语