一种全集成通道级双输出低压差稳压器设计*

2018-12-20魏晓敏胡永才

王 佳,魏晓敏,郑 然,李 萍,胡永才

(西北工业大学 计算机学院,陕西 西安 710072)

基于射线和物质相互作用原理,半导体辐射探测器在被粒子击中后可产生具有一定特征的电信号.通过前端读出电路,对该信号进行放大、成形、峰值采样保持、模数转换等处理后送给计算机.然后采用专门的算法来得到粒子的能量、位置和时间等可用信息.因此,前端读出电路是辐射探测系统中的关键部件,其噪声等性能直接关系到整个探测器系统的优劣.像素型探测器的每个像素都需要有独立的通道进行读出[1-2].因此,大面阵像素探测器的读出通道数量更多,芯片面积更大.此时,芯片上的电源线和地线带来的寄生电阻、寄生电容较大,不可忽略.尤其对于远离电源管脚的通道,相邻通道之间的串扰变得更加严重.另外,这些寄生参数可能进入读出电路的反馈回路,电源线上的随机扰动会导致读出电路的振荡,使其无法正常工作.

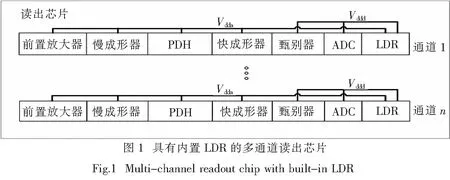

超多通道芯片设计时,需要对电源和地走线的寄生进行计算.这样,增加了版图设计的复杂度,而且对于通道间串扰的抑制能力较为有限.为了更好地解决该问题,提出了一种可全集成在单个通道内的双输出低压差稳压器(low dropout regulator, LDR)电路.提出的电路可同时输出模拟电源电压(Vdda)和数字电源电压(Vddd),实现模拟电路和数字电路的独立供电,避免二者之间的相互干扰.如图1所示,前置放大器、慢成形器、峰值采样保持电路(peak detect and hold, PDH)、快成形器等对电源噪声较为敏感的模拟电路由Vdda供电.而其他电路对电源噪声要求不高,由Vddd供电.普通的多通道稳压器一般采用将两个独立的LDR进行集成的方式实现,因此面积和功耗较大[3].本文所设计的稳压器复用了部分电路,减小了面积和功耗,可以集成于单个通道内.通道之间将不再共享电源,可以降低串扰.

1 电路设计

如图2所示,稳压器由三部分组成:误差放大器,缓冲级,输出级.两路缓冲级和输出级电路完全相同,分别输出模拟电源电压Vdda和数字电源电压Vddd.误差放大器和反馈电阻串共用,可以减小芯片面积.本文LDR与普通LDR的工作原理基本相同.反馈电阻采样得到反馈电压,误差放大器使其与基准电压Vref相等,调节缓冲级和输出级使得输出电压稳定为与基准电压成一定比例关系的电压值.整个系统为负反馈.除了该反馈通路外,本文电路增加了一路负反馈.将输出电压输入误差放大器和缓冲级部分电路的电源端,从而形成单位缓冲器结构.而输出级的电源仍为外部直接输入电源电压Vin.因为没有连接反馈电阻,电压Vddd的调节完全靠新增加的负反馈进行控制.误差放大器将反馈电压与基准电压进行对比运算得到电压Va.输出稳定时,该电压也恒定不变.然后,驱动缓冲级和输出级来保证Vddd不变.但是Vddd的变化无法反馈给误差放大器,仅靠缓冲级进行调节控制输出管的栅极电压.因此,数字电源电压Vddd的调节能力较差.而数字电路一般比模拟电路的抗干扰能力强,所以,该电路可满足设计需求.

缓冲级和输出级的晶体管电路如图3所示.误差放大器的输出电压Va输入一个二极管负载共源放大器中,作为第一级缓冲,然后输入给第二级缓冲,同时改变电压极性.最后一级为共源共栅结构放大器,提供高增益,驱动输出管.第一级共源放大器的电源连接到输出电压,因此当反馈电压保持不变时,该级放大器也可以看作是共栅极放大器.当输出电压变低时,共栅放大器输出变低,输出管栅极电压变低,使得输出电压升高.整个回路为负反馈,从而保持输出电压不变.该电路实质上为电位平移结构,输入电压Va和输出电压Vout之差约为PMOS管的阈值电压.因此,当Va恒定不变时,在一定负载电流范围内,Vout也保持不变.另外,将输出电压反馈到前级电路,可以为LDR的输出管提供对地电流通路,在负载电流为0时,电路仍可正常工作.

如图2所示,输出电压Vdda和Vddd的生成电路之间相互独立.当其中一个输出端电压出现电压陡变时,另外一个输出受到的影响较小.例如,Vddd的负载电流突然增大,其电压会降低.然后,该电压变化反馈到缓冲级和输出级进行调节,保持不变.而Vdda通路上只有Va受其影响.这是因为Vddd和Va之间存在寄生MOS电容,所以Va发生较小变化.但是电压Va主要由误差放大器确定,所以Vdda几乎不变化.为了进一步降低瞬态电流的影响,尤其是多个数字电路同时跳变产生的较大瞬态电流的影响,本文设计的稳压器分别在两个输出端加入了滤波电容.

2 仿真结果与讨论

本文提出的稳压器电路基于0.25 μm 2P5M商用标准CMOS工艺设计实现,并采用SPECTRE进行了仿真.为了验证所设计稳压器提供负载电流的能力,分别在Vdda和Vddd端放置恒定电流源.图4给出了该负载特性的仿真结果.可以看出,Vdda和Vddd可提供的最大负载电流分别约为4.4 mA和3 mA.因为Vdda的增益更高,所以可提供的最大负载电流较大.该稳压器可以满足文献[4-5]中单通道读出电路的电流需求,且留有部分设计裕度.

因为Vdda对电压变化要求更高,更易受影响,所以在Vddd端放置一个峰值为0.5 mA的脉冲电流源来验证两个输出电压之间的干扰.为了验证最差情况,分别在两个输出端直流负载电流均处于最大值时进行仿真,结果如图5所示.Vddd上仅出现峰值为27 mV的毛刺,而Vdda的波形上几乎没有变化.这主要由于滤波电容和反馈回路的抑制作用.该波形也验证了提出的稳压器电路可以很好地抑制两个输出端之间的干扰.

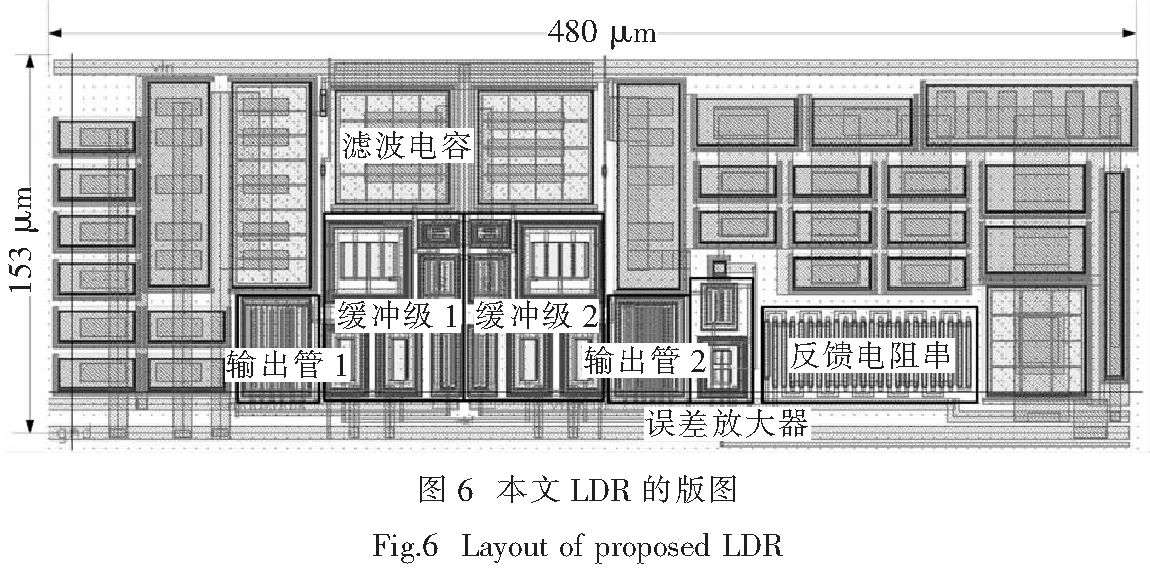

本文LDR的版图如图6所示,为了保证两个输出电压相等,两路缓冲级和输出管靠近对称摆放,提高器件的匹配度.芯片面积为480 μm×153 μm.误差放大器等核心电路占的面积较小,大部分面积被滤波电容占据,其次为输出管和反馈电阻串.如果实际应用中电流波动较小,可以减小滤波电容,从而进一步减小芯片面积.也可以考虑一个稳压器同时驱动两个通路,这样也可以满足在通道内集成的要求.该稳压器在最大负载情况下的压差电压为0.2 V,消耗的静态电流仅为25 μA.因此,全集成到通道内,不会显著增加单个通道的功耗.

3 结论

为了解决读出电路中通道之间的电源干扰问题,本文提出了一种全集成通道级双输出稳压器电路.所提出的电路采用一种简单的缓冲器电路结构维持输出电压的稳定.共用误差放大器和反馈电阻串,进一步减小了芯片面积和功耗.本文电路基于0.25μm 2P5M商用标准CMOS工艺设计和实现.SPECTRE仿真结果表明,所设计稳压器的负载能力满足单通道读出电路需要,并且可以很好地抑制两个输出电压之间的干扰.