基于FPGA的串口实现

2018-12-20孙列鹏杨化路程宇峰

张 诚,孙列鹏,肖 薇,杨化路,程宇峰

基于FPGA的串口实现

张 诚1,孙列鹏2,肖 薇1,杨化路1,程宇峰1

(1. 北广科技股份有限公司,北京 101312;2. 北京航空航天大学,北京 100082)

串口作为一个简单可靠的通讯方式,广泛的应用于现代电子工业中。目前产品中定时控制分系统与其它的分系统的通信都是由串口来完成的,实现串口的方法大部分是由TI公司的DSP来实现的。本文先对串口协议进行研究,然后介绍串口设计中需要注意的几个问题,最后根据目前的项目对基于FPGA的串口设计做详细的说明。

串口;协议;FPGA;VHDL

0 引言

通常提起串口我们都会想到计算机的串口,在工业控制和通信当中串口通信应用也很广泛。这些领域的串口都是按照计算机的串口标准来做的,这样极大的方便了用计算机来调试设备。

1 串口协议

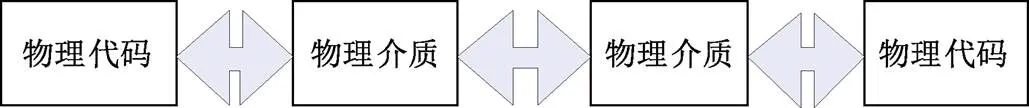

目前我们做的串口,都是按照或者参考计算机的串口协议来做的。用于计算机的串口协议有两种:一种是RS-232,它是是IBM-PC及其兼容机上的串行连接标准。我们见到的计算机大部分都是采用的这种标准,它的外围电路是由专用芯片(如8251)和电平驱动芯片(如MAX232)来组成的。串口通信的逻辑主要由专用芯片来完成(包括信息的发送和接收和主板总线的通信),电平驱动芯片主要完成电平的转换。另一种标准是RS-422,它是Apple的Macintosh计算机的串口连接标准,它的组成和RS-232类似,有区别的是RS-422采用了差分线进行传输,这使得传输的抗干扰性和传输距离大大的提高了。还有一种标准是RS-485,它是RS-422的改进,如图1所示。

图1 串口通信的物理层组成

如图1所示,物理层由物理介质和物理代码组成,物理介质由驱动芯片以及外围电路和传输电缆等用于物理信号传输的介质组成,而物理代码完成了通信的逻辑,它可以是8251这样的专用芯片,也可以是单片机,DSP,FPGA这样的可编程器件。我们通常所看到的MAX488,MAX232等驱动芯片和传输线都是物理介质。一般计算机是RS-232标准,而我们所设计的电路板都采用了RS-422的标准,所以我们在和计算机通信的时候都会采用一个转接头;而物理代码则通常用DSP,CPLD/FPGA来实现的,这样DSP,CPLD/FPGA还能完成其他的功能,增加了设计的集成度。

串口通信分为同步通信和异步通信。同步通信比异步通信传输信息的质量要好,但是同步通信的硬件电路比异步通信的电路电路要复杂的多,需要硬件连线数增多。如果设计的系统比较复杂,所需要的连线数会成倍的增加。终端定时控制分系统和其他分系统的串口有10-20多个,如果每个串口增加了两根握手信号,我们需要的连线就会有20-40多个。这大大的增加了连线的困难。所以在一般应用中都会采用异步串口通信,因为异步通信只需要三根线(收,发,地),虽然异步通信比同步通信传输的信息少了20%,但是由于其硬件结构比较简单所以在很多设计中都用了异步通信的方式。本文所讨论以及实现的都是异步串口通信。

2 异步串口通信

2.1 监听机制

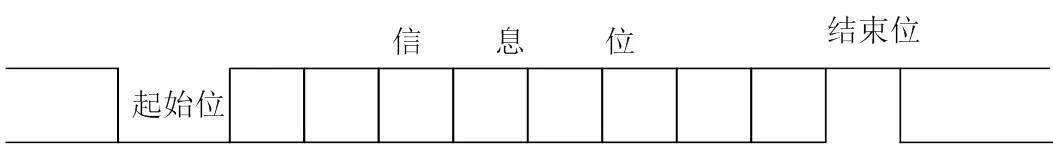

异步通信的时候,通信双方都不知道什么时候通信开始,什么时候通信结束。这样就需要在传输线上有信号位来标志通信的发起和结束。串口通信中所采用的是在发送信息前先发送一个起始位,在信息结束的时候发送一个结束位。这样本来传送8位的信息就会传送10位,这样信息的传送率为80%。因为串口通信本来就是慢速的通信,所以这种损失是允许的。在具体的信号线上,当没有信息发送的时候,信号线上的信号是‘1’,当有信号发送的时候有一位‘0’;当接收信息结束的时候,在结束位会出现信号‘1’,如图2所示。

图2 异步通信的传送位关系

2.2 时钟与定时

异步通信是相对于同步通信来说的,异步通信之间数据的传输率是相同的,由通信双方规定好。也就是说数据位的速率是相同的,异步接收的时候通过监听机制监听到起始位后开始定时接收,如图3所示。为了保证通信的可靠性,系统工作的时钟要高于数据率的时钟。8251要求系统的工作时钟为数据率的4-6倍,如果数据时钟是9600,那么系统的工作时钟就是38.4 k-57.6 k1。图3是以数据位的五倍时钟来说明的,当开始定时接收的时候,定时器开始循环计数,当计到三的时候,把数据锁存起来,这样保证锁存的数据前后有一定的时间间隔,比较稳定。当遇到停止位的时候,计数停止。系统工作的时钟也可以高于数据率的4-6倍,比如16倍,这样计数器就是模16计数,锁存的时候可以在计数器为8的时候锁存,也可以在4的时候锁存,所以很多串口通信中可以设置结束位为四分之一,或者二分之一位。

图3 异步通信的接收定时时序

异步通信所传送的数据位数也是事先规定好的,至少为10位(8位信息加上一位起始位和一位结束位),如果还有奇偶校验位,那就11位了。具体的位数要看实际中的应用,但是一定要保证通信双方一致[3]。

2.3 纠错机制

在通信中纠错是重要的指标之一,一个好的通信系统不仅要知道传输的数据错误,而且还要对传输的数据进行纠错[4]。在异步串口通信当中,在传输的是一个字节时,一般采用奇偶校验的方法,在8个数据位后多一个奇偶校验位,在接收的时候对其进行检验,如果正确则存储,如果错误,则采用相应的机制来纠错。当异步传输的是很多字节组成的数据包时,会在数据包后面加上冗余码,一般为CRC码,这种码是固定的多项式,通过计算可以对错误的数据进行纠错[1]。

采用的检测方法是将数据包里的数据进行累加,发送的时候将累加的值放在数据包相应的位置,接收的时候对传输的数据包的数据也进行累加,两者进行比较后,向发送端反馈相应的数据包。发送端检测数据包,如果是正确的数据包则不作处理,如果是错误的则重新发送相应的数据包。

这种检测方法要求通信的基本单位是数据包,纠错的手段是重发机制。因为产品中串口所发送的都是命令协议,时间多为一秒以上,所以这种纠错机制是很适用的[5]。

FPGA作为一种可编程器件已经为大家所熟悉了,这里就VHDL语言编写的收发程序给大家介绍一下。[6-7]这部分主要包括发送程序(物理层),接收程序(物理层),以及发送处理(顶层,主要对反馈后的数据包进行处理),接收处理(顶层,对接收的数据包进行处理)[2]。

3 程序设计

3.1 发送程序

发送的过程如下:发送器检测到发送处理程序发送有效标号后,发送计数器和分频计数器开始计数,同时根据发送的数据产生奇偶校验位,根据发送计数器的状态,进行串并转换,进行发送。[8]

PROCESS(CLK48K,T_CO)

BEGIN

IF(CLK48K'EVENT AND CLK48K='1')THEN

CASE T_ST IS--状态表,S0表示无发送;S1表示发送状态。

WHEN S0=>

T_COUNT<="000";

IF(T_CO='1')THEN

T_COU<="0110";

T_ST<=S1;

T_TEMP1(7 DOWNTO 0)<= T_TEMP;--T_TEMP1

ELSE

T_COU<="0000";

END IF;

WHEN S1=>

IF(T_COUNT="100")THEN T_COUNT<="000";

ELSE

T_ST<=S1;

END IF;

END CASE;

END IF;

END PROCESS;

3.2 接收程序

接收过程如下:接收器探测到起始位,定时计数器和分频计数器开始工作,当分频计数器等于2的时候,将接收的数据进行串并转换,当接收满8位并且探测到停止位的时候,接收停止,并将接收的结果发送到接收处理程序中去。

PROCESS(CLK48K)

BEGIN

IF(CLK48K'EVENT AND CLK48K='1')THEN

CASE R_ST IS

WHEN S0=>

R_DOUT<=(OTHERS=>'1'); R_TEMP<=(OTHERS=>'1');

R_EN<='0';

IF(R_DATA='0')THEN

R_COUNT<="0110000";

R_ST<=S1;

ELSE

R_ST<=S0;

R_COUNT<=(OTHERS=>'0');

END IF;

IF (R_COUNT(6 DOWNTO 3)>= "0110" AND R_COUNT(2 DOWNTO 0)="010")THEN

END IF;

END PROCESS;

3.3 接收处理

接收处理的过程如下:接收处理程序接收到接收程序发送的有效信号和数据后,对数据进行存储,并对存储的数据进行检验,将检验后的结果发送到发送处理程序中去。

PROCESS(RE_STEN,R_EN)

VARIABLE RE_ST : STD_LOGIC_ VECTOR (2 DOWNTO 0);

BEGIN

IF(RE_STEN='1')THEN

RE_ST:="000";

ELSIF(R_EN'EVENT AND R_EN='1')THEN

CASE RE_ST IS

WHEN "000"=>

RE_ST:="001"; RE_ST:="001";

RE_FLAG<='0';

WHEN "001"=> RE_ST:="010";

RE_FLAG<='0';

WHEN "010"=> RE_ST:="011";

RE_FLAG<='0';

WHEN "011"=> RE_TEMP1<=RE_TEMP; RE_ST:="100";

RE_FLAG<='0';

WHEN "100"=> RE_ST:="101";

RE_FLAG<='1';

WHEN "101"=>

RE_TEMP2<=RE_TEMP; RE_ST:="110";

RE_FLAG<='0';

WHEN "110"=>

RE_TEMP3<=RE_TEMP;

RE_ST:="000";

RE_FLAG<='0'; WHEN OTHERS=>

RE_FLAG<='0'; RE_ST:="000";

END CASE;

END IF;

END PROCESS;

PROCESS(RE_TEMP1,RE_TEMP2,RE_TEMP3)

—检测数据侦的结果正确发送正确标志,错误发送错误标志

BEGIN

IF(RE_TEMP1+RE_TEMP2+X"76"=RE_TEMP3)THEN

RE_ERROR_FLAG<='0';

RE_RIGHT_FLAG<='1';

ELSE

RE_ERROR_FLAG<='1';

RE_RIGHT_FLAG<='0';

END IF;

END PROCESS;

3.4 发送处理

发送处理的过程如下:发送处理程序接收到接收处理程序的检验结果,根据结果,发送处理程序向发送程序发送有效标志和数据包(按字节发送),并且在数据包相应的位置加入正确或错误字节。[9-10]

PROCESS(RE_FLAG,CLK48K,RESET)

VARIABLE TR_COUNT : INTEGER RANGE 0 TO 100;

VARIABLE TR_ST : STD_LOGIC_ VECTOR(4 DOWNTO 0);

BEGIN

IF(RESET='0')THEN

TR_ST:="01011";

ELSIF(RE_FLAG='1')THEN

TR_ST:="00000";

TR_COUNT:=0;

ELSIF(CLK48K'EVENT AND CLK48K='1')THEN

IF(TR_COUNT=450)THEN

TR_COUNT:=0;

TR_EN<='0';

TR_DATA<=X"FF";

ELSIF(TR_COUNT=2)THEN

CASE TR_ST IS

WHEN "00000"=>

TR_EN<='0';

TR_DATA<=X"FF";

TR_ST:="00001";

WHEN "00001"=>

TR_EN<='0'; TR_DATA<=X"FF";

TR_ST:="00010";

WHEN "00010"=>

TR_EN<='0'; TR_DATA<=X"FF";

IF(RE_EN='1' AND RE_RIGHT= '0')THEN

TR_ST:="00011";

ELSIF(RE_EN='0' AND RE_ RIGHT='1')THEN

TR_ST:="10001";

ELSE TR_ST:="00010";

END IF;

WHEN "00011"=>-- 发送反馈正确数据包

TR_EN<='1';

TR_ST:="00100"; TR_DATA<=X"7E";

WHEN "00100"=>

TR_EN<='1';

TR_ST:="00101";

TR_DATA<=X"15";

WHEN "00101"=>

TR_EN<='1';

TR_ST:="00110";

TR_DATA<=X"61";

WHEN "00110"=>

TR_EN<='1';

TR_ST:="00111";

TR_DATA<=X"9E";

WHEN "00111"=>

TR_EN<='1';

TR_ST:="01000";

TR_DATA<=X"04";

WHEN "01000"=>

TR_EN<='1';

TR_ST:="01001";

TR_DATA<=TR_TEMP;

WHEN "01001"=>

TR_EN<='1';

TR_ST:="01010"; TR_DATA<=X"14"+TR_TEMP;

WHEN "01010"=>

TR_EN<='1';

TR_ST:="01011";

TR_DATA<=X"7E";

WHEN "01011"=>

TR_EN<='0';

TR_ST:="01011";

TR_DATA<=X"FF"; WHEN "10001"=>-- 发送反馈错误数据包

TR_EN<='1';

4 结论

本文重点讨论了串口通信的物理层协议,给出了基于FPGA的实现方法。本文的程序将光纤接收单元和终端定时与控制单元的串口通信中。本程序已经在试验阶段通过。

[1] 邬宽明《单片机外围器件实用手册数据传输接口器件分册》, 北京航天航空大学出版社. 2001: 100-113.

[2] 李新兵《兼容ARM9的软核处理器设计基于FPGA》, 机械工业出版社. 20012: 20-30.

[3] 谢显中, 王新梅. 第三代移动通信系统的空中接口方案[J]. 移动通信. 1999(01).

[4] 谢显中, 苗洪雷, 李颖, 王新梅. 分层空时码的模型、译码接收及其性能仿真[J]. 通信学报. 2001(08).

[5] 葛利嘉, 路鸣. 蜂窝通信的空分多址: 概念、算法和性能[J]. 通信学报. 1999(08).

[6] 王蕾, 韩立峰. 基于Artix-7 FPGA的异步高速串行通信IP设计[J]. 现代电子技术, 2018, 41(19): 6-10.

[7] 王蕾, 李淑婧. 一种基于FPGA+DSP的高速串口通信设计[J]. 现代电子技术, 2018, 41(15): 22-25+30.

[8] 徐巧玉, 周新稳, 王军委, 朱佩. 一种ARM+FPGA的可裁剪以太网串口服务器设计[J]. 河南科技大学学报(自然科学版), 2018, 39(06): 24-29+34+5.

[9] 甘康, 蔡锦达, 邹亿, 刘倩. 基于ARM和FPGA的LED标准光源电路设计[J]. 光学仪器, 2018, 40(03): 38-45.

[10] 白晓. 基于FPGA的状态采集与快保护系统子板设计[D]. 中国科学院大学(中国科学院近代物理研究所), 2018.

Implementation of Serial Port Based on FPGA

ZHANG Cheng1, SUN Lie-peng2, XIAO Wei1, YANG Hua-lu1, CHENG Yu-feng1

(1. Beijing BBEF Science & Technology Co., Ltd, Beijing 101312, China; 2. Beihang University Beijing 100082, China)

As a simple and reliable communication method, serial port is widely used in modern electronics industry. At present, the product communication between the timing control subsystem and other subsystems is completed by serial ports. Most of the methods for serial ports are implemented by the DSP of TI company. Firstly, this paper studies the serial port protocol, then introduces several problems that need attention in the serial port design. Finally, according to the current project, the FPGA-based serial port design is described in detail.

Serial port; Protocol; FPGA; VHDL

TN79

B

10.3969/j.issn.1003-6970.2018.11.046

张诚(1980-),男,硕士,高级工程师,研究方向:为射频微波系统设计、电子技术;程宇峰(1970-),男,本科,高级工程师,研究方向:高频系统设计开发技术方向;孙列鹏(1979-),男,博士,职称:高级工程师,研究方向:高频系统设计开发技术方向;杨化路(1965-),男,硕士,职称:高级工程师,研究方向:高频系统设计开发技术方向;肖薇(1971-),男,硕士,职称:高级工程师,研究方向:结构系统设计与工艺。

张诚,孙列鹏,肖薇,等. 基于FPGA的串口实现[J]. 软件,2018,39(11):219-223