K波段高功率放大器MMIC设计

2018-10-27陆雨茜陈华康

陆雨茜,陈华康,高 博,龚 敏

(四川大学物理科学与技术学院,成都 610065)

1 引言

随着无线通信的发展,相对较低波段的利用率已经趋于饱和,低频段频率的拥挤促使电路设计逐渐向高频段发展。在K波段(18~27 GHz),随着本地多点通信系统(LMDS)和防撞雷达等应用的发展和微电子工艺技术的成熟,毫米波单片电路的需求越来越大[1]。除此之外,K波段在工业界、科学界以及医疗界都有应用,该波段适用于高数据传输速率、近距离雷达系统以及自动车载雷达等[2]。

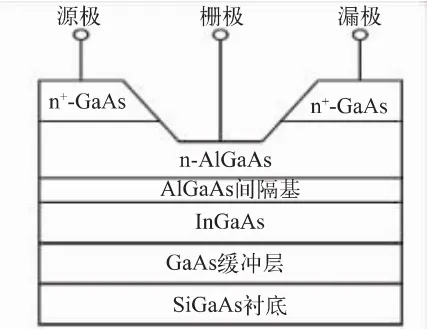

随着微电子工艺技术的发展,GaAs功率器件的发展十分迅速,它们具有高频特性好、可靠性高、功率密度高、线性度高、体积小[3]等特征。GaAs pHEMT采用多种不同的材料层合成,采用InGaAs层作为沟道材料,AlGaAs和InGaAs在界面处通过势阱形成二维电子气(2DEG),如图1所示。与传统的HEMT相比,二维电子气的迁移率高,平均饱和速度高,使得pHEMT的频率特性与功率特性都得到了提高[4]。

图1 pHEMT结构示意图

本文所设计的GaAs MMIC功率放大器采用截止频率为60 GHz的0.25 μm GaAs pHEMT工艺,通过有耗匹配和三级级联放大等技术实现了电路设计。工艺采用TaN金属膜电阻、重叠式MIM(M1/Si3N4/M2)电容器、空气桥连接和背面通孔等技术。

2 功率放大器电路设计

微波功率放大器在设计过程中需要将多种设计因素考虑在内,相较于小信号放大器,功率放大器在要求较高输出功率的同时,对电路的增益及附加工作效率也有一定要求,设计更加复杂。末级器件的总栅宽根据电路所要求的输出功率加以确定,保证足够功率输出的同时兼顾效率[5]。通过对器件的分析可以得知,仅采用单个晶体管难以达到较高的输出功率,所以放大器采用功率合成的方式以满足高输出功率的要求。

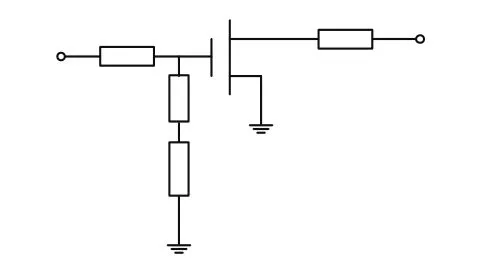

2.1 有耗匹配结构

在功率放大器的设计过程中,为了得到较为平坦的增益,一般采用有耗匹配电路结构,最常见的拓扑结构是在电路的输入端或输出端采用串有电阻的短路线,如图2所示。其工作原理是:当电路工作在低频时,短路线呈低电抗,电阻消耗增益;当工作在高频时,短路线呈高电抗,电阻对增益的影响较小。因此,匹配网络可以引入一个正增益斜率,从而抵消器件的增益随频率滚降的部分[6]。与此同时,电阻器可以起到在低频时缓解电路不稳定的作用。

图2 有耗匹配电路拓扑结构

2.2 有源器件选择

结合实际工艺与设计指标,综合选择三级有源器件尺寸,电路输入与输出结构之间采用有耗匹配。经过查阅模型手册得知,实际工艺的晶体管饱和输出功率密度为550 mW/mm,在达到最终设计目标的同时,需要为输出功率结合器预留3 dB的裕量。经过计算,总晶体管栅宽应达到7.24mm。考虑到两个指叉之间的间距为100 μm,为了尽可能减小版图面积,第三级有源器件选择120μm×8(单指栅宽120μm,栅指数为8)。

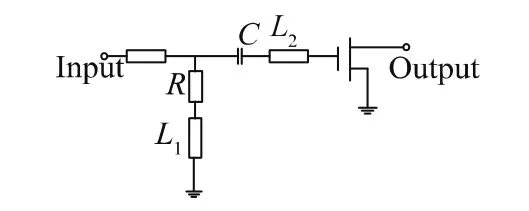

输入级不仅要提供增益,还要使输出级达到饱和输出功率。若前级与后级有源器件总栅宽比不够大,则会导致整体的功率压缩,影响电路效率;若总栅宽比太大,则会使前级电流过大,极大地降低电路效率。为了提供足够的输入功率,输入级与输出级之间的晶体管栅宽比例为0.5:1[7]左右,从而确定第二级有源器件选择 100 μm×6(单指栅宽 100 μm,栅指数为 6)。同理可以确定第一级有源器件选择100 μm×4(单指栅宽100μm,栅指数为4),最终电路结构示意图如图3所示。

图3 K波段功率放大器结构示意图

2.3 电路稳定性设计

由于电路设计采用的有源器件不是绝对稳定器件,所以需要考虑电路的全频带稳定性,以保证电路在实际工作中的稳定与可靠性[8]。ADS软件中,主要通过稳定因子(k)来对电路是否稳定进行判断,为了保证电路在全频段的稳定性,二端口网络必须保证在全频段k>1。k值越大,则表示电路的稳定性越强。

在功率放大器的设计过程中,常采用在输入匹配和级间匹配电路中增加电阻电容并联网络的方法,如图4所示[9]。在低频时,传输线电抗较小,匹配网络中的电阻可以降低电路增益;在高频时传输线电抗较大,匹配网络中的电阻影响很小[10]。这种电路结构降低电路的增益,从而提高电路的稳定性和增益平坦度。

图4 电阻电容并联网络

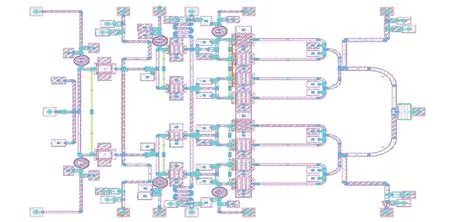

3 功率放大器版图设计与仿真

由于微波功率放大器工作在较高频段,实际元件制作在一定大小的芯片上,各类器件会产生十分显著的电磁耦合效应,对电路进行三维电磁场仿真至关重要。选取合适的元件对电路进行适当调整,从而在节省仿真时间、提高仿真效率的同时,使版图更加合理化。为了保证版图与原理图仿真结果的一致性,在原理图仿真时电路结构与分布版图需要完全相同;为了避免偏置电流之间互相干扰,每一级电路偏置均独立设计,并且通过滤波电容对低频信号进行滤除。为了保证电流容量,本设计均采用双层金属走线设计,同时对寄生参数有一定的削减作用。通过电磁场设计、仿真和调试,尽量缩小芯片面积以提高成品率,确定功率放大器最终的版图如图5所示,版图面积为2.5mm×3.2 mm。

图5 K波段功率放大器版图设计

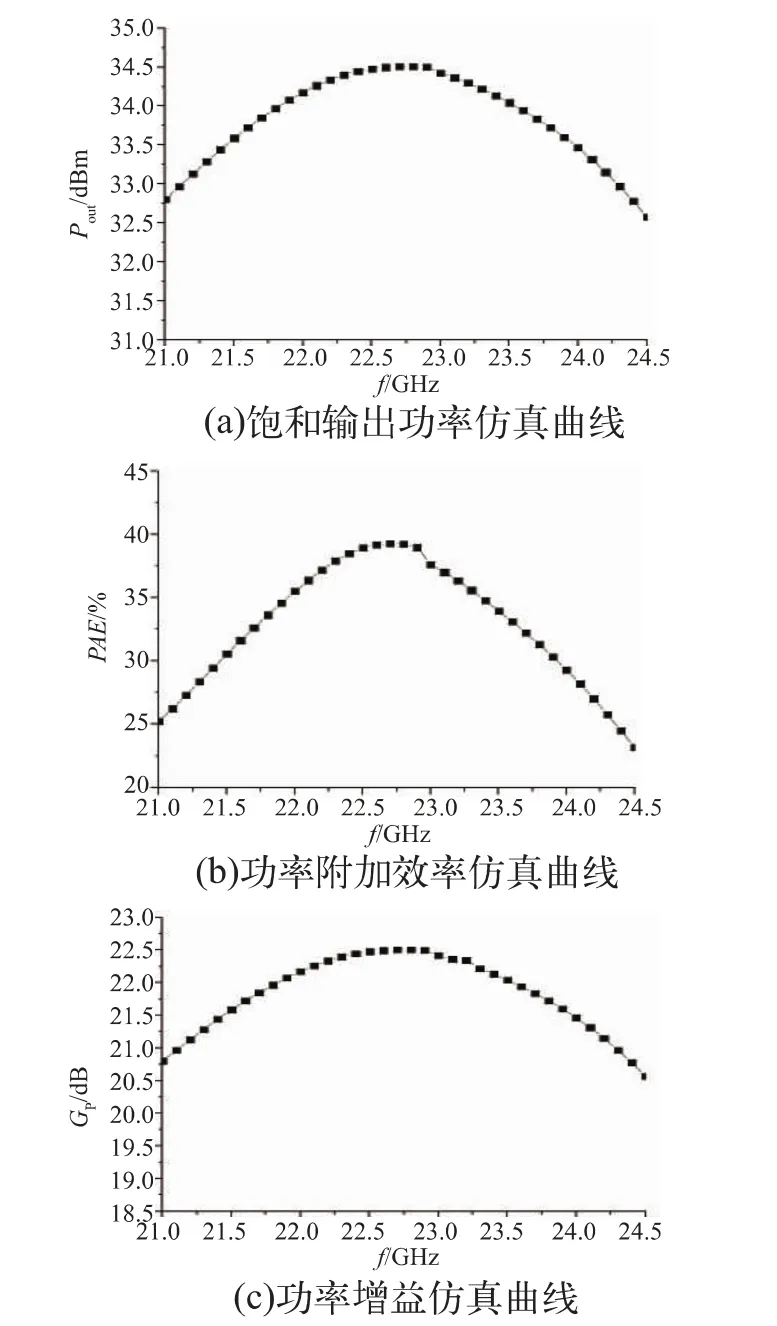

通过大量的调试,电路输出功率仿真曲线如图6所示。仿真结果显示,当功率放大器电路工作在21~24.5 GHz时,饱和输出功率大于33 dBm,功率附加效率大于25%,功率增益大于19 dB。

图6 功率放大器电磁场仿真结果

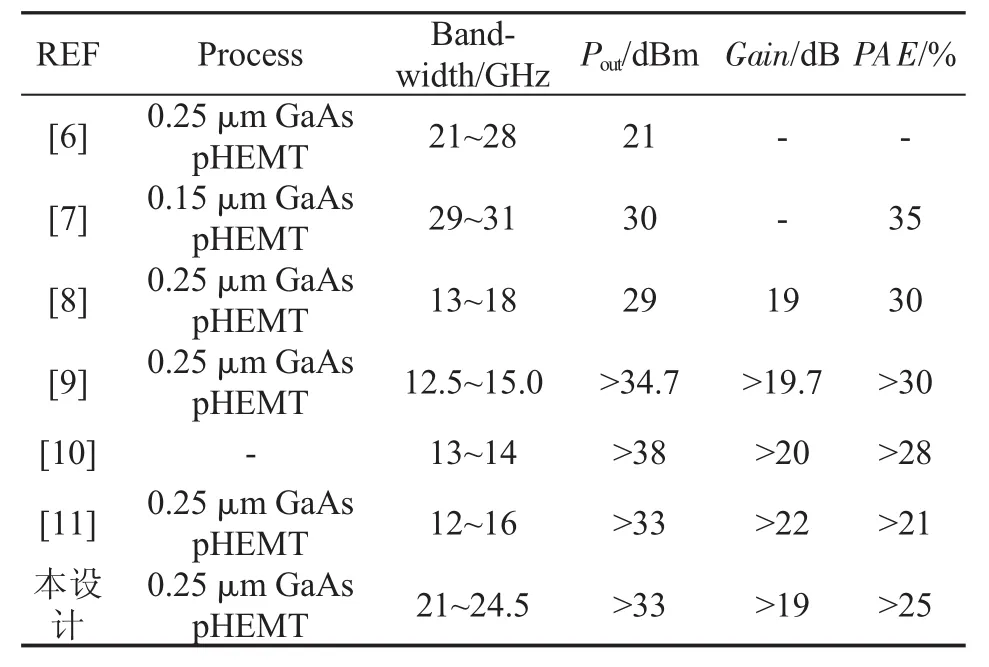

本次工作与近几年文献中功率放大器电路的平行比较如表1所示。从表1中可知,本功率放大器相对于同类放大器电路具有较高的工作频率,且在输出功率方面体现出了一定的优势。

表1 不同文献中设计的功率放大器电路性能参数对比

4 结论

本文基于0.25 μm GaAs pHEMT工艺,采用了三级级联的电路结构,用微带电路实现电路输入、输出和级间匹配,实现了一款工作在K波段的高功率放大器,各级栅宽比为1:1.5:2.4。经 ADS仿真结果显示,当放大器工作在21~24.5 GHz时,饱和输出功率大于33dBm,功率附加效率大于25%,功率增益大于19 dB,具有良好的微波性能。