一种优化FPGA测试配置时间的方法

2018-10-27肖艳梅

肖艳梅,陆 锋,2

(1.江南大学物联网工程学院,江苏无锡 214122;2.中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 概述

现场可编程门阵列(Field-Programmable Gate Array,FPGA)芯片已广泛应用在通讯、汽车电子和计算机等领域。为保障芯片应用的可靠性及稳定性,亟需发展能够快速、精确测试FPGA的科学方法。

覆盖率以及测试时间是FPGA测试的关键[1]。目前大多数FPGA测试方法的目标为在保证高的故障覆盖率条件下尽量减少配置次数,但同时测试时间也呈线性增加。文献 [2]、[3]指出,大约95%~99%的FPGA测试时间用于加载测试配置位流 (TCB),这些TCB占据了FPGA测试数据量的95%以上[2,3]。

以Virtex-7 FPGA为例,位流文件约为450 Mb[4],如此大的数据量会带来很多问题。首先,测试系统需要非常大的向量深度来存储这些向量;其次,FPGA配置过程所占的时间比重越来越大,造成测试成本急剧增加[5]。减少加载测试配置比特流所花费的测试时间成为一个关键问题[6]。

本文基于Advantest公司V93000 SoC测试系统,从“配置时间开销”的角度出发,提出以FPGA的4X配置方式来减少配置比特流的测试时间,进而减少FPGA编程下载时间,提高在系统配置速度,降低测试成本。

2 FPGA配置模式及配置流程

2.1 FPGA配置模式选择

基于 ATE(Automatic test equipment,即自动测试设备)对FPGA进行测试的大部分时间使用在配置上,因而对配置模式的选择尤其重要。如表1所示,FPGA主要的配置模式有边界扫描、主串、从串、主并和从并模式。为了节省测试配置时间,本文采用从并配置模式对FPGA进行测试配置,原因是从模式的时钟CCLK可从外部提供,同时并行模式可以令32位数据并行加载。

表1 FPGA配置模式

2.2 FPGA配置流程

FPGA的配置过程是一种自动装载配置数据的过程,主要有以下5个步骤:上电、清除配置存储器、初始化、载入配置存储器、启动。FPGA具体配置流程如图1所示。

3 基于V93000的4X配置原理

利用ATE将配置向量载入配置存储器的传统做法是测试机在一个周期内加载1行配置向量,通过在一个周期内设置一个比较沿来读取各个输出管脚的数据。但随着FPGA规模发展到千万门级甚至是亿万门级,配置码越来越大,测试数据量非常庞大。数量巨大的配置向量一方面要求测试系统需要极大的向量深度来存储这些向量,另一方面FPGA配置过程中所占的时间比重也越来越大,造成测试成本急剧增加。

图1 FPGA配置流程

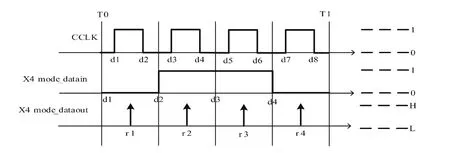

基于V93000的4X配置方式是在一个周期内加载4行配置向量,通过设置4个比较沿来读取各个输出管脚的数据,相当于在一个周期内完成了4位向量的读取。与一般配置方式相比,相同的时间内4X配置方式可以读取4倍大小的配置向量。也就是说,现有V93000每个通道向量深度有112 M,利用4X模式后使可容许的向量深度达到了448 M。换言之,在配置向量一定的情况下,每个测试配置的编程下载时间将减少75%,解决了FPGA测试数据配置与测试时间的矛盾。图2为X/4X模式示意图,X模式下,数据在输入驱动沿d1、d2处发生变化,ATE在输出比较沿r1处进行采样;4X 模式下,数据在输入驱动沿 d1、d2、d3、d4、d5、d6、d7、d8 处发生变化,ATE 在输出比较沿 r1、r2、r3、r4处进行采样。

图2 一般配置方式/4X配置方式示意图

4 4X模式设置与测试实现

4.1 4X模式设置

V93000测试平台的每根通道都有自己独立的向量存储、施加和测量单元,硬件上每根信号管脚都有自己的TIMING文件和PATTERN文件,而且在测试时都是并行操作[7]。在ATE中,通过测试程序对驱动沿、比较沿、时钟周期的定义,结合配置文件中存储的数据,形成实际测试时所需的测试向量。

4X模式设置体现在TIMING的设置上,TIMING主要指的是波形的种类以及时序关系。基于周期的ATE测试语言对测试向量有以下4个方面的信息要求[8]:1)测试周期;2)波形调制格式,如 NRZ(不归零)、RO(归一)、RZ(归零)、SBC(环绕补码);3)定时信息(包含输入驱动沿、输出比较沿);4)状态信息(各类管脚的波形值)。

在V93000测试系统中,TIMING WAVETABLE定义波形调制格式,即配置向量的输入输出波形的种类,这里把时钟引脚CCLK定义为RZ码,即归零码,当数据为0时没有变化,数据为1时提供一个正向脉冲;其他输入脚定义为NRZ码,即不归零码,它代表存储于向量存储器的实际数据,只在周期的起始发生变化。TIMING EQUATION定义定时信息,即波形沿变化的时刻,它表示各引脚在一个周期内部4个驱动沿d1、d2、d3、d4(CCLK 引脚有 8 个驱动沿 d1、d2、d3、d4、d5、d6、d7、d8) 和 4 个比较沿 r1、r2、r3、r4 的位置。SPECIFICATION定义测试周期,这部分设置完成之后即代表4X模式设置完成。图3表示在4X模式下,在一个周期内采用RZ码的时钟引脚的输入逻辑值为“1111”,采用NRZ码的输入数据的逻辑值为“0110”,设置4个输出比较沿。

4.2 测试实现

基于ATE的FPGA在系统快速配置与完整的测试实现过程可以描述为:利用PC完成配置位流文件的生成;选择FPGA的从并配置模式,根据FPGA配置时序要求对控制脚的状态进行定义,得到所需的配置向量;利用ATE的4X配置方式将配置向量加载进测试机;对FPGA进行上电配置及测试。

图3 4X模式引脚设置

为了验证FPGA的4X配置方式下配置时间的优化效果,本文以Xilinx公司Virtex-7系列FPGA芯片XC7VX485T为例进行测试验证。测试过程中,选取一段LVCMOS15电平模式配置码对XC7VX485T进行配置时间的测试。XC7VX485T是一款千万门级FPGA,LVCMOS15电平模式下生成配置文件大小为410 Mb,如此大的数据量要求找到一种快速配置方式来满足向量深度以及测试时间的需求。基于ATE的一般配置方式、4X配置方式得到的配置向量如图4所示。其中每一行为一个周期,各数据脚并行加载,4X配置方式下每个管脚在一个周期内加载4位配置向量。由ATE按预定的测试时序,在芯片控制引脚以及数据引脚上送入测试图形,对待测器件(Device under test,DUT)进行测试。

基于ATE的一般配置方式、选择32位从并配置模式对FPGA进行在系统配置时,LVCMOS15电平模式下的配置时间为1.047 s,实验数据如图5所示。

图4 一般配置方式(左)、4X配置方式(右)下的配置向量

图5 一般配置方式测试结果

采用基于ATE的4X配置方式、选择32位从并配置模式对FPGA进行在系统快速配置时,LVCMOS15电平模式下的配置时间为271.329 ms,实验数据如图6所示。

图6 4X配置方式测试结果

实验数据表明,在一般配置方式下FPGA的配置时间达到1.047 s,对于需要反复进行“配置-测试”的千万门级FPGA而言,测试时间是难以接受的。采用4X配置方式,FPGA的单次配置时间由1.047 s压缩到271.329 ms,是一般配置方式的25.9%,配置时间减少了74.1%。该方法能显著减少配置向量的单次配置时间,是优化配置时间的有效方法,对于提高FPGA的测试效率、减少测试成本有很好的实用价值。

5 结束语

对于可重复编程的FPGA,测试时间包括每个测试配置的编程下载时间和对应加测试向量集的时间,配置时间远大于加测试向量的时间。为了提高在系统配置速度,本文从测试过程中配置时间开销的角度出发,实现了基于Advantest公司的V93000 SoC测试系统的4X配置方式,对单次配置时间进行了优化。与一般配置方法相比,配置时间减少了74.1%,解决了FPGA测试数据配置与测试时间的矛盾,研究结果可为高性能大容量FPGA测试配置提供一种新的方法。