基于RRAM的混合存储模型

2018-10-24钱育蓉侯海耀

杜 娇,钱育蓉,侯海耀,张 猛

(新疆大学 软件学院, 新疆 乌鲁木齐 830008)

0 引 言

面对大数据、云计算、物联网等信息技术发展产生的海量数据,传统的动态随机存储器(dynamic random access memory,DRAM)的内存设计逐渐无法满足需求[1],同时内存存储性能的提升远远落后于计算性能的提升[2],随之出现的是“存储墙”、“能耗墙”问题[3,4]。新型非易失性存储器(non-volatile memory,NVM)的出现,为解决上述问题提供了方向。现有的NVM主要有相变存储器(phase change memory,PCM)、阻变存储器(resistive random access memory,RRAM)、自旋转移力矩存储器(spin-transfer torque RAM,STT-RAM)[5,6]等,它们具有非易失性、漏电功耗低、存储密度高和扩展性强等特性,成为存储领域的研究热点,有望在未来取代传统存储器[7]。就目前而言,任何单一的存储器件都不能满足内存系统大容量、低成本和高性能的需求,较为有效的方法是采用混合存储的方式。它主要是从数据访问特点及负载特征出发,结合不同存储器件的特性,将请求发送给适合的存储设备,达到提高整个系统性能的目的,是目前存储技术的发展方向[8]。

本文基于DRAM和RRAM提出了一种混合存储模型,评测并分析该模型下内存系统的读写性能,实验结果表明,混合内存系统,性能优于完全以RRAM为主存的系统,接近完全以DRAM为主存的系统,同时DRAM与RRAM的容量配置及应用程序自身特点的不同,亦会对系统性能造成影响。

1 相关研究

目前将NVM用于混合存储的内存系统主要有3种结构:第一种是NVM完全取代DRAM作为内存;第二种是NVM与DRAM构成混合内存,但两者处于同一层次;第三种是NVM与DRAM构成混合内存,但DRAM与NVM是层次结构[9]。事实上NVM的写速率没有DRAM好,寿命也相对短些,因此第一种存储结构目前不适用。针对第三种存储结构,有学者采用STT-RAM和静态随机存取存储器(static random access memory,SRAM)混合进行缓存设计[10],缓存一般会被频繁访问,同时大部分应用程序的访问不是均匀分布的,而是存在明显的局部性和不均衡性,某一存储单元失效,将导致整个缓存的寿命下降,因此若要使用NVM架构缓存,存储单元的均衡访问是一个待以解决的问题。

因此本文采用第二种结构,DRAM和RRAM处于同一层次,利用软件来模拟RRAM的硬件行为,同时将读写延迟等结果返回。

2 DRAM与新型存储器的混合存储模型

2.1 动态随机存储器

DRAM是易失性存储器的代表,具有速度快、寿命长等特性,是目前最受欢迎的计算机主存设备,其每年市场容量几乎占整个全球集成电路市场的1/10[11]。DRAM通过电容两边电荷的多少表示数字“0”或“1”,达到存储数据的目的。目前有两个主要因素限制了单独使用DRAM作为内存的进一步发展。第一是DRAM的工艺制程已接近极限,存储密度难以提高。第二是电容存在漏电现象,会导致电荷丢失,因此需要进行周期性刷新来保证数据完整[12]。

本文在所构建的混合存储模型中,利用DRAM良好写速率,完成大部分的写工作,弥补RRAM较大写延迟问题,从而提高系统的整体性能。

2.2 阻变存储器

RRAM存储数据信息的方式是基于阻值变化的,它利用薄膜材料在不同电激励的作用下出现高低阻态之间的可逆转变现象来进行数据存储,不需要刷新操作,空闲时不耗能。其结构简单,由金属-介质-金属构成,有利于实现三维的高密度集成。国际半导体技术路线图组织(international technology roadmap for semiconductors,ITRS)在其2013年度报告中指出,将成为下一代存储器中最有力的候选者[13]。

表1从单元存储密度、容量、读写延迟、耐久性、写能耗和易失性几个方面出发,将RRAM与常用存储器件NAND Flash,DRAM进行了对比。

表1 常用存储技术比较

从单元存储密度上来看,RRAM的存储密度高于DRAM的存储密度,从容量上来看,RRAM的容量远远大于DRAM,虽然NAND同样具有容量大的优点,但NAND具有较大的读写延迟;从耐久性来看,RRAM的耐力通常可以达到106,在70 ℃高温下数据仍可保持十年,介于NAND和DRAM之间,更长的耐力已经被报道(例如109),耐久性测试受基准测试程序集选择的影响;从易失性上来看,NAND和RRAM属于非易失性存储器,而DRAM是易失性存储器。

本文主要利用RRAM存储密度高、容量大这一特性,同时RRAM具有非易失性,掉电后仍能够保存数据,有效地保障了系统数据的安全性。在所构建的混合存储模型中,通过使用较少DRAM与RRAM混合,在保证系统性能的同时,亦提高了其存储密度。

2.3 混合内存结构设计

如图1所示,设计混合内存体系结构,通过设计一个内存管理控制器来管理数据的访存,该控制器实现地址映射、命令生产、读写调度等功能。每一个内存数据读写请求,都需要经过内存控制器,本文通过不同的通道实现混内存的支持,设置两个通道,一个通道中模拟DRAM,另一个通道中模拟RRAM。为DRAM和RRAM分别设计存储管理模块,二者的地址空间是分别独立的,任何时候一个数据页只能存在于一个设备上。内存控制器维护DRAM和RRAM的分区列表,根据请求地址将请求发送到相应的内存。

图1 混合内存体系结构

图2展示了引入RRAM后内存控制器中请求下发的流程,当内存访问请求到达时,内存控制器对访问请求进行解析,获得请求类型、地址、大小等信息,根据请求类型不同做相应的操作。当请求类型为写请求时,我们优先考虑是将请求发送给DRAM,同时当读操作发生缺页中断时,缺页中断程序从磁盘读取请求页时,优先考虑将请求页写入DRAM中,这样做的目的是减少RRAM的写次数,因为RRAM具有较高的写延迟(相对于DRAM)。

图2 引入RRAM后内存控制器中请求下发流程

3 实 验

3.1 模拟器及其配置

在混合内存系统中,不仅需要模拟DRAM的行为,还需要模拟RRAM,同时需要一个混合内存控制器来负责调度上层下发的请求,并将执行完的数据返回给CPU。因此,本文在GEM5和NVMain的基础上,构建DRAM-RRAM混合内存模拟器。

表2列出了混合内存模拟器基本配置及内存的参数信息。本文中在各个内存级别的调度算法一致,都采用FR-FCFS(first-ready,first-come,first-serve),默认内存地址映射策略是scheme1,单个RRAM芯片的容量设置为256 MB,单个DRAM芯片的容量设置为512 MB,内存总容量为4 GB。

表2 模拟器基本配置

3.2 基准测试程序集及其特征

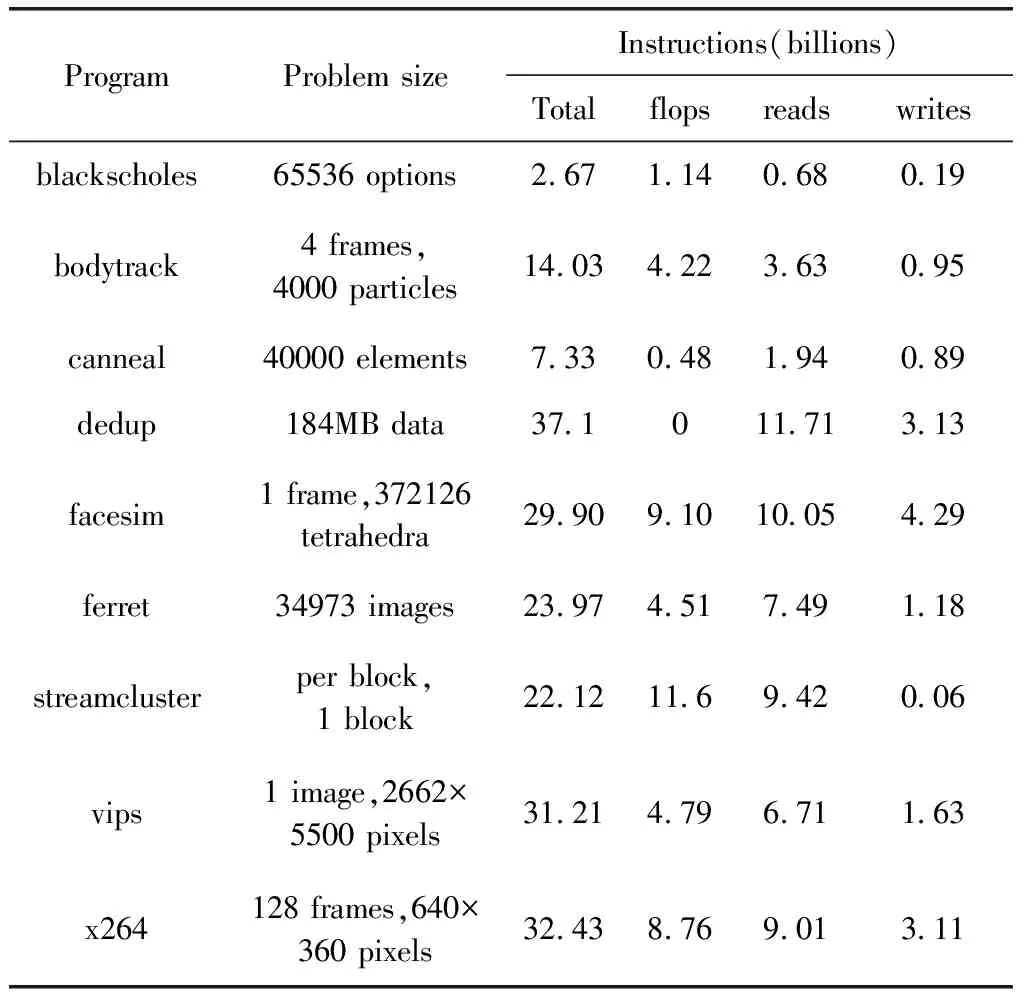

本文采用的基准测试程序集是PARSEC[14],该测试集由多线程应用程序组成,具有一定代表性。从中选取9个不同测试程序,测试程序的输入集选取simMedium进行实验,其特点见表3。

表3 测试程序集的特点

3.3 实验性能分析

实验中设计了3种内存结构,分别为4G容量的DRAM、4GB容量的RRAM和2GB DRAM+2GB RRAM,首先通过模拟器单独在DRAM设备和RRAM设备上运行上述测试程序集,获得单个设备的性能,然后在混合存储设备上运行同一测试集。

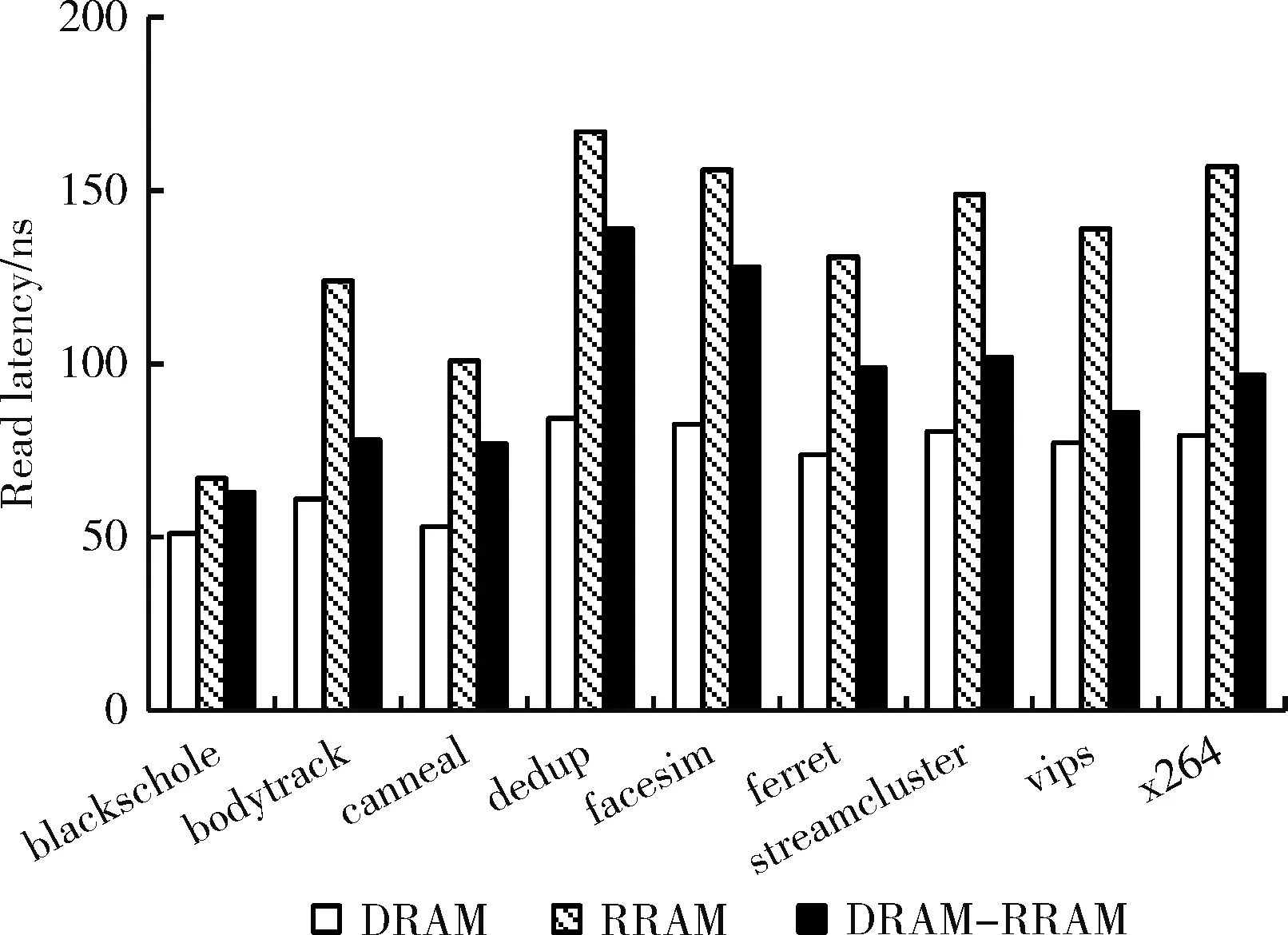

实验1:不同应用程序在不同内存结构下的平均读延迟

本实验主要是为了测试不同内存结构下,不同应用程序的读延迟情况,实验采用3.2节中的基准测试程序。

如图3所示,我们可以看出,在DRAM内存结构下,所有应用的平均读延迟最小,同时DRAM-RRAM内存结构下的平均读延迟小于RRAM内存结构,这是因为DRAM本身的读延迟小于RRAM。

图3 不同应用程序的平均读延迟

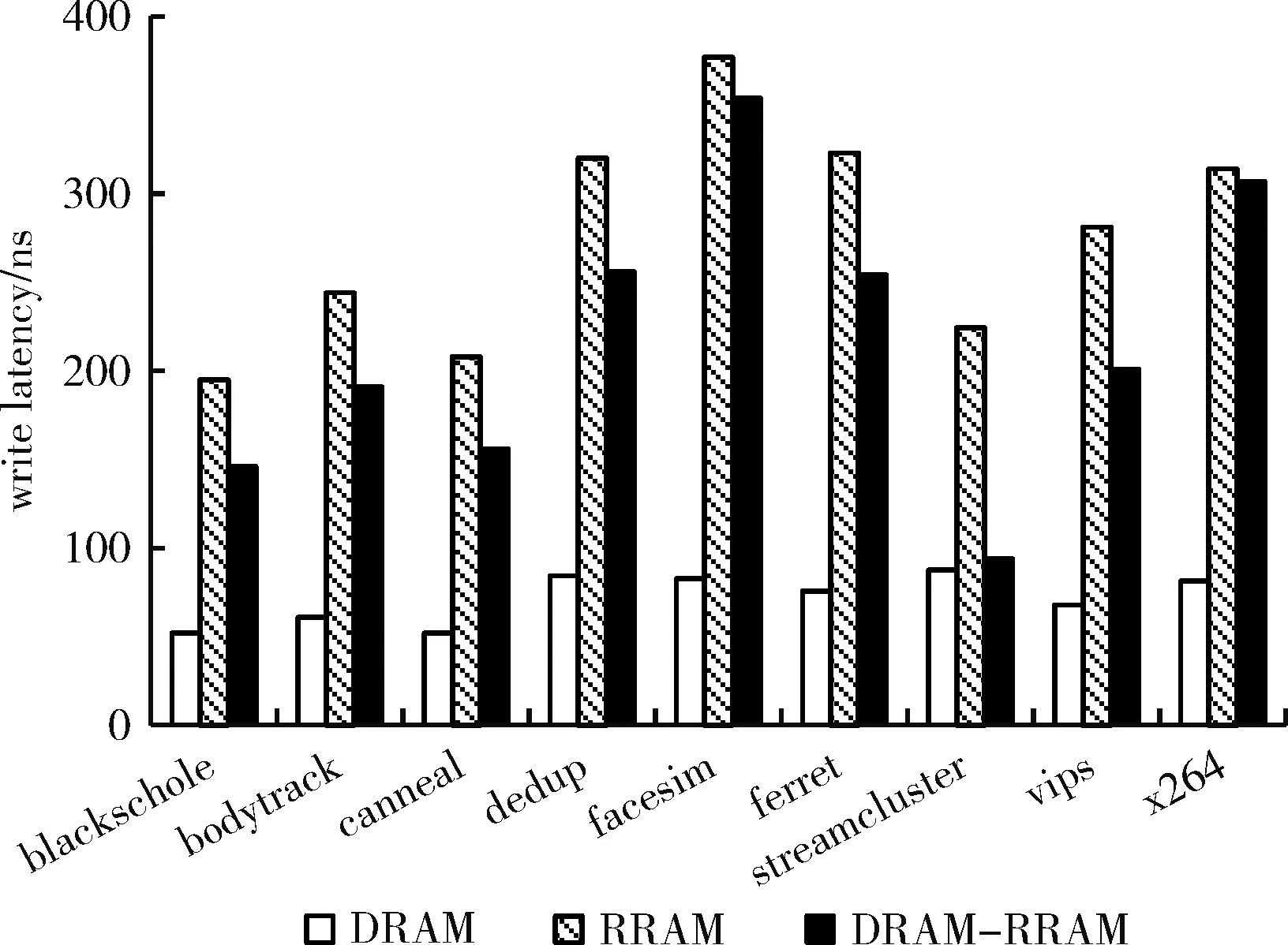

实验2:不同应用程序在不同内存结构下的平均写延迟

本实验的主要是为了测试不同内存结构下,不同应用程序的写延迟情况,实验采用3.2节中的基准测试程序。

图4展示了在3种不同内存结构下不同应用的平均写延迟。应用程序streamcluster在DRAM内存结构下和在DRAM-RRAM内存结构下,写延迟非常接近,这是因为streamcluster的写请求非常少,也就是说对于写操作非密集的应用程序而言,混合内存的结构基本不会影响其写性能。对于应用程序facesim和x264,没有体现出DRAM-RRAM混合内存结构中DRAM写操作快的优势,反而体现出RRAM写延迟较大的缺陷,这可能是由于这两个应用程序发送的写操作请求发送到RRAM上较多,发送到DRAM上比较少导致的。对于其它应用,DRAM-RRAM混合内存的延迟小于RRAM,这正体现出了DRAM写延迟小的优势。

图4 不同应用程序的平均写延迟

通过实验2和实验3,我们可以得出,2GB DRAM+2GB RRAM混合存储模型读写性能优于单独使用RRAM内存设备,当应用程序属于写密集型应用时,混合内存的优势体现的更加明显。

实验3:不同内存容量配置对内存系统性能的影响

为了分析混合存储设备DRAM与RRAM内存不同容量配置对内存系统性能的影响,设置了4组不同容量的内存结构,分别为4GB DRAM、1GB DRAM+4GB RRAM、1GB DRAM+8GB RRAM、1GB DRAM+16GB RRAM,测试程序选取上述测试集中具有代表性的blackscholes、streamcluster和facesim。blacksscholes仅含26.7亿条指令,facesim含299亿条指令,streamcluster含221.2亿条指令,同时属于写操作非密集的应用。实验中我们没有对RRAM单独作为内存结构时的情况进行研究,因为RRAM有较大的写延迟,其性能明显比DRAM作为内存时差。

如图5所示,在测试程序blackscholes、streamcluster、facesim下,随着RRAM容量的增加,程序运行时间逐渐减小,其中当内存采用1GB DRAM+16GB RRAM结构时,其性能与4GB DRAM时的性能相当。

图5 不同内存容量下应用程序的运行时间

4 结束语

制约DRAM内存系统发展的主要因素是容量和能耗,与DRAM相比,NVM具有存储密度高、扩展性强、非易失性等优势,而NVM的读写性能、耐久性略逊于DRAM。本文基于GEM5和NVMain构建了DRAM-RRAM混合内存模拟器,通过测试其在程序集PARSEC下不同应用的平均读写延迟,得出混合内存的读写性能优于单独使用RRAM的内存系统,略差于DRAM作为内存结构时的性能,但RRAM的引入大大提高了内存系统的存储密度。在此基础上,选取测试程序集下不同的应用程序,配置不同混合内存容量,发现对系统性能亦造成不同程度的影响。为了更好地提高混合内存结构中NVM的耐久性,降低其写功耗,还需进一步的工作。