基于FPGA的数字化MSK载波同步设计与实现*

2018-10-15王永斌付天晖

刘 华,王永斌,付天晖

(海军工程大学 电子工程学院,湖北 武汉 430000)

0 引 言

针对甚低频(VLF)通信过程中报文速率低、频带窄、噪声干扰大等问题,通常采用包络恒定、相位连续、带外衰减小、能量集中的MSK调制。而MSK调制的解调多采用相干解调,需要在接收端生成一个相干信号。相干信号一般可通过锁相环产生。目前,大多数锁相环采用分立元件和专用集成芯片构建。然而,分立元件会导致设备体积增大,专用集成芯片使用过程中灵活度不足,不能够根据输入与输出需求进行编程调整,造成使用不方便[1]。随着FPGA的不断发展,FPGA在数据处理方面的能力急速提高,且具有可编程的特点,通过修改设计参数编程,可以按照需求控制性能。

本文基于FPGA平台,采用Verilog语言和模块化的设计思想,对锁相环进行数字化设计,完成了对MSK信号的载波同步解调。

1 方案选择

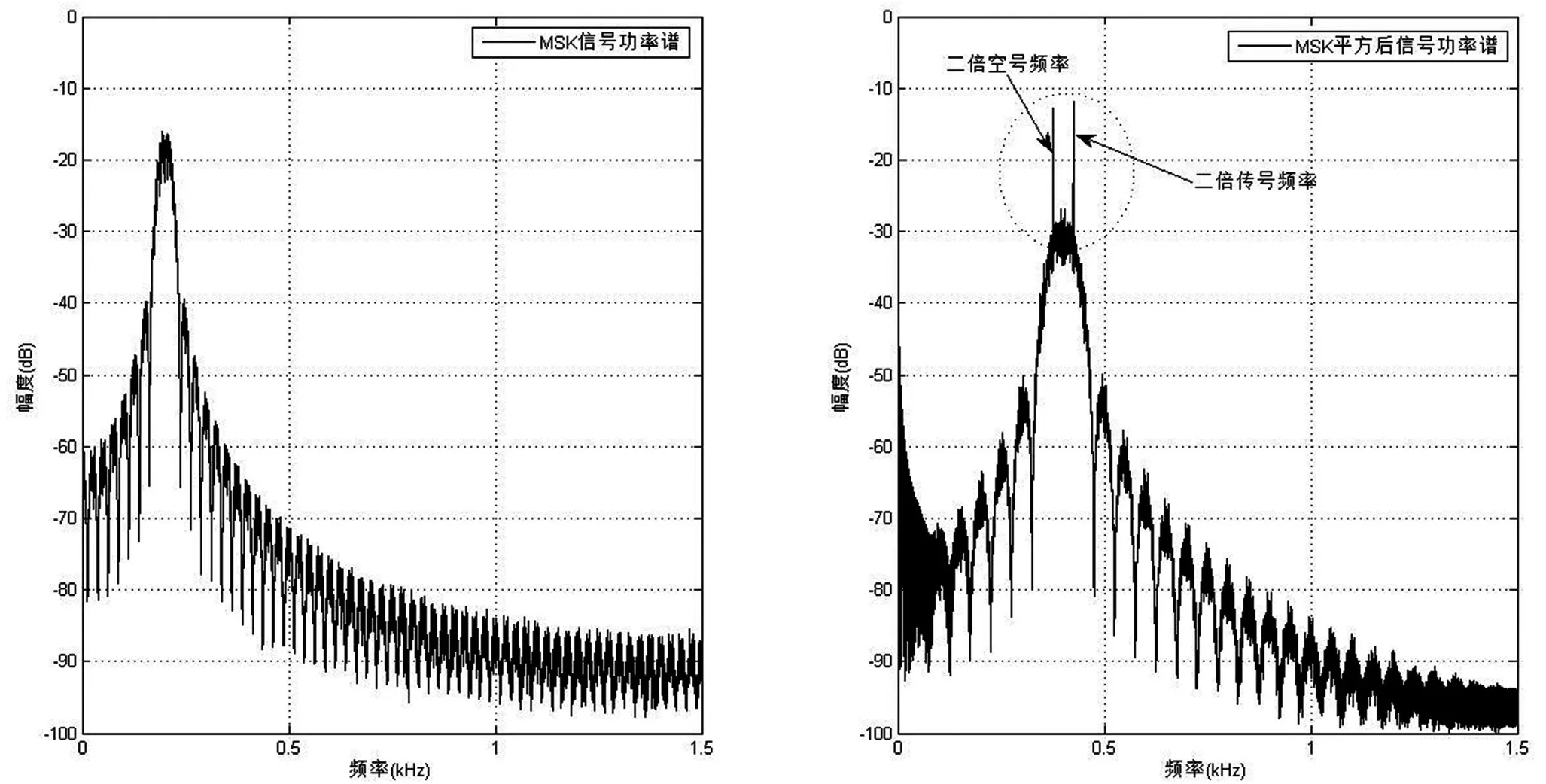

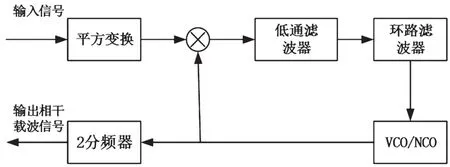

针对不同调制方式和信号的特点,必须采用不同形式的锁相环来提取同频同相信号。对本文的MSK调制进行变换,观察功率谱可以发现,功率谱中并不存在离散的频率分量,因而锁相环不能对MSK信号进行锁定[2]。而对其平方后可以发现,功率谱中出现两个离散的频率分量,如图1所示。通过计算分析可知,这两个尖峰为MSK调制信号中的2fH和2fL,可见,平方后的MSK信号含有导频信息。因此,可以利用锁相环对二倍传号频率2fH和2fL分别进行锁定,然后分频得到需要的载波信号。

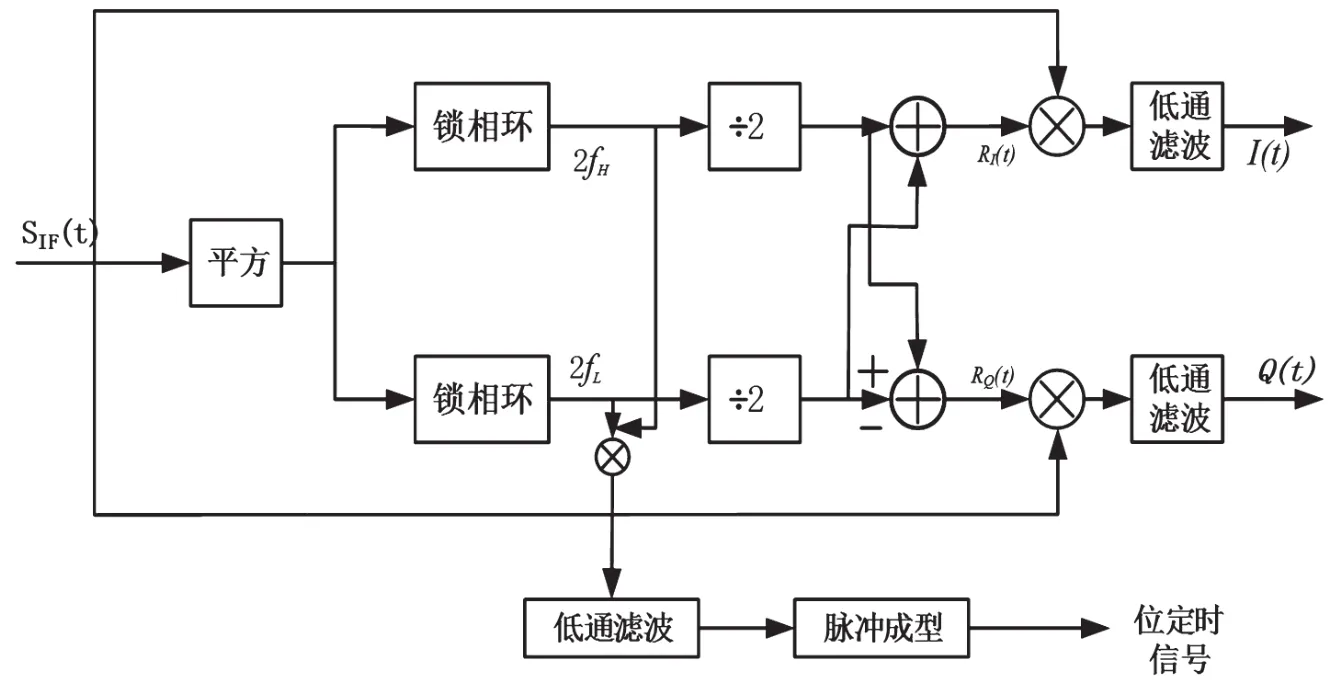

针对MSK信号的这个特点,本文采用平方环对MSK信号进行相干解调,如图2所示,利用MSK信号平方后出现的导频信息,通过滤波器将导频信号分别滤除,并将其送入锁相环进行锁定,通过数学运算生成相干信号与MSK信号进行相乘,最后通过滤波得到IQ信号,完成载波同步。

图1 MSK原信号与平方后的功率谱

图2 平方环载波同步

2 锁相环结构分析及数字化设计

2.1 锁相环结构分析

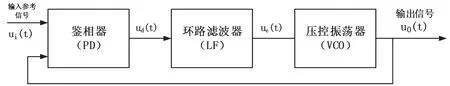

锁相环电路由三部分组成:鉴相器(PD)、环路滤波器(LF)以及电压控制振荡器(VCO),如图3所示。

图3 锁相环基本组成

鉴相器作为相位比较装置,用来检测输入信号相位θ1(t)与反馈信号相位θ2(t)之间的相位差θe(t),并将相位差转化为一个电压差。

环路滤波器具有低通特性,且应留有充足的相位裕度。环路滤波器对锁相环的调节时间和稳定后的允许误差都具有很大影响。

压控振荡器是一个电压—频率变换装置,需要随输入控制电压uc(t)的变化而改变输出的频率,且是一个线性变化过程。变换关系为:

式中ωv(t)是压控振荡器的瞬时角频率,Ko为控制灵敏度或增益系数。

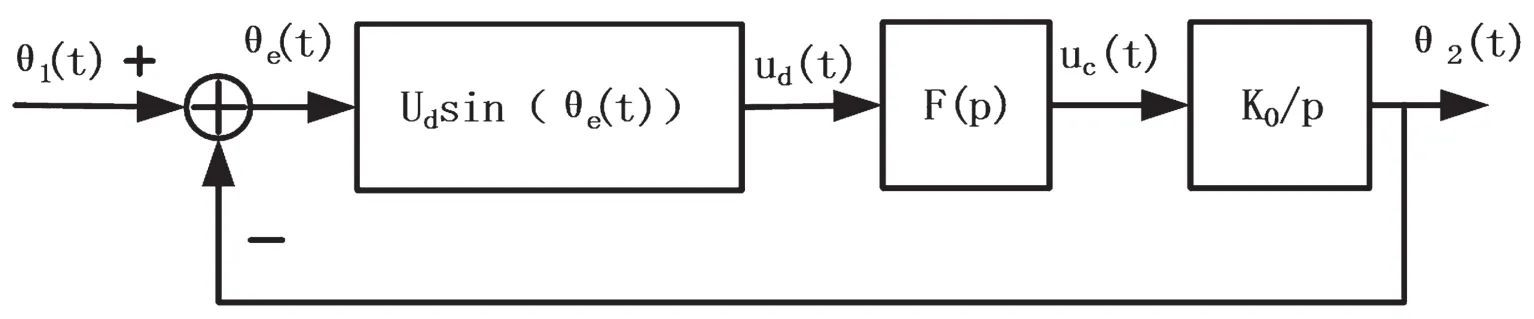

根据上述讨论,得到了锁相环电路的三个部分模型,按照图3结构,可以得到整体的锁相环路的相位模型,如图4所示。

图4 锁相环的相位模型

锁相环是一个相位负反馈的误差控制系统。控制过程为:利用鉴相器中的混频器,使输入相位减去反馈输入的相位得到误差相位θe(t),通过低通滤波器使误差相位产生误差电压ud(t);误差相位经过环路滤波器F(p)产生误差电压uc(t);控制电压加到压控振荡器上使之产生频率偏移,跟踪输入信号频率ωi(t);若输入ωi(t)为固定频率,在uc(t)的作用下,ωv向ωi(t)靠拢,一旦达到两者相等,若满足一定条件,环路稳定达到锁定[3]。锁定后,被控的压控振荡器频率与输入信号频率相同,两者之间维持一定的稳态相位差[4]。

2.2 锁相环数字化设计

鉴相器采用正弦鉴相器,即乘法器和低通滤波器串联而成。乘法器与低通滤波器在FPGA中都易于实现,压控振荡器利用Quartus软件中提供的NCO IP核。

环路滤波器对锁相环电路性能具有很大影响,在工程实践中,使用最多的是理想二阶环路滤波器。理想二阶环路滤波器(理想积分滤波器)系统函数为:

利用双线性变换对其进行数字化,得到:

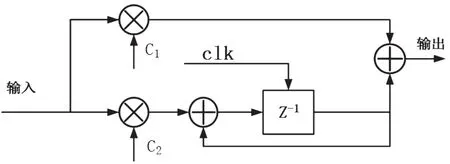

根据系统函数可以得到环路滤波器的系统结构,如图5所示。鉴相器输出的信号中具有直流分量和交流分量,而只有直流分量才是控制VCO需要的数据,因此环路滤波器应具有低通特性,以滤除交流分量[5]。

图5 数字环路滤波器结构

设NCO的数字化传输函数为[6]:

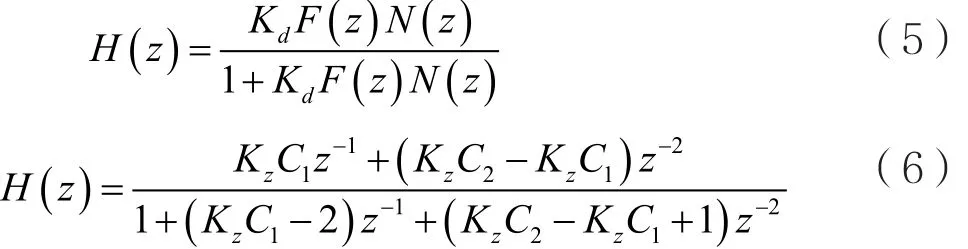

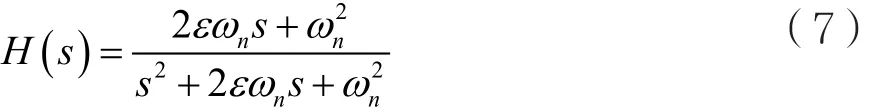

将式(4)、式(3)代入锁相环传输函数式(5),可得到式(6):

其中Kz=KdK0´。

理想二阶环路的系统函数为:

进行双线性变换,可得:

于是,有:

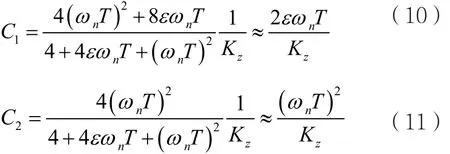

显然,式(6)和式(9)应该相等,令ωnT ≪1,则有:

C1和C2的取值对锁相的调节时间和允许误差具有很大影响。在FPGA设计中,为了便于乘除系数,通常需对C1和C2进行量化,使之成为2的倍数,从而使FPGA可通过移位实现乘除。

3 模型优化

平方环中锁相环部分电路原理,如图6所示。对于甚低频这样一个窄带信号,实际过程中带通滤波器获取的增益并不大,而设计一个窄带的带通滤波器却很耗FPGA资源,因此在此省略了带通滤波器。

图6 平方环提取载波原理

由于平方环锁定的是二倍频2fH和2fL,因此需要对输出的正弦信号进行二分频才能得到需要的fH和fL。然而,对正弦信号进行分频十分复杂。为了解决这个问题,通常采用如图7所示的方法解决这个问题[7],即利用NCO产生两路正交的正弦信号,将两路信号相乘产生2倍频的载波信号,将两倍频接入鉴相器,将同相信号直接输出,即为相干载波信号。

图7 改进的平方环提取载波信号原理

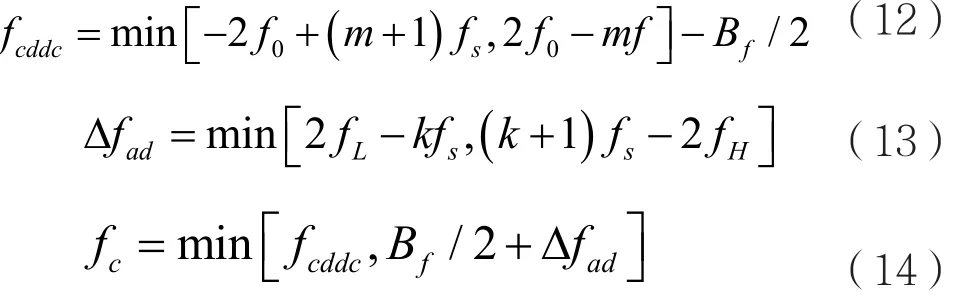

设计过程中,另一重点是滤波器通带和截止频率的确定。滤波器的好坏对最后锁定影响巨大。对于鉴相器中的低通滤波器,通带必须大于捕获带频率,而截止频率应不大于2fH-2fL。对于载波与MSK信号相乘后的低通滤波器,通带频率一般设为同相支路数据速率,而截止频率一般可由式(12)、式(13)、式(14)估算[8]:

其中Bf表示中频信号处理带宽,fs表示系统时钟,m为整数,fc为所求截止频率。

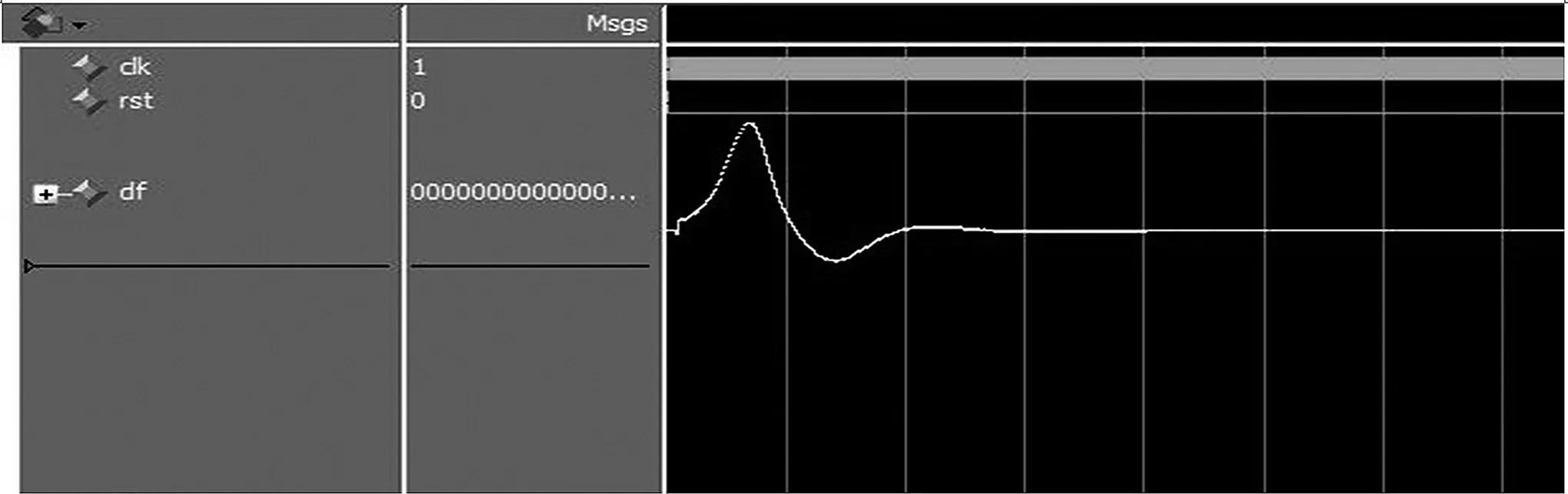

4 实验仿真

首先对锁相环进行单独仿真,结果如图8所示。观察图8中环路滤波器的输出频差df,可以看到锁相环的调节过程为先振荡后趋于稳定,且稳定后相位差波动很小。改变环路滤波器中C1和C2的值,对环路滤波器调节作用进行仿真,得到如下结论:在锁相环锁定范围内,C1若减小,会降低最后的频偏允许误差;若加大C2的值,会减小锁定时的调整时间。因此,可通过更改C2和C1的值来平衡误差精度和锁定时间。

图8 锁相环锁定后频差变化

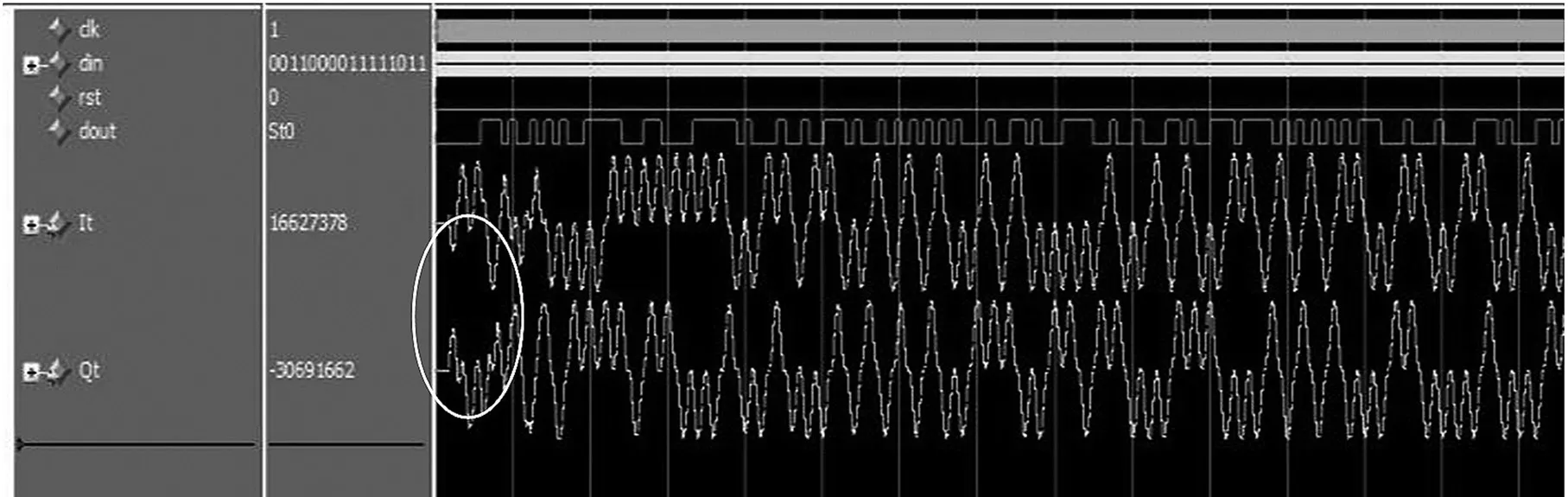

将该锁相环置于平方环中,对MSK解调过程进行仿真,结果如图9所示。从图9的圆圈处可以看出,开始信号没锁定时,IQ两路载波解调并不完美,随后锁相环锁定时IQ两路信号越接近理论。经过后期实际工程验证,该锁相环工作效果良好,解调出的码元正确。

图9 MSK解调IQ输出

5 结 语

本文通过分析锁相环电路原理,对锁相环各部分进行数字化。采用平方环对MSK信号进行载波同步,通过modelsim进行仿真验证。仿真结果表明:锁相环锁定效果良好,能够正确产生相干信号,在频差不大于快捕带范围的情况下,锁定时间满足工程需求。