一种基于FPGA的短波数字接收机设计与实现*

2018-10-15杨建平袁凤国

李 路,杨建平,袁凤国,罗 磊

(中国电子科技集团公司第三十研究所,四川 成都 610041)

短波通信以其传输距离远、无需中继、配置灵活、快速部署以及抗毁、抗干扰等特性,一直是战略通信的主要手段,在军事通信中始终占有重要地位。经过多年的发展,除了具备基本的模拟话音通信能力外,短波电台已经由传统的模拟电台逐渐向带宽更宽、跳速更快、扩展功能更加多元化的数字化电台发展。

一般而言,数字化的实现是通过采样得到的。短波数字接收机作为短波电台的主要组成部分,其性能直接影响整个系统的性能好坏。目前,短波数字接收机的设计方案很多,主要的区别在于对射频前端信号的处理。对射频信号的数字采样一般分为三种:射频低通直接采样、射频带通采样和宽带中频采样[l]。根据奈奎斯特定理,采样速率Fs应满足Fs≥2fmax,这样得到的采样信号才能被准确还原。其中,Fs为采样频率,fmax是被采样信号的最高频率。短波信号的频段在3~30 MHz。如果采用直接射频低通采样,要满足奈奎斯特采样定律,那么采样速率Fs要在60 MHz以上[2]。这要求DSP/FPGA处理器有很高的处理速度,以进行后续的数字信号处理,而目前的处理器实现起来较为困难。根据带通采样原理,如果fmax≥ fmax-fmin,信号的最高频率大于信号带宽时,要准确还原采样信号,采样速率必须满足Fs≥2( fmax-fmin),即采样率大于信号带宽的2倍。其中,fmax是被采样信号的最高频率,fmin为信号最低频率。这种处理方法可以大大降低采样率。但是,带通信号存在于不同的频带内,每个频带都对应一个中心频率,所以如果采用射频带通采样方案,带通采样前,需经过相应中心频率的滤波处理,否则会发生信号混叠失真[3]。由此可见,射频带通采样虽然可以大大降低采样率,但是额外带来了不同中心频点的带通滤波处理需求。

宽带中频数字化的工作原理是,在模拟前端采用多次混频体制,得到一个固定中心频率的中频信号。即首先将信号上变频到一个高中频抑制干扰和实现大动态范围AGC,之后将信号下变频到规定输出的中频,然后将混频后的信号模数转换成数字信号,再送入DSP/FPGA等处理器完成下变频滤波和解调[4]。经过多次混频不仅可以优化ADC的动态范围和改善带宽,而且此结构得到的是中心频率固定、带宽适中的宽带中频信号。这样处理不仅大大降低了DSP/FPGA的处理速度,而且没有增加额外的滤波结构,复杂度相对最低。综合实际情况考虑,认为这是最现实的实现方案。

1 设计思路

1.1 宽带中频数字采样结构

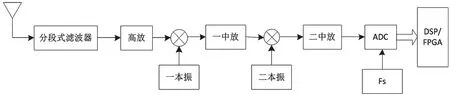

A/D变换前的电路主要由混频器、滤波器和中频放大器组成。宽带中频采样数字结构如图1所示。

图1 宽带中频采样数字结构

本方案中,A/D变换模块前面的部分通常叫做射频前端。首先,将天线接收的射频信号利用本地频率振荡器混频,得到一个高中频信号抑制干扰和实现大动态范围AGC。其次,将信号通过第二个频率振荡器再次混频,得到一个频率合适后续数字器件处理的宽带中频信号。再次,此中频信号经过专门的ADC转换芯片得到数字信号,进入DSP/FPGA数字处理器进行处理。最后,经过DSP/FPGA模块对采样的数字信号进行下变频和解调,就可以恢复出原始的基带信号。本方案采用FPGA进行下变频和解调处理。

1.2 数字接收处理模块

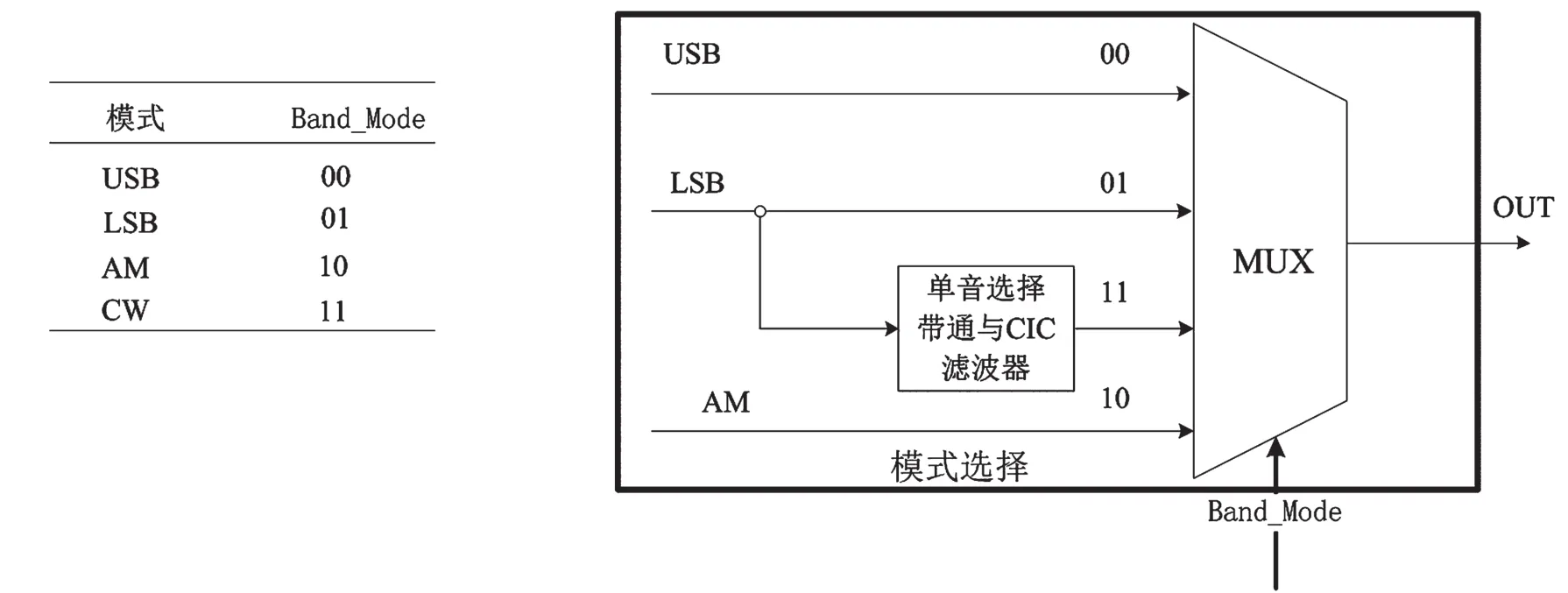

数字接收处理模块将中频ADC采样信号进行下变频处理和边带恢复,结构如图2所示。

图2 数字接收机处理模块

各模块功能说明如下。

DDC:完成频谱搬移、抽取、滤波等操作,得到相关频谱的I/Q两路基带信号。

希尔伯特(Hilbert)变换:对DDC输出的I/Q两路基带信号进行Hilbert滤波。

单边带解调:对Hilbert滤波输出的I/Q两路基带信号对信号进行加减运算实现上下边带切换,输出LSB与USB基带信号。

AM解调:对来自DDC输出的I/Q两路基带信号进行包络检波和AM解调,输出AM基带信号。

模式选择:通过控制位进行解调模式选择,根据模式不同,分别输出USB、LSB和CW/AM信号。详细结构如图3所示。

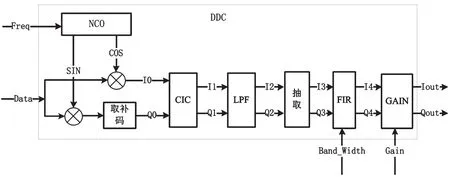

其中,DDC模块的详细设计,如图4所示。

图3 模式选择模块详细设计

图4 DDC模块详细功能

(1)DDC抽取倍数

中频采样频率4.915 2 MHz,基带信号采样频率为9.6 kHz,抽取倍数为512。

(2)抽取滤波器

为了实现512倍抽取,需要多级级联的抽取滤波器,包括CIC滤波器、半带滤波器和FIR低通滤波器。其中,CIC抽取滤波器由三级级联实现,各级抽取倍数分别为8-4-4,总共抽取倍数为128倍。半带滤波器19-tap,处理时钟频率38.4 kHz,2倍抽取。FIR低通滤波器加Blackman窗,255-tap,截止频率3.6 kHz,处理时钟频率19.2 kHz,2倍抽取。

各模块功能说明如下。

NCO频谱搬移:根据混频器配置信息,通过信号发生器NCO产生正弦信号和余弦信号,将通道输入的信号与正弦、余弦信号进行相乘,完成频谱搬移操作。

CIC滤波器:系统中的CIC滤波器主要完成6倍的内插/抽取过程中的抗混叠滤波。

LPF低通滤波器:低通滤波器完成低通滤波,提取基带信号,采用Xilinx自带的滤波器IP核实现。

抽取模块:抽取模块完成6倍的抽取。

FIR滤波器:下变频模块均需要两路基带低通FIR滤波器,满足64 kb/s下的3~25 kHz的基带带宽。

GAIN增益控制:输入增益系数Gain与基带数据,将基带数据与增益系数Gain相乘,得到输出基带数据。

2 设计保证

为保障总体方案提出的性能指标,对业务模块中的关键单元进行参数设计。

数字解调中抽取滤波来实现频谱搬移和频谱抗混叠,后端低通滤波为带外噪声抑制滤波器。在模拟信号输出时,边带对消单元消除边带影响。CW输出时,增加窄带带通滤波。该过程中重点设计带外噪声抑制低通滤波器、窄带带通滤波器,而边带对消滤波采用Hilbert即可实现所需要求。

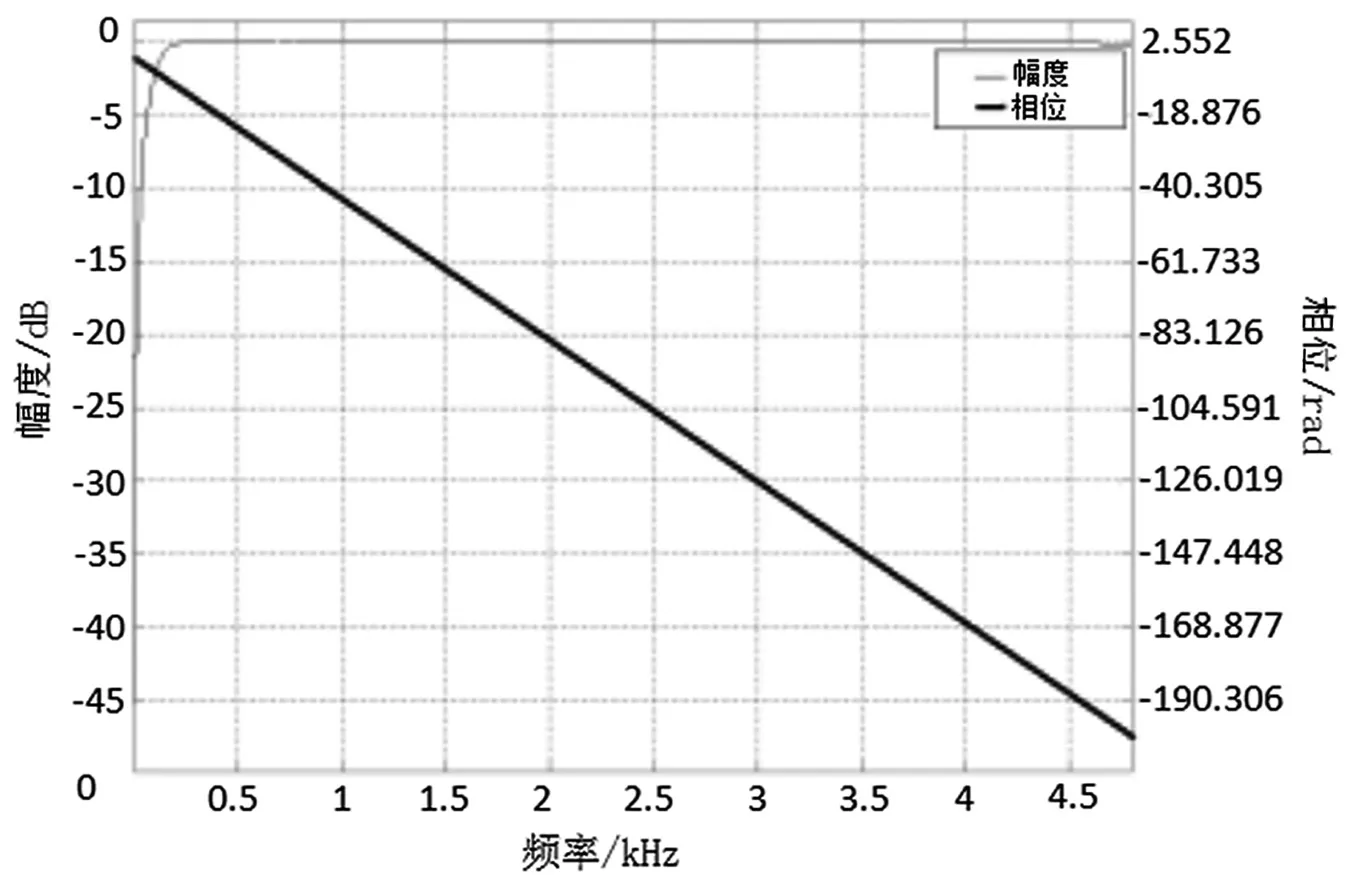

2.1 低通滤波器

在通常的数字解调中,保证带外干扰低于有效信号40 dB就能满足数字解调要求。这里设计采用63阶实现带外抑制大于40 dB的衰减。设计低通滤波器的幅度相位响应如图5所示。

图5 低通滤波器幅度相位响应

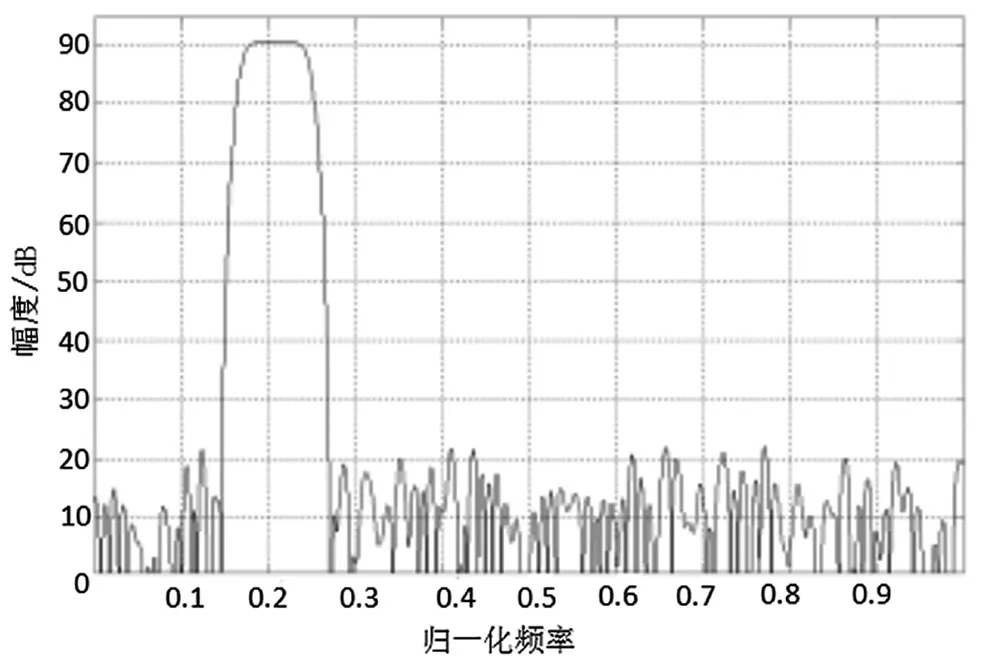

2.2 窄带带通滤波器

根据短波电台中的对CW解调带通滤波器的指标,通带(3 dB)200 Hz,过度带200 Hz,阻带衰减60 dB,设计窄带带通滤波器幅频响应如图6所示。

图6 窄带带通滤波幅频响应

滤波器设计阶数为255,过渡带为200 Hz,中心频率为1 kHz,带宽200 Hz。

2.3 Hilbert滤波器

IQ分解单元主要是对模拟采样信号的IQ正交分路和模拟采样信号低端噪声对边带和载波的抑制,关键是对Hilbert滤波器与带通滤波器的参数设计。

Hilbert滤波器为相移网络,带外的衰减很小,带内的增益影响到IQ信号的正交性。如果正交性能得不到有效保障,会导致边带抑制不够。根据以往工程开发经验,Hilbert带内衰减增益必须达到

10 -4 dB以上。

Hilbert滤波器带外衰减导致与原来应该输出的I路信号失去幅度和相位的正交性,带外低端的噪声会在IQ对消时导致泄露过大。所以,原采样信号进行带外的噪声抑制,使其带外干扰尽可能小。Hilbert滤波器设计为127阶,幅度与相位响应如图7所示。

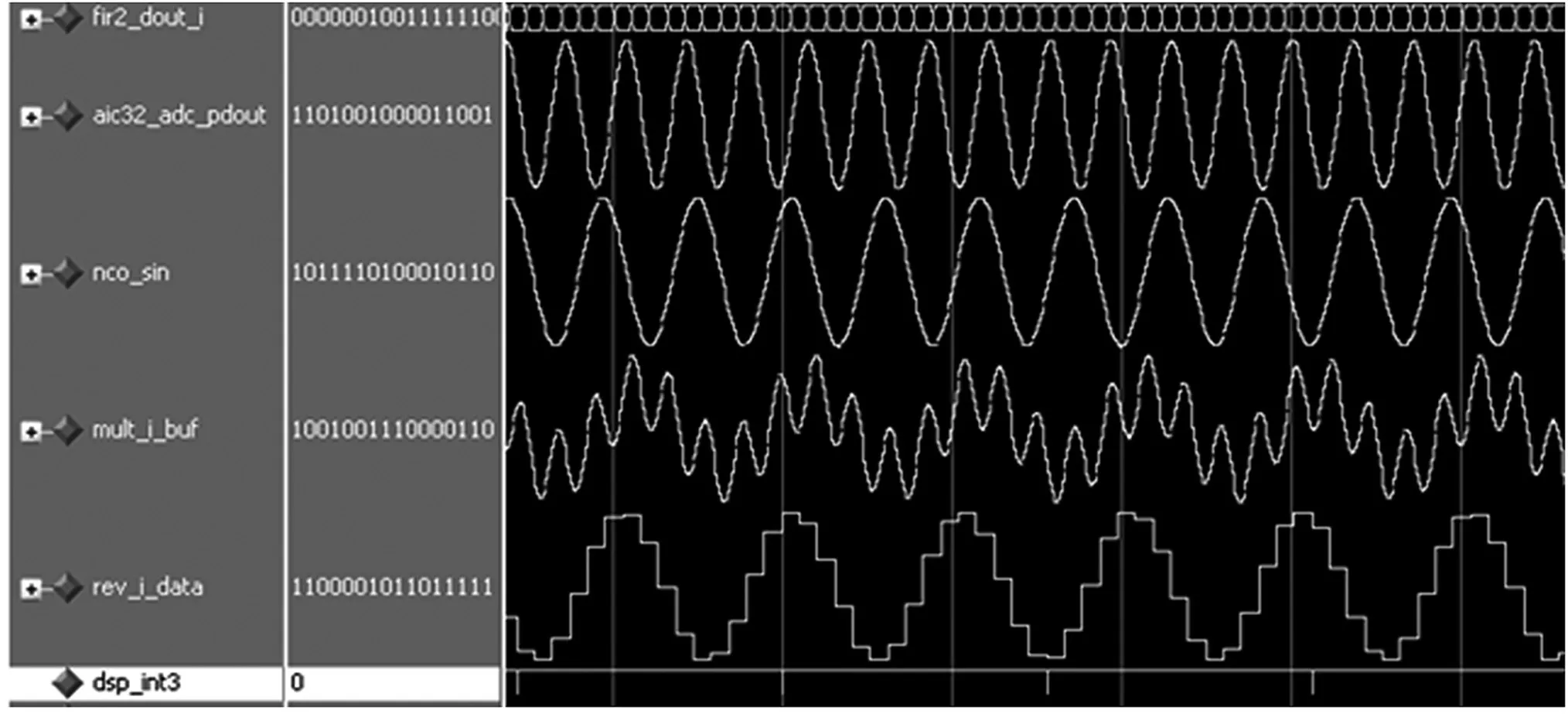

3 FPGA实现

采样后的数据处理工作都在FPGA中完成。为了保证充足的硬件资源和处理速度,FPGA选用Xilinx的FPGA,选用XC6SLX150芯片。FPGA程序采用VHDL语言编写,主要完成中频处理和时序控制的设计。在功能仿真阶段,模拟中频输入2.8 kHz接收信号,NCO为1.8 kHz本地载波,实现了1 kHz单音信号的分离与下变频,仿真结果如图8所示。

图7 Hilbert滤波器幅度相位响应

图8 FPGA功能仿真

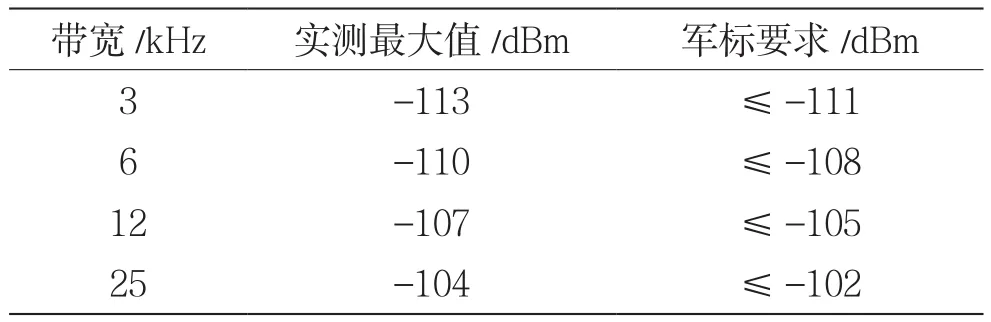

系统经调试成功后,在接收机实物上进行了性能测试。

试验方式。接收机收/发口连接射频信号发生器,中控口与音频分析仪连接。接收机收模式设置为USB,带宽设置为3 kHz。射频信号发生器产生工作频率+1 kHz射频信号,调整输出信号电平,使音频分析仪SINAD为10 dB,记录此时射频信号发生器输出信号电平d,d即为该频率模拟灵敏度。更换工作带宽和接收频率,记录不同带宽和频率的测试结果。

试验结果。本次试验共测试了3 kHz、6 kHz、12 kHz、25 kHz共4种带宽,每种带宽在2~30 MHz的频率范围内以1 MHz为步进进行测试。3 kHz带宽下,测试数据最大值为-113 dBm;6 kHz带宽下,测试数据最大值为-110 dBm;12 kHz带宽下,测试数据最大值为-107 dBm;25 kHz带宽下,测试数据最大值为-104 dBm。对照国军标GJB 367A-2001关于短波接收机的灵敏度指标,满足要求,具体如表1所示。

表1 接收机灵敏度实测数据

4 结 语

基于FPGA的数字接收机性能比模拟接收机性能有很大提高,且具有很强的适应性,可灵活配置,容易实现宽带和多信道化,为现代接收机提供了一种高性能的接收机解决方案,具有广泛的应用前景。