一种基于蓝牙通信的FPGA无线下载器设计

2018-09-20周清文殳国华黄冠

周清文,殳国华,黄冠

(上海交通大学 电子信息与电气工程学院,上海 200240)

0 引 言

目前,可编程器件(如CPLD、FPGA)由于其高性能及灵活可配置性,得到广泛的应用。开发人员在对其开发时,都需要专用的有线下载器对其进行配置,或者需要在器件周围设计专门的配置电路,这在一定程度上增加了设计的难度与成本。可编程器件都具有在系统可编程性,并且兼容边界扫描功能(JTAG)[1]1,这使得使用微控制器更新、修改器件配置极为方便。本文针对Xilinx公司可编程逻辑器件FPGA芯片,基于蓝牙通信并利用ARM处理器,设计了一种实现无线配置FPGA的下载器。

1 JTAG原理

1.1 JTAG概要及时序

JTAG(Joint Test Action Group,联合测试工作组),是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片(主要是复杂的集成芯片,如微处理器、DSP、FPGA和CPLD)内部测试。其基本原理是在器件内部定义一个TAP(Test Access Port,测试访问口)通过专用的JTAG测试工具对内部节点进行测试[2]。在芯片正常工作时,边界扫描单元对于芯片内部电路是“透明”的,所以不会影响芯片电路的正常工作与信号传输。

IEEE 1149.1 标准规定了一个四线串行接口(第五条线是可选的):

TCK:边界扫描逻辑测试时钟;

TMS:测试模式选择,用于驱动TAP控制器的状态;

TDI:测试数据输入,数据在TCK上升沿采样进入器件寄存器;

TDO:测试数据输出,串行数据在TCK的下降沿从移位寄存器输出;

TRST:测试重置,为可选输入信号。

在时钟TCK的驱动下,测试模式TMS信号控制TAP状态机的状态,在不同的状态下,TDI提供串行数据输入,TDO为数据输出提供通道。如图1所示,JTAG所有的操作都同步于时钟信号TCK,在时钟上升沿,采样信号TMS和TDI,在时钟下降沿,输出测试信号TDO。

图1 JTAG接口时序图

1.2 TAP状态机

测试访问端口控制器(TAPC,TAP Controller)是JTAG工作的核心部分。如图2所示,TAPC控制整个TAP的运行状态,状态切换线路上的数据“0”和“1”表示的是TMS的信号电平。

图2 TAP状态机流程图

TAP状态机是一个有16个状态的有限状态机,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。TAP状态机主要可以分为三部分:复位操作、数据寄存器操作以及指令寄存器操作。其中,对指令寄存器的访问的一个周期中,从测试逻辑复位状态出发,历经测试/空闲、选择数据寄存器扫描、选择指令寄存器扫描、指令捕获、指令移位、第一次指令退出、指令更新各个状态,最后回到测试/空闲状态。在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的[3]。其中,在指令捕获(Capture-IR)状态下,指令寄存器中将加载一个固定逻辑矢量;在指令转移(Shift-IR)状态下,一条特定指令将移位进入指令寄存器;在指令更新(Update-IR)状态下,新的指令被锁存,即更新为当前指令。这样通过TAP状态间的转换就完成对指令寄存器的访问,指令执行,接下来将执行对数据寄存器的操作。对数据寄存器的访问操作和对指令寄存器的操作基本相同。

2 XSVF格式配置文件

可编程逻辑器件因其灵活性等优点在嵌入式系统中得到广泛的应用,在这些系统中利用串行矢量文件(SVF)可通过微控制器对可编程器件进行重新配置。SVF是一种描述IEEE 1149.1(JTAG)总线操作的标准文件格式[4]1。Xilinx公司提供用于可直接生成SVF格式配置文件的iMPACT工具,该工具附于标准Xilinx ISE软件内。SVF格式配置文件对于配置Xilinx系列可编程器件FPGA、CPLD以及PROM是非常方便的,因为在无需了解目标器件信息就可以生成包含复杂编程算法的SVF指令。SVF文件由ASCII语句构成,需要较大的存储空间,不便于嵌入式应用。为了提高嵌入式系统中存储空间的利用率,将SVF格式配置文件转换成一种紧凑的二进制XSVF文件。iMPACT工具能够直接将标准的BIT/MCS配置文件转化为XSVF格式文件。

在利用Xilinx ISE软件对目标器件进行相关设计之后,可以生成对应的器件配置文件(BIT/MCS文件)。利用iMPACT工具将BIT/MCS文件转换为XSVF格式配置文件,XSVF格式文件包含所有编程指令和设计信息数据。利用文本编辑软件UltraEdit打开一个XSVF文件,其部分数据如图3所示。

图3 XSVF格式文件数据

该文件中所有指令以十六进制数字代表,描述了所有JTAG总线操作信息,其中包含TAP状态机各个状态的状况指令和信息,以及目标器件的程序信息。如0X07代表定义重复测试TDO数据的次数,0X13代表设定指令移位状态(Shift-IR)的下一状态是空闲状态(Run-Test/Idle)还是指令暂停状态(Pause-IR),0X02表示进入指令移位状态[4]17-23。

3 硬件设计

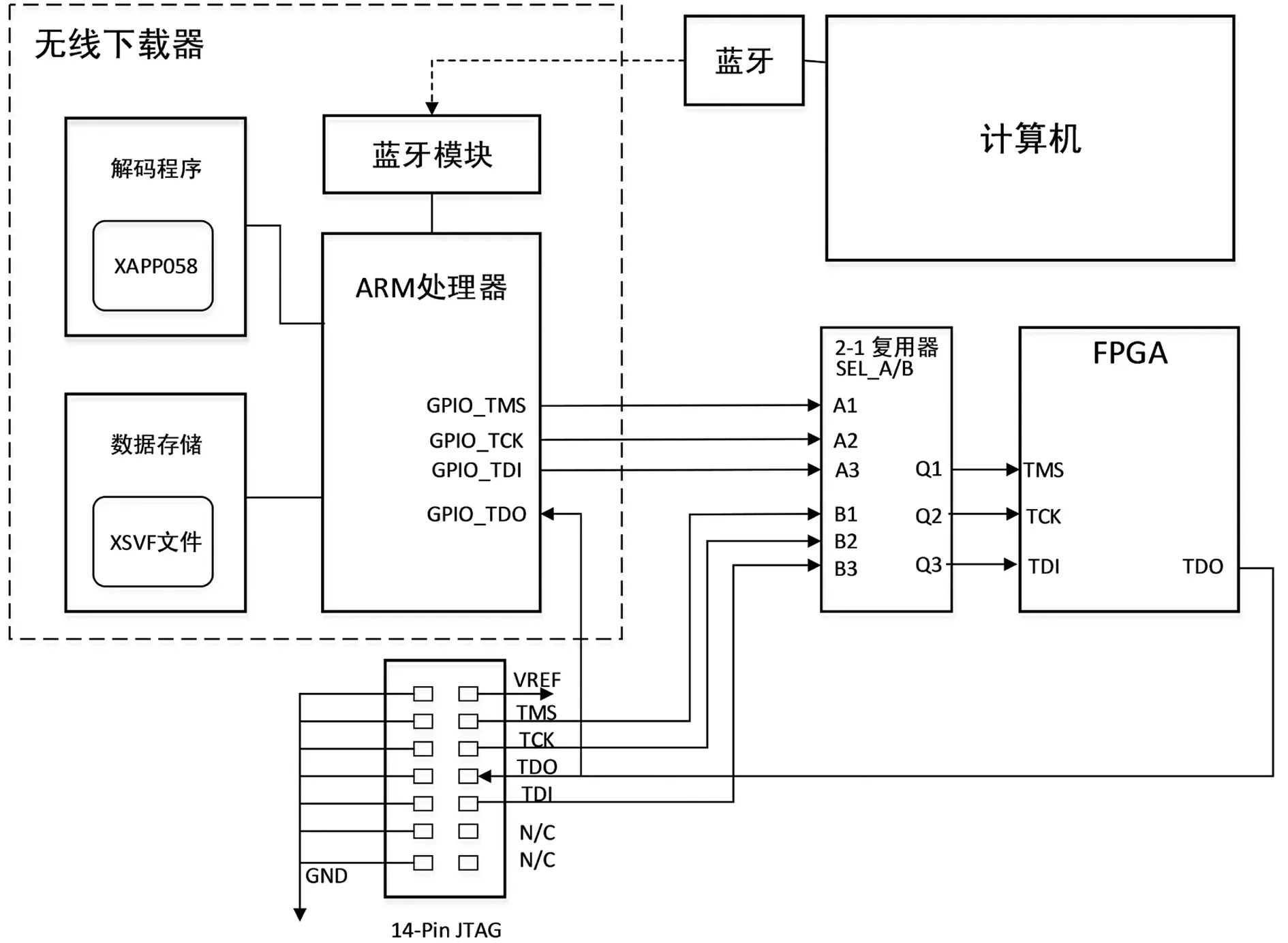

基于蓝牙通信的FPGA无线下载器的系统框图如图4所示。PC终端将可编程器件的配置文件(XSVF文件)通过蓝牙传输到无线下载器的蓝牙模块。蓝牙模块接收文件数据后通过串口方式输出到ARM处理器,处理器将接收到的数据信息以文件的形式存储至片外数据存储器。当数据文件接收完毕后,ARM处理器调用解码程序将XSVF文件解码为JTAG时序信息,通过GPIO口模拟JTAG接口配置相关器件。

图4 系统框图

所设计无线下载器主要功能是通过蓝牙接收上位机传输的配置文件,并将配置文件存储在片外存储器SD卡中,然后通过GPIO口模拟JTAG接口时序配置目标可编程器件。硬件部分主要包括ARM处理器、数据存储器、蓝牙模块HC-05,各功能部件主要功能如下:

(1)ARM处理器选用STM32F103系列芯片,主要功能是与蓝牙模块通信接收数据并将数据存储到数据存储器,调用相关程序实现对XSVF文件的解码,并通过GPIO口模拟JTAG接口时序实现对FPGA的在系统配置。

(2)数据存储器,用于存储FPGA芯片的XSVF格式配置文件。由于微处理器片内存储空间有限,故采用片外小容量的SD卡存储器。由于它具有体积小、数据传输速度快、可热插拔等优良特性,因此被广泛地应用于小型嵌入式系统装置中。在本设计中采用SD卡,既能满足存储容量要求,也能满足通信速度要求。

(3)蓝牙模块采用HC-05主从机一体蓝牙模块,它具有传统蓝牙技术的功能,模块的接口形式有串口、SPI接口、USB接口,在短距离通信中具有稳定的性能。此设计中选用了串口与ARM处理器进行通信,该通信方式操作简单且易实现。

4 软件设计

软件设计是实现所述下载器设计的重要部分,主要包含以下三个部分:参考C代码的移植、FATFS文件系统的嵌入以及XSVF文件数据接收与存储。

4.1 参考C代码的移植

Xilinx公司提供参考C代码文件XAPP058,用于读取XSVF文件并输出TAP控制字,可理解为对XSVF文件的解码过程,将XSVF文件中二进制指令转化为对JTAG总线操作。XAPP058源代码包含C代码文件lenval.c、micro.c、ports.c以及其对应的头文件lenval.h、micro.h、ports.h。lenval.c文件主要处理内部定义的数据结构变量,micro.c文件包含用来从存储器中读取XSVF文件、解码XSVF文件指令以及驱动JTAG信号的主要函数,port.c文件中程序的功能主要为在JTAG引脚(TCK、TMS和TDI)输出相应值、读取TDO端口的值以及以字节为单位读取XSVF文件数据。

在ARM处理器中需要移植上述代码,实现对可编程器件的配置。主要包含以下几个关键函数:

setPort:设定JTAG输出信号(TCK、TMS和TDI)为特定值。该函数的设置取决于微处理器中用于JTAG信号输出的I/O端口;

readTDOBit:读取JTAG输入信号(TDO)的值;

readByte:返回XSVF文件的下一字节。Micro.c文件调用readByte函数是为了连续读取XSVF文件。readByte函数在运行时必须记住上一次读取XSVF文件的位置才能完成本次读取,所以此函数通常用一个指针返回文件下一字节位置信息;

waitTime:等待时间。器件完成相关操作需要的最少等待时间,对此函数的校准是成功执行XSVF文件操作至关重要的一步[1]17。

4.2 FATFS文件系统的嵌入

为了方便处理器调用参考C代码对XSVF文件的读取操作,以及方便存储和管理不同的配置文件,在设计中嵌入FATFS文件系统。FATFS是专为小型嵌入式系统设计通用的文件系统模块,它完全由C语言编写,具有高可配置性以及良好的硬件平台独立性,可以将其嵌入到如8051、ARM、AVR、PIC等低成本的微控制器中[5]。

在设计中嵌入FATFS文件系统,主要需要调用以下几个关键函数来实现对文件的创建和读写操作:

f_mount函数,在FATFS模块中注册/注销一个工作区;

f_open函数,创建一个将要访问的文件对象;

f_close函数,关闭一个打开的文件,函数执行成功后,文件对象不再有效;

f_read函数,从文件中读取数据,其中文件对象的文件指针随着读取字节数的增加而增加;

f_write函数,写数据到文件。

4.3 XSVF文件数据接收与存储

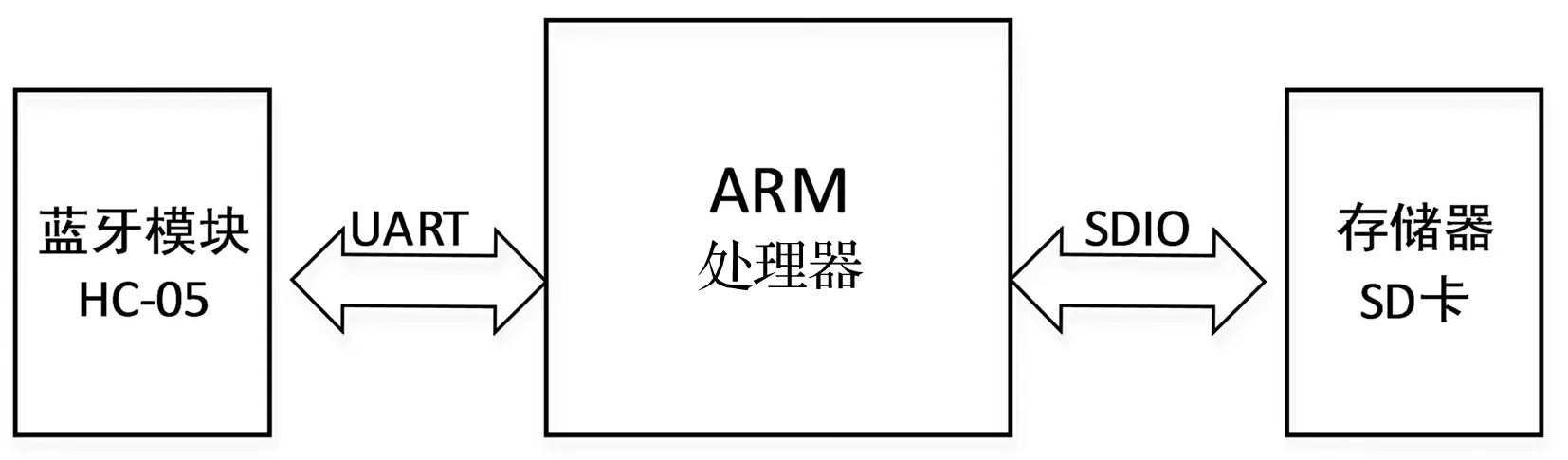

如图5所示,ARM处理器STM32F103和蓝牙模块HC-05与外置文件存储器SD卡之间的接口类型。处理器和蓝牙模块之间采用串口UART的方式传输数据,而和SD卡之间采用SDIO方式传输数据。蓝牙模块HC-05接收数据后通过串行方式传输到微处理器,UART串行通信方式简单易操作且成本低,适合通信速率不高的场合。处理器通过在存储器SD卡中嵌入FATFS文件系统实现对XSVF文件的相关存储和读写操作,SDIO接口方式能够满足数据传输速率要求。

图5 ARM处理器接口示意图

在对ARM处理器编程时,需要设定处理器与蓝牙模块的通信速率。该速率不能过高,其受限于处理器的运行速度以及和SD卡之间数据传输的速率。在往SD卡中存储数据时,调用了FATFS文件系统,这在一定程度上降低了存储速度,所以需要通过结合硬件调试协调各模块之间的传输速率,以达到更高的传输效率。

5 测试流程及结果

图6 测试流程图

根据上述方法完成硬件设计和软件程序编写,完成无线下载器的设计工作。对Xilinx公司SPARTAN-6系列FPGA芯片XC6SLX9进行测试工作,使用的是带有该芯片的一款开发板。

测试流程如图6所示。

图7所示为硬件测试平台,左边电路板为所设计的无线下载器,蓝牙模块垂直嵌入在其上方,右边为测试所用FPGA开发板。

(1)首先测试读取目标。FPGA芯片的器件ID,利用iMPACT工具生成读取器件ID的XSVF文件。此文件所含代码量比较少,但能够测试无线下载器模拟JTAG时序对目标器件的配置操作是否正常。该文件传输以及配置过程都非常短,利用串口软件在其界面打印出配置结果,如图8所示,可以看到“SUCCESS-Completed XSVF execution”信息,说明执行成功,下载器工作正常;此外,串口还输出了TAP状态转移等信息。

图8 串口输出结果

(2)接下来采用ISE软件编写程序操作开发板上4个LED灯,实现流水灯现象,完成仿真后生成BIN文件。同样利用iMPACT生成XSVF文件进行测试,此文件在10 s左右完成配置,如图8所示, 为测试流水灯试验的效果图,观察到流水灯现象,

说明配置成功。

(3)同样利用实现流水灯现象的程序,通过ISE软件生成MCS文件并将其存储至开发板外置SPI FLASH芯片M25P16中。由于直接对FPGA进行配置断电后程序丢失,而该FLASH芯片可以作为启动镜像[6]。将MCS格式配置文件转换为XSVF文件,然后进行测试。MCS文件相比于BIN文件较大,所以配置时间也比步骤(2)长。完成配置后同样观察到流水灯现象,接下来对FPGA开发板断电再重新上电,经过短暂的启动时间后,依然观察到流水灯现象,说明XSVF文件成功烧至开发板片外FLASH中。

6 结束语

本文提出了一种采用蓝牙通信方式无线配置Xilinx可编程器件FPGA的方法,完成了基于ARM处理器的无线下载器的设计。利用包含有复杂编程算法指令和所有设计信息数据的XSVF格式配置文件,通过嵌入式处理器能够方便地实现对兼容JTAG协议的器件进行在线配置。利用蓝牙传输方式实现了满足设计要求的低成本、短距离数据传输,并且实现了从有线配置到无线配置的跨越,这也为远程更新器件配置提供了可能。此外,处理器的外置存储器能够高效、灵活地存储以及管理配置文件。