基于FPGA认知无线网络中双优先级MAC协议的研究

2018-09-12徐智丁洪伟杨志军何敏保利勇柳虔林

徐智 丁洪伟 杨志军 何敏 保利勇 柳虔林

摘 要: 为了解决无线电应用需求与日益稀缺的频谱资源的矛盾,认知无线网络技术应运而生。根据无线网络节点工作特点,以现场可编程门阵列(FPGA)硬件电路为实验研究平台,首次对认知无线网络中双优先级MAC协议进行设计和实现。该设计充分运用FPGA的灵活性,采用硬件描述语言Verilog HDL和原理图相结合的方法,使用QuartusⅡ9.0 进行电路设计。通过对电路系统统计值与理论值比较,证实该设计具有实时性好、可靠性高、可移植性强等特点,能够有效减少系统节点能耗,提高系统吞吐率,可应用于无线网络。

关键词: 认知无线网络; 现场可编程门阵列; 双优先级MAC协议; 原理图; 节点能耗; 吞吐率

中图分类号: TN913?34 文献标识码: A 文章编号: 1004?373X(2018)17?0034?06

Abstract: The cognitive wireless network technology came into being to solve the contradiction between radio application demand and increasingly?scarce spectrum resources. According to the operating characteristics of the wireless network node, the field programmable gate array (FPGA) hardware circuit is used as the experimental platform to design and implement the dual?priority MAC protocol in the cognitive wireless network. The method combining hardware description language Verilog HDL and schematic diagram, and Quartus Ⅱ 9.0 are used to design the circuit by making the full use of FPGA flexibility. By comparing the theoretical value and statistic value of the circuit system, it is proved that the design has the characteristics of perfect real?time performance, high reliability and strong portability, can effectively reduce the energy consumption of the system nodes and improve the throughput of the system, and can be applied to the wireless network.

Keywords: cognitive wireless network; field programmable gate array; dual?priority MAC protocol; schematic diagram; node energy consumption; throughput

0 引 言

认知无线网络[1]的核心是分配、管理和利用割裂的频谱资源,从而进行动态调配,而这些割裂的频谱资源就形成了多个信道,因此认知无线网络中的MAC协议主要是基于多信道的MAC协议。这些协议完成的主要工作是获取网络信息,为不同的通信节点分配相应的信道,消除数据分组之间的冲突,使尽量多的节点可以共用网络资源同时进行通信。

而在认知无线网络环境下的MAC协议中,CSMA方案能够在较大程度上避免发送节点之间的冲突,提高信道传输效率,减少节点能耗。文献[2?3]中以Matlab为实验平台,针对CSMA协议的相关理论进行分析,这样的研究方式仅能对理论结果进行验证,并没有在仿真实验过程中体现协议的控制原理与数据实时传输的过程。FPGA技术在许多领域均有广泛的应用,特别是在无线通信领域,由于具有极强的实时性,使其对信号进行实时处理成为可能;由于它是通过面向芯片结构指令的软件编程来实现其功能的,因此仅修改软件代码而不需改硬件平台就可以改进系统原有设计方案或原有功能,因而具有极大的灵活性;又由于FPGA并非专门为某种功能进行设计,因而使用范围广、产量大、价格低,所以FPGA在无线通信系统研究中大量应用,促进了无线通信的发展。文献[4?5]中以FPGA为实验平台,为单通道CSMA协议提供一种电路实现方案,但该方案仅通过伪随机码生成近似泊松分布的信源信号,且整个设计都依靠电路完成,实验参数不宜更改,重塑性难度很大,实现精准性较差,因此该硬件设计方案并不理想。

综合上述应用与研究现状,本文结合Matlab与Quartus Ⅱ两种工具搭建实验平台,不仅设计出满足协议要求的信源模块,并且结合Quartus Ⅱ电路模块化设计的特点,在电路系统模块中充分体现双优先级概率检测CSMA协议算法的控制原理与传输过程,设计出双优先级数据传输系统。最终系统测试的统计值结果与理论值一致,且该系统在吞吐量与节点能耗两方面均优于其他多项MAC协议,证实了其优秀的通信性能。

1 协议性能分析

吞吐量是系统单位时间内成功传送数据的数量,而节点平均功率是系统能量消耗的一个标志。本文基于FPGA对双优先级概率检测CSMA协议接入的系统进行研究,首先从吞吐量和节点能耗两个方面进行理论分析。

1.1 吞吐量分析

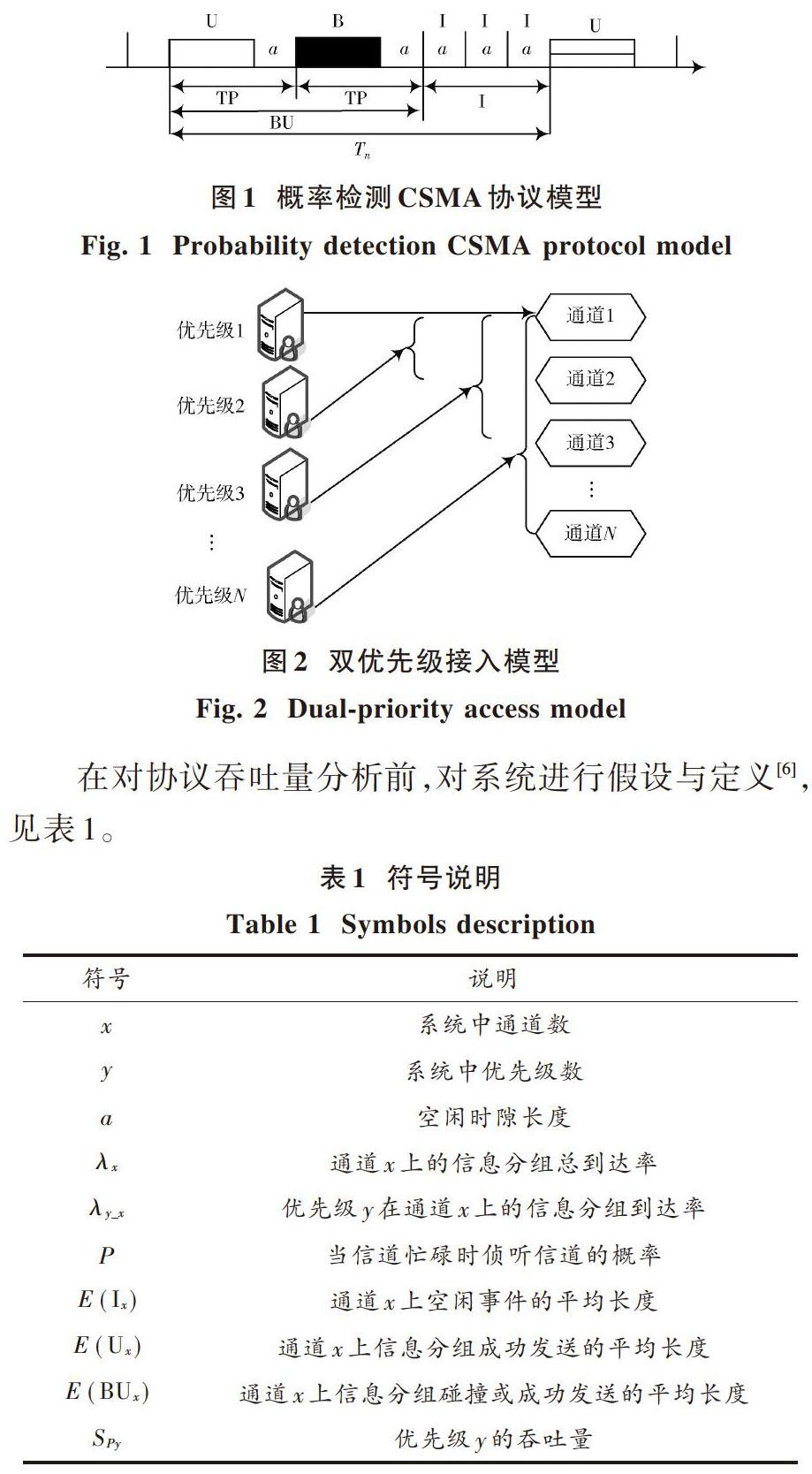

概率检测CSMA协议原理为:当节点准备发送数据时,会先对信道进行监听,当信道处于空闲时,则节点将在下一个时隙的起始时刻立即发送数据,当信道忙碌时则以概率[P]侦听信道状态,等到信道空闲再进行发送。

图1是概率检测CSMA协议模型。其中U,B,I分别代表信道的三种状态:信息发送成功、信息碰撞、信道空闲。TP表示一个信息分组的发送时间,BU表示信息分组发送成功和产生碰撞的联合事件;[Tn]表示出现忙时间周期和空闲时间周期的一个循环周期。在实际的通信系统中,存在着多种业务类型,根据这些业务的不同特点设置两种优先级,同时在通信系统中提供两个信道给终端节点随机占用,且规定终端采用概率检测CSMA随机多址接入技术。

图2为双优先级系统接入模型,系统中有两个优先级,并且提供两个通道进行数据传输。优先级的顺序从低到高依次为优先级1、优先级2,其中每个优先级的用户个数不限。若某用户处于优先级2,那么其业务固定占用信道1与信道2。而优先级[y]在通道[x]上的到达率则为[λxN-x+1]。

1) 每条信道接入的方式为概率检测CSMA协议,并且在信道[x]上的信息分组到达过程都满足独立参数为[λx]的泊松分布[(x≤]2);

2) 信道空闲的时隙长度为[a],有分组发送时的时隙长度为单位长度1,为[a]的整数倍;

3) 碰撞或放弃发送的信息分组将在后面某时刻进行重传,重传的分组对信道的到达过程没有影响。

4) 若此时系统负载均衡,每条信道上信息总到达率均为[λ=λ1=λ2]。

根据泊松分布的规律,首先求解信道2中分组成功发送事件[U2]的平均长度[E(U2)]:

对于双优先级概率检测CSMA控制协议下的通道2而言,仅有优先级2的信息分组在发送,而分组成功发送分为以下两种情况:

1) 空闲期的最后一个时隙一个信息分组到达,并且在下个时隙立即发送,该事件平均时隙数为:

综上所述,双优先级概率检测CSMA系统的总吞吐量表达式为:[S=S1+S2]。

1.2 节点能耗分析

为了求得系统功耗的数学表达式,对发送终端节点的三种不同状态下所需功率进行设定:

1) 处于发送状态时功率为[Ps];

2) 处于侦听状态时功率为[Pl];

3) 处于接收状态时功率为[Pr]。

2 系统模块化设计

系统设计充分运用Quartus Ⅱ的模块化设计特点,整个电路系统分为:泊松信源模块、状态分类模块、跳读模块、优先级争用模块、吞吐量检测模块。

2.1 泊松信源模块

众所周知,在硬件电路中生成满足泊松分布的信源信号是非常难的。现有的基于FPGA设计的MAC协议中基本是由伪随机序列生成近似泊松分布的数据信号,这就势必会造成协议实现的不准确性。

图3是泊松信源模块,该模块首先由Matlab中的Poissrnd函數产生泊松序列,然后将该泊松序列保存为Quartus Ⅱ中IP内核ROM可读取的文件格式,最后将ROM存储的泊松数据流经过八分频时钟转换生成拟定的信息状态数据(例:0000_0001代表信道空闲,0000_0110代表数据发送成功,0000_0111代表信息冲突),满足协议要求的泊松信源数据就成功引入到电路中。采用这种数据产生方式可在Matlab程序中调整泊松函数的到达率[λ]的值,便于电路系统的仿真测试。

2.2 状态分类模块

经过ROM存储和八位映射关系转换后,Matlab中的泊松数据流成功引入到电路中,但是此处的信息数据时隙长度相等,都是八位位宽,这并不满足1.1节吞吐量分析中不同状态时隙长度的倍数关系。

图4是状态分类模块,该模块由异步FIFO和反馈计数器组成。异步FIFO具有一定的存储功能,在保持写使能处于高电平,而读使能从高电平变为低电平时,输出的信息会保持最后时刻读到的数值。根据异步FIFO这一工作特性,当反馈计数器检测到异步FIFO信息流数据为非空闲数据时,立即将低电平信号给予读使能,这样异步FIFO读出的数据就会暂停为当前非空闲数据。与此同时,通过设置计数器数值来控制恢复读使能的时间,这个时间就是忙碌事件的时隙长度,从而实现不同状态时隙长度可控的功能,产生满足协议要求的数据流。

2.3 优先级争用模块

在双优先级接入模型中已知优先级1与优先级2均在信道1上进行数据传输,因此信道1上存在着信道争用的问题。

如表2所示,将(1,6,7)和(2,8,9)分别表示优先级1与优先级2的三种数据状态。当两个优先级都无数据时,则信道1为空闲状态;当两优先级中有一个为单一数据到达另一个为无数据时,则信道1为成功发送状态;其余实时情况均为信道1信息冲突,这样便体现信道争用的状况。

2.4 跳读模块

依据双优先级概率检测协议传输原理可知在信道2上仅有优先级2传输数据。因此为了在电路设计中实现单通道上的信息分组竞争,体现这两种事件,将一个信息站点分为空闲站点和忙碌站点。这两个站点数据分别来自Matlab中的两个泊松数据流,到达率分别为[λ1,λ2],且[λ1+λ2=λo],这样一个到达率为[λo]的泊松数据站点便生成了。而选择读取模块根据侦听到信道总线上实时数据[(I,U,B)]来跳读空闲或忙碌站点的信息数据,这样系统既完成了监听信道的功能又实现了单通道上信息分组竞争状态。

2.5 吞吐量检测模块

在该FPGA电路系统中,可通过统计系统中两个信道上吞吐量的方法统计协议实际工作的吞吐量,即统计系统各个信道上在仿真时间内成功发送的数据时隙与系统总仿真时隙的比值。这一模块由检测计数器组成,该计数器滤过空闲数据与碰撞数据,直接统计两个信道上数据成功发送时隙的个数。吞吐率计算方式如下:

2.6 系统顶层设计

依据FPGA自顶向下的设计特点,将泊松信源模块、状态分类模块、优先级争用模块、跳读模块、吞吐量检测模块连接构成系统。

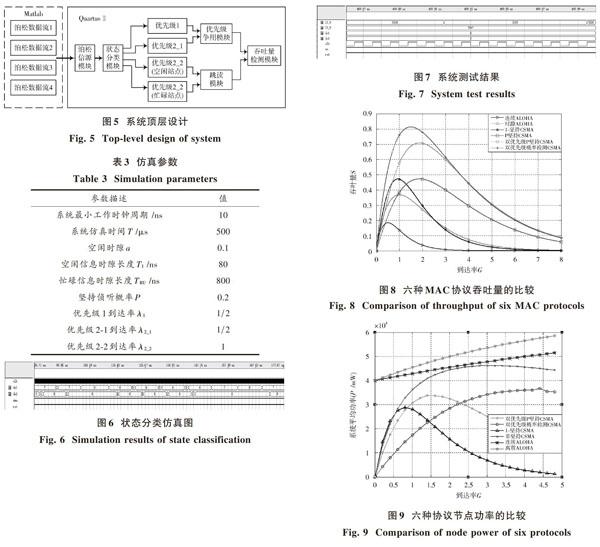

图5为系统顶层设计图,Matlab中Poissrnd函数产生4个不同的泊松数据源,经过泊松信源模块后成功将泊松数据引入到Quartus Ⅱ设计的电路中,再经过状态分类模块对不同状态的数据时隙长度进行控制,从而生成各优先级数据。其中,优先级1与优先级2_1在信道1上经过优先级争用模块控制后进行数据传输,优先级2_2(空闲)与优先级2_2(忙碌)在信道2上经过跳读模块后进行传输。最终信道1与信道2的成功发送数据都被吞吐量检测模块进行计数统计。

3 系统测试与分析

系统测试主要针对双优先级概率检测CSMA中吞吐量与节点能耗两方面进行。其中以第二节中推导的协议理论表达式算出的值为检验标准。实验过程中信息分组到达率[λ]值在Matlab的泊松函数中进行设定;信道状态不同时隙长度的数值关系可以在状态分类模块中的计数器程序中调整。实验仿真参数设置如表3所示。

表2已设定(0,6,7)和(1,8,9)分别代表优先级1与优先级2_1的3种数据到达状态,图6为经过状态分类模块处理后的数据,do1与do2分别代表优先级1与优先级2_1的实时数据,其中空闲数据0与1的时隙长度明显与非空闲数据6,7,8,9有着整数倍数关系,这与设计的初衷是相符的。系统测试结果如图7所示,该系统测试在表3仿真参数条件下进行,do1与do2为信道1与信道2上的实时传输数据,C1_U与C2_U分别为信道1与信道2上数据传输成功状态的时隙个数,分别为3 326,3 347。经计算,系统信道1与信道2吞吐量的仿真值分别为0.483 7和0.486 8,与理论值0.483 5一致;优先级2的测试值为0.728 6,与理论值0.725 3一致。根据系统吞吐量仿真值可计算系统仿真过程中节点平均功率值为17.36 mW,与理论值17.34 mW一致,证明了该协议设计正确。

双优先级概率检测CSMA与其他协议系統的吞吐量理论值与统计值的对比如图8所示,各MAC层协议硬件测试的吞吐量统计值点均在理论值曲线上。从图8中可清晰看到,双优先级概率检测CSMA协议不仅有着较高的吞吐量,并且在系统到达率增大的情况下能保持较高的吞吐量,展现了其较强的稳定性与实用性。在系统平均功率的测试中,根据已设定的条件经仿真得到双优先级概率检测CSMA与其他协议系统节点平均功率的对比如图9所示。从图9中可观察到,在系统到达率变化范围内,系统平均功率统计值均在理论值曲线上,双优先级概率检测CSMA协议系统整体节点平均功率较低,证实了该协议能够有效降低通信系统的能耗。

4 结 语

本文在认知无线网络背景下,根据无线传感器网络节点的工作特点和实际需求,运用FPGA对多通道MAC协议中的双优先级概率检测CSMA控制策略接入的系统进行电路设计。该电路不仅结合Matlab与Quartus Ⅱ两种软件,将泊松数据流引入到电路中,同时根据通信协议算法特点,将其工作原理映射到电路系统中,展现双优先级数据传输过程。经过实验仿真测试,在所设定的仿真条件下,系统吞吐量与节点平均功率仿真值与理论值一致,性能优于其他多种MAC协议,证实了该设计的准确性、稳定性与有效性。FPGA作为硬件化的一种表现,通过其实现通信协议算法,能够将现实中的节点传输过程在硬件的并行电路上实现,是一个从理论联系到实践的过程,对提高通信协议算法理论认识有较大的帮助,为通信协议研究与实现提供了参考。

注:本文通讯作者为丁洪伟。

参考文献

[1] 魏急波,王杉,赵海涛.认知无线网络:关键技术与研究现状[J].通信学报,2011,32(11):147?158.

WEI Jibo, WANG Shan, ZHAO Haitao. Cognitive wireless networks: key technologies and research status [J]. Journal of communications, 2011, 32(11): 147?158.

[2] 谭明川.基于概率检测的CSMA/CA无线传感器网络协议及控制电路分析[D].昆明:云南大学,2011.

TAN Mingchuan. Analysis of protocol and control circuit of CSMA/CA wireless sensor network based on probability detection [D]. Kunming: Yunnan University, 2011.

[3] DING H, GUO Y, ZHAO Y, et al. Research on the multi?channel probability detection CSMA protocol with sensor monitoring function [J]. Sensor letters, 2015, 13(2): 143?146.

[4] LIU Z G, DING H W, XIONG J L, et al. FPGA?based design of P?detection 1?persistent CSMA control system [J]. Applied mechanics & materials, 2014, 602: 933?936.

[5] 刘正纲.WSN中二叉树冲突分解DP?CSMA/CA协议的FPGA控制系统设计与实现[D].昆明:云南大学,2015.

LIU Zhenggang. Design and implementation of FPGA control system based on binary tree collision resolution DP?CSMA/CA protocol in WSN [D]. Kunming: Yunnan University, 2015.

[6] 周圣杰,丁洪伟,杨志军,等.自适应三维概率CSMA控制策略研究[J].电子学报,2017,45(2):440?445.

ZHOU Shengjie, DING Hongwei, YANG Zhijun, et al. Adaptive three?dimensional probabilistic CSMA control strategy [J]. Acta electronica Sinica, 2017, 45(2): 440?445.

[7] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

XIA Yuwen. Verilog digital system design tutorial [M]. Beijing: Beijing University of Aeronautics and Astronautics Press, 2008.

[8] 田耘.无线通信FPGA设计[M].北京:電子工业出版社,2008.

TIAN Yun. Wireless communication FPGA design [M]. Beijing: Electronics Industry Press, 2008.

[9] 丁洪伟,赵东风,黄毛毛.新型随机多址接入无线传感器网络MAC控制协议与能量有效性分析[J].通信学报,2010,31(2):51?57.

DING Hongwei, ZHAO Dongfeng, HUANG Maomao. MAC control protocol and energy efficiency analysis for a novel random multiple access wireless sensor network [J]. Journal of communications, 2010, 31(2): 51?57.

[10] 李朋举.OCR?MAC:一种新的基于CSMA的无线传感器网络MAC协议[J].电子设计工程,2014,22(23):154?157.

LI Pengju. OCR?MAC: a new MAC protocol based on CSMA for wireless sensor networks [J]. Electronic design enginee?ring, 2014, 22(23): 154?157.

[11] 陈洲廷,赵东风,蒋慕蓉.连续与离散时间混合控制的多通道随机多址接入Ad Hoc网络协议分析[J].云南大学学报(自然科学版),2009,31(5):463?469.

CHEN Zhouting, ZHAO Dongfeng, JIANG Murong. Multi?channel random multiple access Ad Hoc network protocol analysis with continuous and discrete time hybrid control [J]. Journal of Yunnan University (natural science), 2009, 31(5): 463?469.