应用于汽车雷达的X波段二倍频器

2018-08-24

(重庆邮电大学 光电工程学院,重庆 400065)

近年来,随着生活水平的提高,道路上的汽车越来越多,由此带来的交通安全问题逐渐成为社会关注的焦点。作为一种交通预警装置,汽车雷达是降低交通事故的首选设备。目前市场上对高性能、低成本的汽车雷达的需求越来越迫切[1]。

相对应地,汽车雷达用毫米波频率源成为了研究热点[2]。目前,24 GHz与77 GHz为常见的汽车雷达频段,此频段毫米波信号源主要通过对稳定的微波信号进行多次倍频来获取[3]。然而直接对微波信号进行多倍频会导致倍频效率和输出功率均较低的问题。相比之下,选择先将微波信号进行二倍频,再以此信号驱动下级倍频器实现四倍频成为了比较主流的毫米波信号源获取方式。文献[4]介绍了一种在12 GHz频率源后串接K波段二倍频器来获取24 GHz频率源的方法,但12 GHz频率源相对于6 GHz频率源来说成本偏高。本文基于6 GHz频率源设计X波段倍频器,以降低获取12 GHz频率源的成本。

目前,毫米波倍频器主要以二极管倍频器为主,文献[5]介绍了一种180~190 GHz固态平衡式无源二倍频器,倍频损耗最小为16.8 dB,最大为22 dB。文献[6]则介绍了一种140~152 GHz二倍频器,在20 dBm的输入功率下输出6 dBm。这两个二倍频器均是基于二极管进行设计的,具有宽带应用的特性,但本次设计的X波段倍频器为24 GHz倍频器的前驱倍频器,要求X波段倍频器为窄带倍频器,同时对谐波抑制良好,因此选择FET倍频器作为设计主体。文章通过对FET倍频器的设计原理进行分析,使用仿真软件基于NEC公司的MESFET,通过软件设计与硬件调试相结合的方式设计出应用于24 GHz汽车防撞雷达的前驱二倍频器。

1 倍频原理

理论上,各种半导体元件只要具有非线性,都可以用来构成倍频器。在固态电路中,采用的非线性元件一般是半导体二极管。某些情况下,还可以采用微波场效应管,如MESFET等实现频率变换。

本文设计的倍频器为FET倍频器,图1示出了FET倍频器的结构图,此电路的输入回路需调谐于基波且对高频谐波有抑制,以此来保证此电路输入通路只有基波信号通过而无高次谐波泄露。此电路输出回路调谐于输入信号频率的第n次谐波,对其他谐波与基波都是短路的,以此来保证此电路输出回路只有第n次谐波输出而无基波以及其他谐波输出。通过改变栅压此电路可制成三种类型的倍频器,分别为A类、B类和AB类。

图1 FET倍频器结构图Fig.1 Structure diagram of FET frequency doubler

其中,A类倍频器栅极偏置电压在φ附近 (φ为栅极肖特基势垒电压),利用ID的限幅效应得到半波,导通角θ=2π,直流分量较大,但倍频效率很低。

B类、AB类漏极输出波形与A类相比有更多的谐波分量,因而常被用于高效率倍频器的设计。

其中以AB类效率最高,此类倍频器栅极偏压处于φ与夹断电压VP之间,大信号输入时限幅与夹断效应同时出现,引起漏极电流的上下截顶。此类倍频器不能用于偶次倍频器的研制,且工作电流大,容易自激。

B类倍频器栅极偏压在VP附近,利用管子的夹断效应得到尖峰脉冲电流,相对而言管耗比较低且倍频效率比较高,在防自激方面也有着一定的优势。综合考虑三种类型的FET倍频器的优缺点,本次设计采用B类倍频器[7]。

FET管倍频器在实际应用中大多数工作在截止模式,漏极电流可用如下傅里叶级数展开:

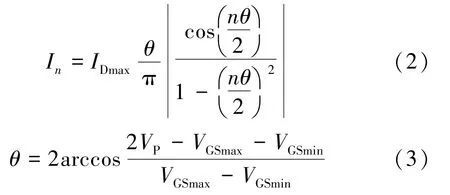

对B类倍频器,有各次谐波幅值:

式中:IDmax为漏极电流峰值;VGSmax为栅极饱和电压;VGSmin为栅极反向电压峰值。

2 二倍频器的设计

本次设计的X波段二倍频器为24 GHz倍频器的前驱倍频器,为下一级K波段倍频器提供X波段输入信号。二级倍频器选择 ADI公司型号为HMC448LC3B的倍频器芯片,该芯片输入频段为10~12.5 GHz,在-4~6 dBm的输入功率下二倍频输出11 dBm的信号,满足24 GHz汽车雷达频率源的输出要求。基于此,本文所设计的前级二倍频器工作频段为5.9~6.1 GHz,中心频率为6 GHz,要求在10 dBm的驱动功率下输出功率达到 -4 dBm以上,谐波抑制大于15 dB。基于以上指标,本设计采用NEC公司型号为NE900100的MESFET作为FET倍频器的核心倍频部件。根据datasheet,该晶体管典型夹断电压VP为 -3.5 V,截止频率高达20 GHz。

2.1 夹断电压选取

夹断电压的选取决定了晶体管是否能够正常稳定工作,在ADS软件中利用NEC公司官网提供的NE900100 ADS仿真模型得出该晶体管的I-V特性曲线,仿真结果如图2所示。仿真结果显示当VGS<-3.5 V时,ID=0 mA,此时MESFET工作在截止区。当VGS=0 V时,漏极电流峰值IDmax=243 mA。综合考虑,选取夹断电压VP=-4 V。

图2 NE900100 MESFET的I-V仿真特性曲线Fig.2 I-Vcharacteristic curves of simulation of NE900100

2.2 偏置电路设计

由于本设计采用MESFET来制作倍频器,因此,输入输出匹配电路中会有直流偏置电路的存在。直流偏置电路主要起到带阻滤波器的作用,在通过直流馈电的同时抑制射频信号的泄露。

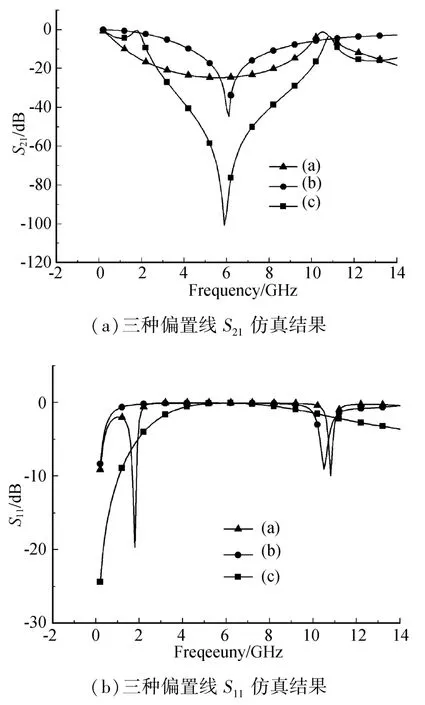

图3中的三种偏置线是三种较为典型的偏置结构,使用仿真软件分析了这三种偏置结构在6 GHz为中心频点的宽带范围内的S参数特性,仿真结果如图4所示。

图3 三种典型偏置线结构图Fig.3 Three structures of typical offset line

图4的仿真结果表明这三种偏置结构在4~8 GHz内S11均大于-2 dB。对比仿真结果,图3(a)这种传统的偏置电路具有宽频带的特点,在2~9 GHz的范围内S11均大于-2 dB的同时S21小于-10 dB,缺点是曲线比较平滑,在可用频段内没有比较明显的变化,对5.5~6.5 GHz的射频信号衰减只有23~25 dB,中心频点处衰减为25 dB;图3(b)这种新型的单扇形偏置电路在中心频点处S21达到-45 dB,在5.5~6.5 GHz的频段内S21也能达到-30 dB,对于本次设计所涉及到的频段衰减较为明显,缺点是带宽比较窄;图3(c)[6]这种四扇形偏置电路在2.3~10.6 GHz的宽带范围内S21小于-20 dB,且S11在此频段内均大于-2 dB,是图3这三种偏置结构中防止射频信号泄漏效果最好的,但是缺点是结构过于复杂,占板空间大,在进行版图设计时排版困难。综合考虑上述三种结构的优劣,本设计采用图3(b)这种单扇形结构。

图4 三种典型偏置线S参数仿真结果图Fig.4 Simulation results of S parameter of three structures of offset line

2.3 X波段二倍频器设计

FET倍频器的设计关键在于输入端与输出端要根据不同的频段分别进行匹配。本次设计的二倍频器输入端匹配电路的设计应考虑对基波匹配的情况下对二次谐波要有反射。输出端电路的设计应考虑对二次谐波匹配的情况下对基波要有抑制。

此外,还需要在输入匹配电路的前端添加隔直电路,并在输出匹配电路的后端添加有隔直作用的滤波器,在滤除杂波的同时防止直流泄露。由于本次设计的倍频器为X波段,表贴电容或者梁式引线电容虽然也适用,却有着价格昂贵、焊接困难以及对信号影响较大的缺点。因此采用文献[9]中提出的一种四分之一波长交趾耦合滤波器来实现输入输出端的隔直以及滤波功能。此滤波器结构如图5所示,这种结构具有极低的插入损耗以及适中的频带宽度,适用于对滤波性能要求不高的电路中。

本次FET倍频器的输入以及输出匹配均采用较为经典的 “π”型匹配,如图6所示。图6中,W与L分别为微带线的宽度和长度,BPF为图5中给出的四分之一波长交趾耦合滤波器。

图5 四分之一波长交趾耦合滤波器结构图Fig.5 Quarter wavelength two-finger DC-block with matching structure

图6 X波段FET倍频器仿真原理图Fig.6 Simulation schematic of X-band FET doubler

3 实物测试分析

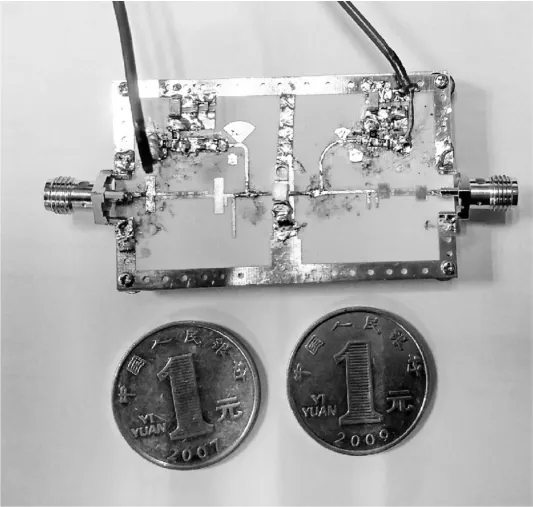

考虑印刷电路板 (Printed Circuit Board,PCB)板材介电常数及损耗对于高频电路的影响,本设计采用0.254 mm厚的罗杰斯4350 B作为基板。该类型的基板被广泛应用于高频电路板的设计与制作。实际制作的X波段二倍频器如图7所示,NE900100焊接在罗杰斯4350 B上。

图7 X波段二倍频器实物图Fig.7 Real photograph of X-band FET doubler

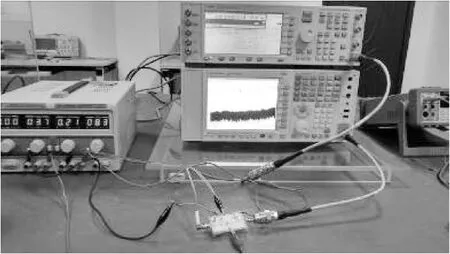

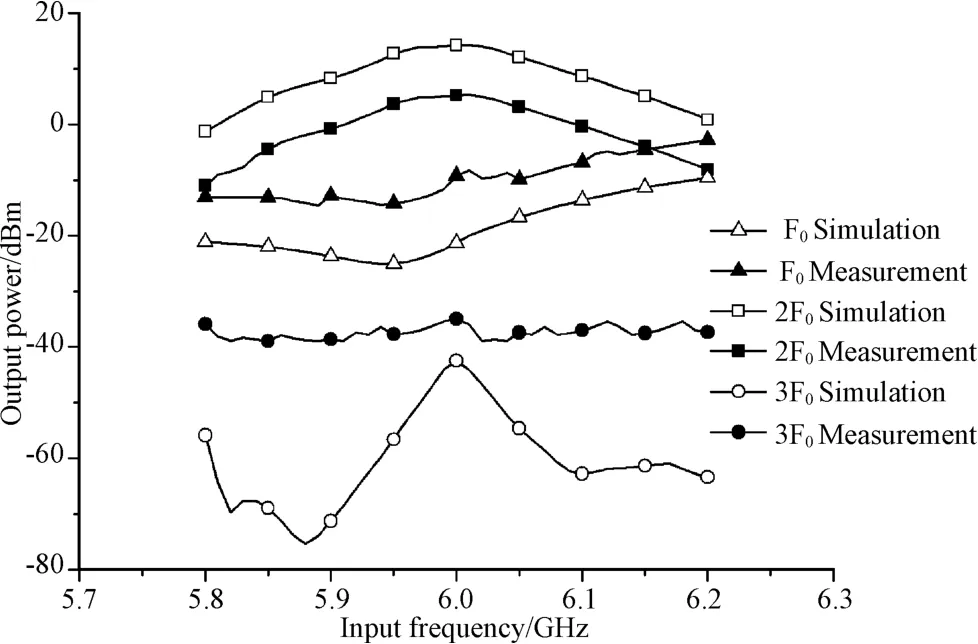

图8为二倍频器现场测试图,信号源通过同轴线与SMA接头相连,可以提供10 dBm的输入功率。图9为二倍频器仿真与实物测试功率曲线,F0为倍频器输出的基波功率,2F0为倍频器输出的二次谐波功率,3F0为倍频器输出的三次谐波功率。

由图9可见,在5.9~6.1 GHz的频带范围内倍频器2F0输出功率大于10 dBm,此时F0与3F0输出功率小于-10 dBm,谐波抑制良好。在中心频率6 GHz处,输出基波抑制达到30 dB以上,各次谐波得到抑制,谐波抑制特性良好。仿真时最高输出功率14 dBm比设计指标的-4~6 dBm要高8 dB。考虑到后续加工过程中微带线加工误差、焊接元器件以及SMA接头等带来的影响,仿真结果达到设计要求。由测试结果可知,在5.9~6.1 GHz的输入频段内,实际测试得到的二次谐波输出功率为-4~5 dBm,在6 GHz处输出功率达到峰值,输出基波抑制大于15 dB。基波与三次谐波的测试结果与仿真结果相差不大,二次谐波的测试与仿真结果趋势一致,但仍存在一定差距。这是加工误差、测试过程中MESFET热效应以及倍频电路自激导致的。

图8 X波段二倍频器现场测试图Fig.8 Field test photograph of X-band FET doubler

图9 X波段二倍频器仿真与实物测试功率曲线Fig.9 Simulation and test results of X-band FET doubler

对于FET倍频器而言,倍频电路稳定性控制不佳会导致电路自激。本次设计的倍频器在实物测试时便出现了自激问题。调试过程中,在MESFET的栅极以及漏极均增加了RC稳定电路,在抑制自激问题的同时导致了二次谐波的输出功率的下降。通过一系列的调试,最终二倍频器的最佳输出功率稳定在5 dBm,此时的漏极电压为8 V,ID峰值为220 mA,低于VDS=8 V,IDmax=243 mA的仿真结果。在仿真过程中已经添加稳定措施的情况下实物测试中仍然出现了自激问题。由此可以看出如何同时兼顾好FET倍频器的输出功率与稳定性仍是FET倍频器设计中的一个重要挑战。

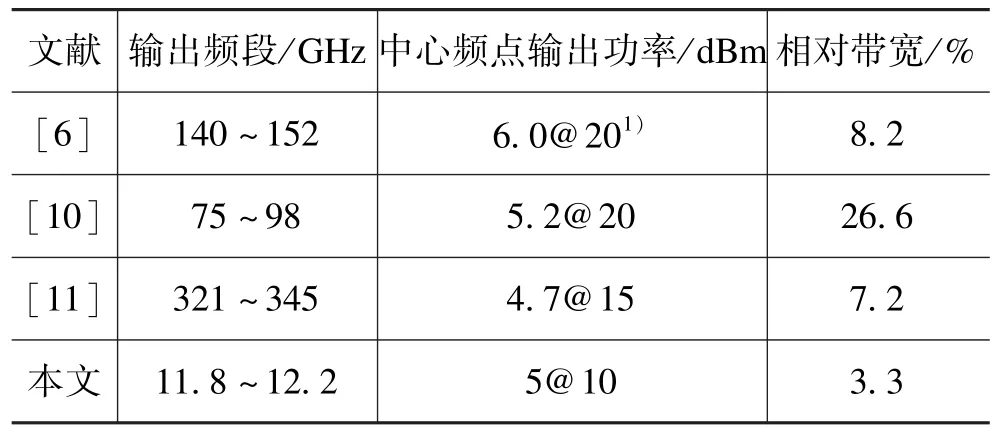

表1为本文所设计的二倍频器与文献[6]、[10]、[11]二倍频器的数据对比,可以发现目前国内外的倍频器设计主要以宽带二极管倍频器为主且所需驱动功率较大,对于应用于窄带的倍频器研究较少。本次设计的X波段倍频器在窄带应用方面有着一定的优势。考虑到SMA接头与射频同轴线存在大于4 dB的插入损耗,若将此倍频器与ADI公司的HMC448LC3B倍频器芯片集成在一块PCB板上,在输入端提供输出功率10 dBm的稳定频率源,恰好能够驱动HMC448LC3B倍频器芯片工作。

表1 二倍频器输出功率对比情况Tab.1 Comparison of the output power of the doubler

4 结论

本文分析了FET倍频器的工作原理,比较了几种常见的偏置电路优缺点,综合软件仿真与实物调试,设计了一款应用于24 GHz频率源获取的前驱二倍频器。经测试,所设计二倍频器最高倍频输出功率为5 dBm。在设计过程中,软件仿真与实物调试相结合的设计方法有效降低了倍频器的设计难度。但由于FET倍频器的自激问题,导致了二次谐波的输出功率与仿真存在较大误差。可以看出,在提高FET倍频器稳定性的同时提高倍频输出功率依然是目前FET倍频器实物制作的设计难点。随着毫米波电路的发展,窄带应用型倍频器由高附加噪声到低附加噪声,由低谐波抑制到高谐波抑制演变,这也是未来工作的主要研究方向之一。