射频组件中电源滤波电路的频率与瞬态响应

2018-08-23张大鹤

张大鹤

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

0 引言

射频通信系统中,抑制噪声和干扰极为重要。电源干扰是电子系统中干扰的重要来源[1]。为了抑制由电源带来的干扰,射频系统中一般都采用大量的滤波措施。

目前很多射频组件设计中,对电源滤波电路原理缺乏分析,元器件的选值缺乏定量计算。滤波电路中常见问题的有:滤波不足、滤波过重、不计算滤波电路的截止频率、照搬元器件选值、降额不足、元器件被不恰当地理想化、瞬态响应缺乏考虑等,这些问题已经无数次影响了产品的技术指标、可靠性、通用性、体积和成本。事实上,很多滤波电路几乎没有发挥任何有益的作用。

可见,对电源滤波电路原理进行理论分析和仿真很有必要。

1 电源噪声干扰对技术指标的影响

射频电路中,电源噪声和干扰在频域中的影响主要是产生相位噪声和杂散信号。在时域中则表现为时钟的抖动。

由于射频系统中VCO对电源干扰较为敏感,而且具有较为清晰的数学模型,便于分析,下面以VCO为例进行推导。

1.1 相位噪声

理想VCO的数学模型为[2]:

ω=ω0+Kvu(t),

(1)

式中,Kv为电调灵敏度。实际VCO的输出频率也受电源电压影响,当调谐电压固定时,VCO的输出相位与电源电压也有类似的关系,其数学模型为:

ω=ω0+Kpu(t),

(2)

式中,Kp为推频系数。

(3)

由上式可知,电源噪声电压造成相位噪声与VCO的推频系数和噪声的偏移频率相关。

1.2 杂散

纹波电压指电源输出的直流电压上叠加的交流成分。一般来说,线性电源输出纹波电压较小,开关电源输出纹波电压较大。

电源的纹波电压直接调制到VCO的输出,产生杂散。纹波电压不是很大时,调制指数≪1,在频偏f处,理论上输出噪声电压在VCO上产生的杂散近似为:

(4)

式中,vn为频率f的纹波电压的有效值。由上式可知,电源噪声电压造成的相位噪声与VCO的推频系数和纹波电压的频率相关。

1.3 相位抖动

相位噪声和杂散在时域中都表现为相位抖动。采样时钟相位抖动对ADC的性能有很大影响,具体计算方法可参考文献[4]和文献[5]。

2 滤波电路的幅频响应分析

2.1 实际电容的非理想性

理想电容的容抗为:

(5)

电源滤波电路中,需要考虑实际电容的自谐振频率和等效串联电阻(ESR)。

常用的3种电容的特点[6]如表1所示。

表1 常用低频滤波电容性能比较

电容种类极性ESR(典型值)可靠性抗冲击能力价格容值体积铝电解有1~15 Ω低强低大大钽电解有0.1~1 Ω较高弱较高小小大容量陶瓷无2~30 mΩ较高强较高小小

孤立电容的滤波效果与电源干扰输出阻抗有关,滤波效果比较有限。

2.2 RC与基本LC低通滤波电路

对于一阶RC低通滤波电路,存在极点

(6)

在极点频率外,电压的频率响应是以20 dB/10倍频程的速度下降。使用这种方式容易实现截止频率kHz级别的低通滤波器。

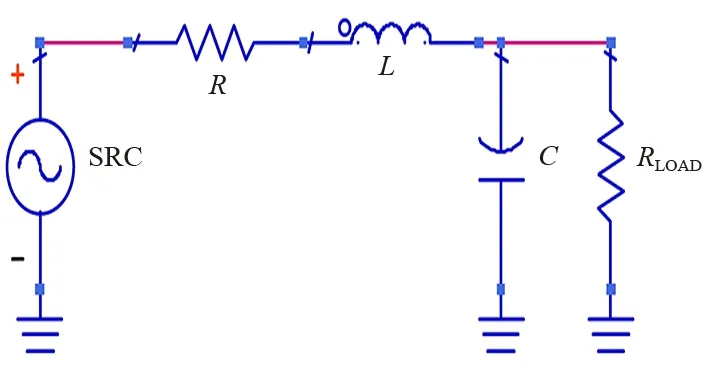

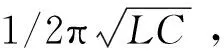

基本的LC低通滤波电路如图1所示,其中R为负载。

图1 基本LC低通滤波电路

对于图1这样的典型电路,存在谐振点[7]

(7)

和Q值

(8)

Q>1时,在谐振频率附近,负载上的电压大于电源电压。也就是说,Q>1时谐振频率处的噪声,滤波电路不仅不会抑制,反而放大了。

根据式(8),在负载不变的情况下,如果需要降低Q值,就需要减小电容C、增加电感L。在一种典型使用状态下,负载R=100 Ω,谐振频率f0=1 kHz时,根据式(8),如果需要Q<1,则电感L应大于16 mH。这样大的电感体积很大,缺乏工程实用性。所以,抑制Q值宜采用串联电阻的RLC低通滤波方式。

2.3 RLC低通滤波电路

典型的RLC低通滤波电路如图2所示。

图2 典型的RLC低通滤波电路

工程上在对幅频和瞬态响应的计算中,当通过负载RLOAD的电流不是很大时,可以忽略其影响。此时R主要由电源的输出电阻、电感的导通电阻和电容的ESR构成。RLC串联电路存在谐振点[8]

(9)

和Q值[9]

(10)

以及阻尼系数[8]

(11)

实际使用中,回路电阻R越低,Q值越高。大容量陶瓷电容的ESR低本来是优点,但用做LC滤波时Q值可达几十以上,此时噪声电压反而被放大几十倍以上,事与愿违,值得注意。

当负载电流很小时,可以在电感上串联电阻以降低Q值。Q≤1时噪声电压基本不再得到放大,此时根据式(11),回路的总电阻需要满足:

(12)

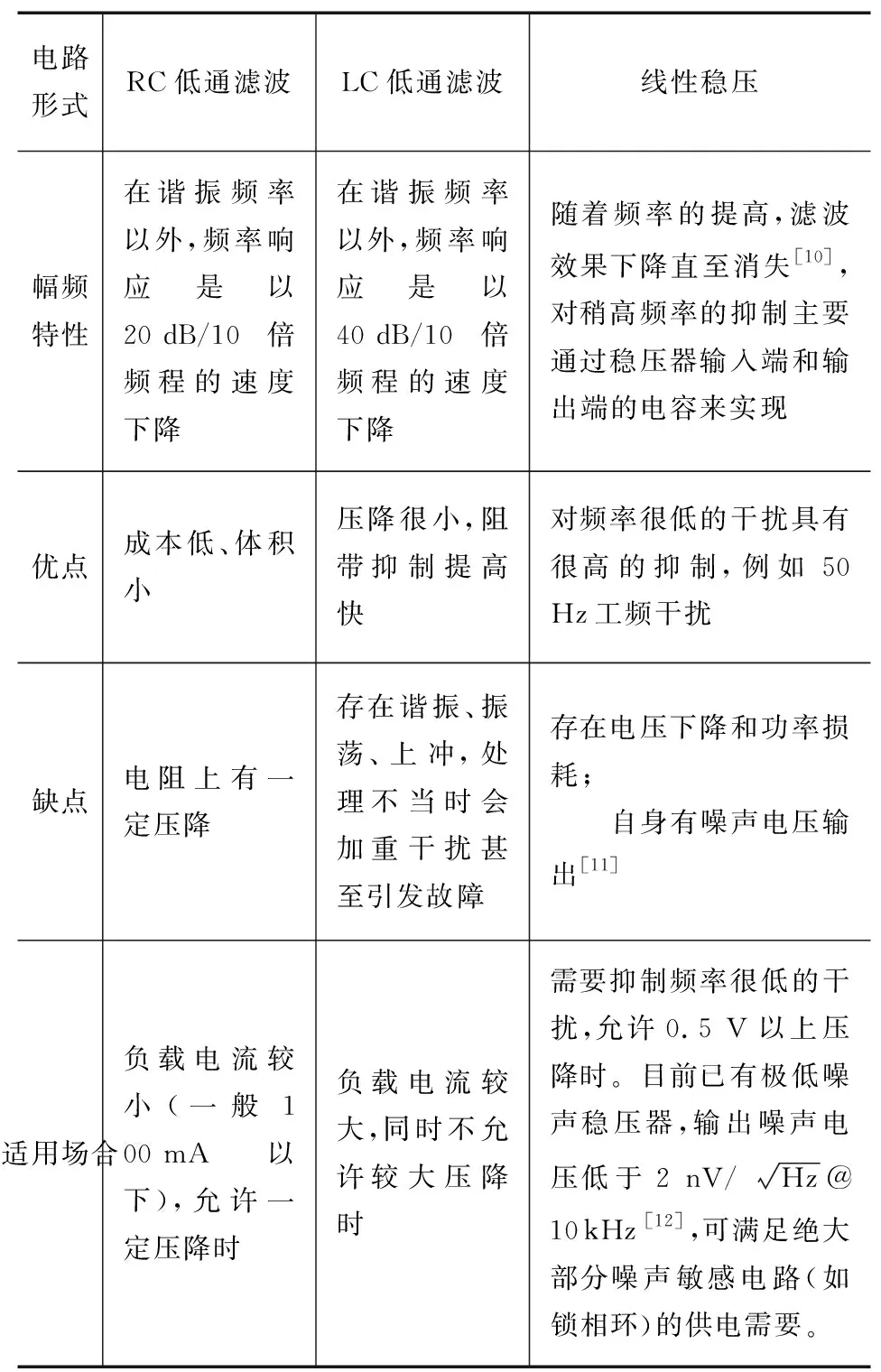

2.4 3种基本滤波电路对比

3种基本滤波电路的比较如表2所示。

表2 常用滤波电路比较

电路形式RC低通滤波LC低通滤波线性稳压幅频特性在谐振频率以外,频率响应是以20 dB/10倍频程的速度下降在谐振频率以外,频率响应是以40 dB/10倍频程的速度下降随着频率的提高,滤波效果下降直至消失[10],对稍高频率的抑制主要通过稳压器输入端和输出端的电容来实现优点成本低、体积小压降很小,阻带抑制提高快对频率很低的干扰具有很高的抑制,例如50 Hz工频干扰缺点电阻上有一定压降存在谐振、振荡、上冲,处理不当时会加重干扰甚至引发故障存在电压下降和功率损耗;自身有噪声电压输出[11]适用场合负载电流较小(一般100 mA以下),允许一定压降时负载电流较大,同时不允许较大压降时需要抑制频率很低的干扰,允许0.5 V以上压降时。目前已有极低噪声稳压器,输出噪声电压低于2 nV/Hz@10kHz[12],可满足绝大部分噪声敏感电路(如锁相环)的供电需要。

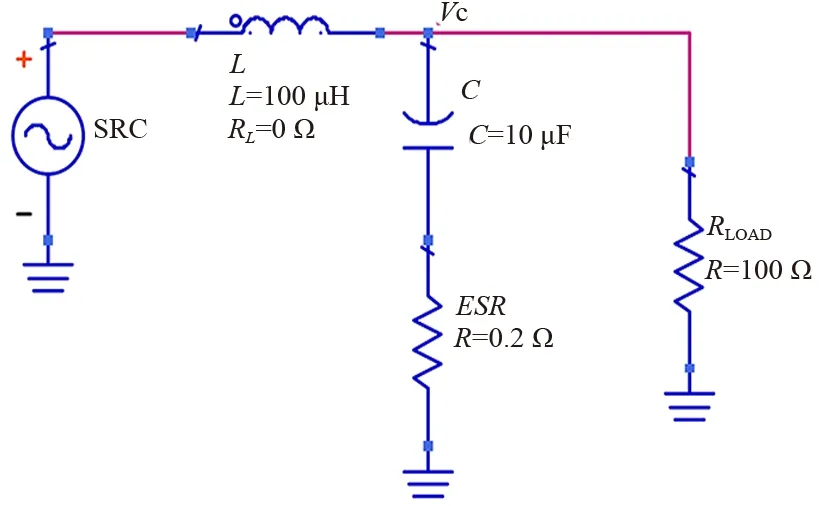

2.5 幅频响应的仿真结果

对使用钽电容的RLC滤波电路进行仿真,仿真软件采用安捷伦公司的ADS2009U1,负载设置为固定电阻。电路如图3所示,图中ESR为电容的等效串联电阻。

图3 幅频响应仿真电路及默认元件值

幅频响应(AV)的仿真结果如图4所示。

图4 幅频响应(AV)仿真结果

通过图4(a)可以看出,图3这样使用钽电容的RLC滤波电路具有明显的谐振点,该处的噪声电压被放大了20 dB以上;图4(b)说明了重负载情况下谐振情况有一定改善,但不能避免;图4(c)说明了改用大容量陶瓷电容滤波后,由于ESR明显降低,谐振现象更为严重,谐振点处的噪声电压被放大了近30 dB;图4(d)说明了增加回路电阻,使Q降低到1时,谐振消失,滤波效果较好。

3 滤波电路加电后的瞬态响应分析

加电后的瞬态响应主要关系到负载和滤波电路自身的可靠性。

3.1 固体钽电容的电流限制需要

滤波电路中,常见的是电容损坏,最多的是钽电容击穿短路,这大多是使用不当引起的。

根据GJB/Z 35-1993中的要求,固体钽电容在电路设计中应有不小于3 Ω/V的等效串联阻抗[13]。也就是说,固体钽电容的充电电流不应超过330 mA。举例来说,对于12 V电压的滤波,如果直连单个钽电容滤波,则需串联36 Ω/V的电阻,这样的设计缺乏实用性,必须采用其他手段来限制电容的充电电流。

近年来,实际工作中经常发生钽电容炸裂事件,技术人员的分析结果是国产钽电容质量不过关,最终使用进口型号替代了国产产品。事实上,这次事故就是由于使用不当,电路中未对钽电容充电电流进行限制,加电瞬间对钽电容产生过强的冲击造成的。本文认为事故处理方式并不很恰当。国产钽电容在质量上虽然与进口钽电容相比还有差距,但在合理使用的条件下可以保证较高的可靠性,并不容易出现故障,不应该被全部替换,进口钽电容也不应该允许不限流使用。在充分限流的使用条件下,例如小功率稳压器的输出端,建议优先使用国产电容,提高国产化率指标。

3.2 LC低通滤波电路的加电瞬态响应

与RC低通滤波器不同,LC低通滤波器加电后可以产生振荡。

RLC串联电路的阻尼系数λ<1时,滤波电路的电压阶跃响应存在上冲。当λ值很小时,电容上上冲的电压可以接近电源电压的2倍,这时一定要注意电容的耐压问题。

大容量陶瓷电容由于其ESR非常低,用做LC低通滤波器时,振荡问题更为严重。

振荡产生后,电容和负载电路的实际承受电压最高可接近电源电压的2倍。为保证可靠性,确定电容耐压值时,必须在实际承受的最高电压的基础上降额处理[14]。同时应该保证负载电路可承受这样的瞬态高压。可以考虑并联大ESR电容[1]、稳压二极管或瞬变抑制二极管[15]来抑制输入振荡。

电源上使用软启动功能,适当延长启动时间,对改善瞬态响应有很大好处[16]。一般来说,启动时间增加到毫秒级以上,就可以大幅提高加电瞬间的可靠性。

3.3 加电瞬态响应的仿真结果

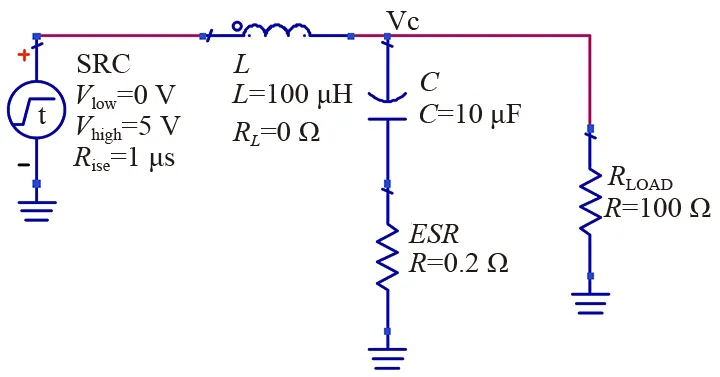

对使用钽电容的典型LC滤波电路进行负载电压的加电瞬态仿真电路如图5所示,图中ESR为电容的等效串联电阻。

图5 瞬态响应仿真电路及默认参数

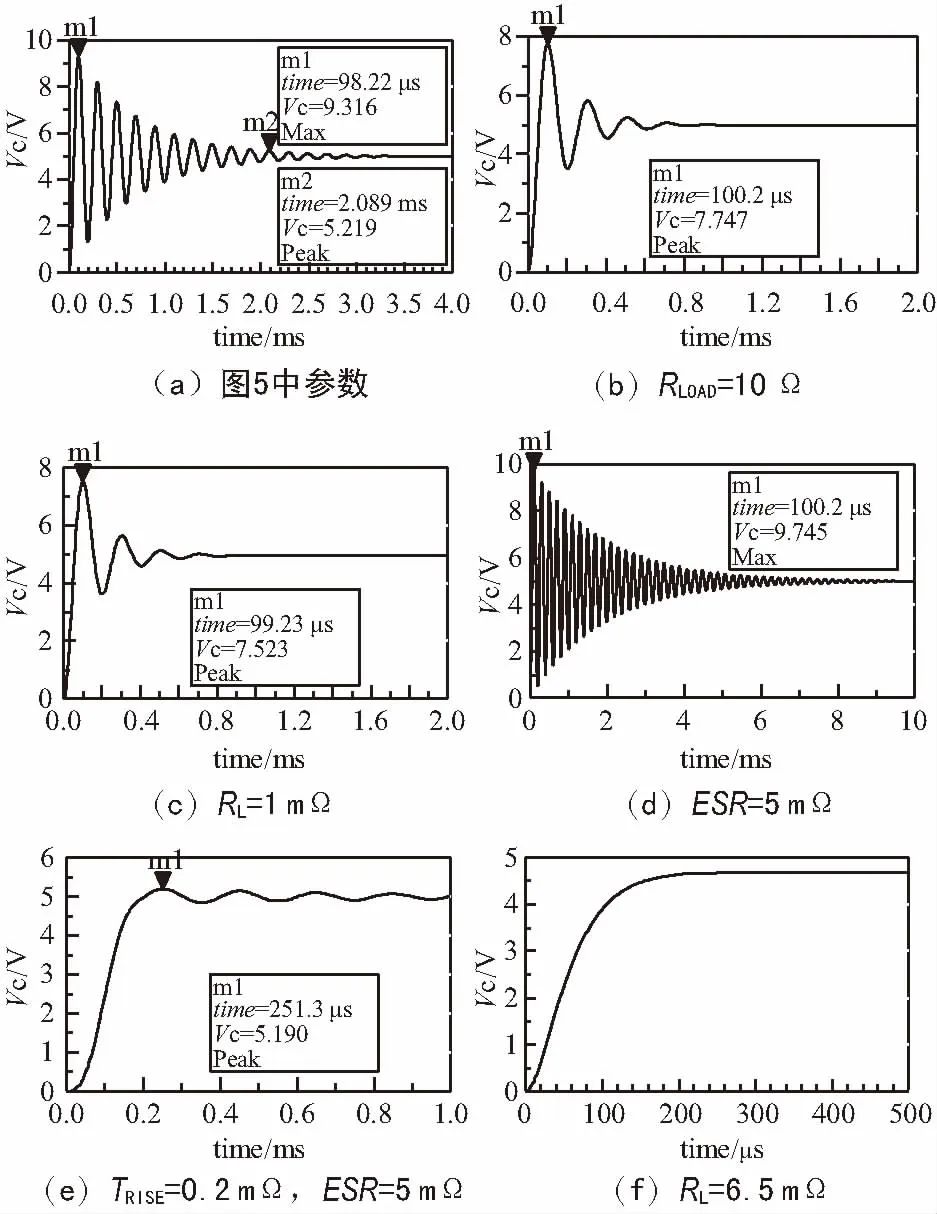

图5中电路的仿真结果如图6所示。

图6 瞬态响应仿真结果

通过图6(a)可以看出,图5这样使用钽电容的典型LC滤波电路加电后产生明显的振荡,峰值电压接近电源电压的2倍;图6(b)说明了重负载情况下谐振现象有一定改善,但不能避免;图6(c)说明了增加回路电阻时,谐振现象得到改善;图6(d)说明了改用大容量陶瓷电容滤波后,由于ESR明显降低,谐振现象更为严重,电压稳定下来的时间增加了1个数量级;图6(e)说明了将电源电压的上升时间增加到1个振荡周期时,上冲基本消失。图6(f)说明了增加回路电阻,使λ提高到1时,上冲消失,滤波效果较好。

4 结束语

电源电路设计不当是射频组件的指标下降和故障产生的主要原因之一。电源滤波电路的瞬态作用造成的电容和受电器件的可靠性问题在研制阶段难以发现,需要特别注意。

大容量陶瓷电容是近十几年发展起来的新型电子元件,用其替代以往使用的钽电容时,其低ESR造成的影响应当充分考虑。

设计电源滤波电路时,首先应当了解电源的电压上升时间及噪声情况、负载电路的敏感程度、负载电流,以及组件的设计方案和技术指标要求,估算各频率下所需的抑制度,综合考虑抑制度、瞬态响应、可靠性等因素后,确定滤波电路的形式,进行元器件选值。与照搬电路的方式相比,合理设计的电路在技术指标、可靠性、体积和成本等方面具有明显优势。