基于STM32单片机FSMC接口驱动LCD的配置与分析

2018-08-17王德生王小康姜小存

李 良,王德生,王小康,姜小存

(火箭军士官学校,山东 青州 262500)

0 引言

LCD液晶显示屏与主芯片之间有多种接口形式,比较常见的接口有 UART、SPI、FSMC、LTDC、HDMI、MIPI等。FSMC也即是灵活的静态存储器控制器,是用来驱动外部总线,在一些TFT液晶的操作用经常用到。单片机访问内存是通过三总线形式进行访问的,即地址总线、数据总线和控制总线,只是对于不同的控制芯片总线宽度不一样而已。STM32的FSMC[1]就像51系列单片机的外部总线一样,只不过性能更好,速度更快。本文主要分析基于STM32芯片FSMC接口的ILI9341液晶显示屏的控制过程。

1 硬件连接关系

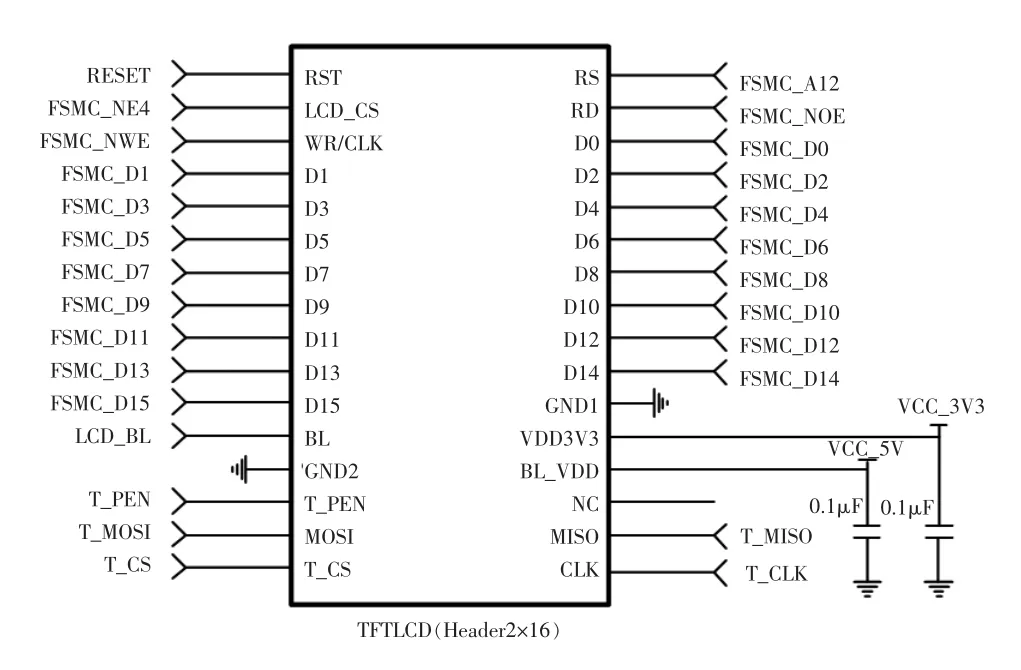

本文选用ILI9341液晶屏[2]接口是16位的80并口,16位代表有16根数据线,用STM32芯片驱动一个80并口的LCD需要7个控制信号,通过SRAM控制器控制外部LCD液晶显示屏显示。图1为本文中采用的TFT型LCD硬件引脚图,共有32个功能引脚:

图1 TFT型LCD硬件引脚

LCD_CS:Chip Select片选信号,低电平有效;

RS:Register Select寄存器选择;

LCD_WR:Write写信号,低电平有效;

LCD_RD:Read读信号,低电平有效;

RESET:重启信号,低电平有效;

DB0-DB15:数据线,与STM32相应GPIO引脚相连;

BL:背光控制信号;

其中 MOSI、MISO、T_PEN、T_CS 及 CLK 引脚在内存接口控制中未用,其余引脚与STM32相应引脚相连。STM32上有FSMC接口的好处就是一旦对其设置之后,WR、RD、DB0-DB15这些控制线和数据线,都是FSMC自动控制的。

2 NOR和PSRAM的地址映射

追本溯源,为何FSMC可以用来驱动LCD,原因是FSMC的读写时序和LCD的读写时序很相似,于是把LCD当成一个外部存储器来用。利用FSMC在相应的地址读或写相关数值时,STM32的FSMC会在硬件上自动完成时序上的控制。所以我们只要设置好读写相关时序的寄存器后,FSMC就可以帮我们完成时序上的控制了。对于FSMC驱动LCD有一个比较难理解的地方就是当LCD使用16位宽度的数据传输(也就是有16条数据线)的时,HADDR和FSMC_A这个地址块的对应问题 (使用8位数据则不用考虑此问题)。

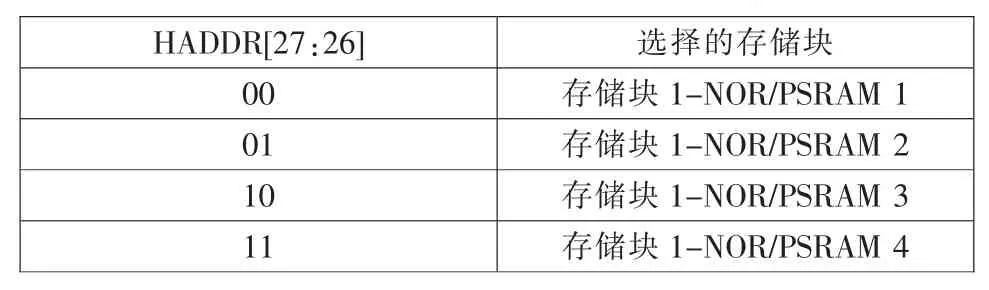

FSMC_A是STM32单片机的外部硬件接口,是物理存在的。HADDR是需要转换到外部存储器的内部AHB地址线,是STM32内部总线。当LCD的16位的80并口和STM32的FSMC接口连接好之后,我们可以进行软件编程控制HADDR,从而间接操作FSMC_A,STM32的FSMC接口将0x60000000-0x6FFFFFFF的地址用作NOR/PRAM(共256M地址范围)。存储模块分成四部分,每部分64M地址范围[1]。NOR和PSRAM的存储块选择如表1所示。

表1 NOR和PSRAM的存储块选择

本文使用NOR/SRAM的Bank1.sector4,地址位HADDR[27,26]=11,也即用FSMC_A12引脚作为数据命令区分线,0:命令,1:数据。 本文中 LCD 的 LCD_RS(命令/数据标志线)是接在STM32的外部接口FSMC_A[12]上的。

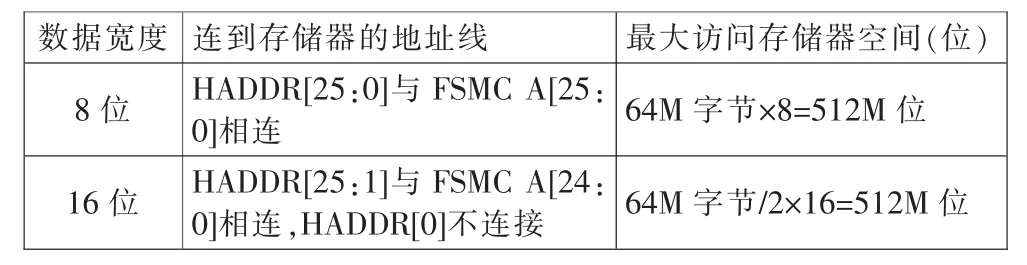

由于STM32规定当使用16位数据宽度的时候HADDR[25:1]与 FSMC_A[24:0]对应相连,HADDR[0]这个地址是没用的。外部存储器地址如表2所示。

表2 外部存储器地址

这就是当使用16位数据宽度的时候,HADDR自动右移一位对其的原理因为使用的是16位的数据宽度,所以在设置时要注意STM32内部会右移一位对齐:

3 软件配置FSMC接口

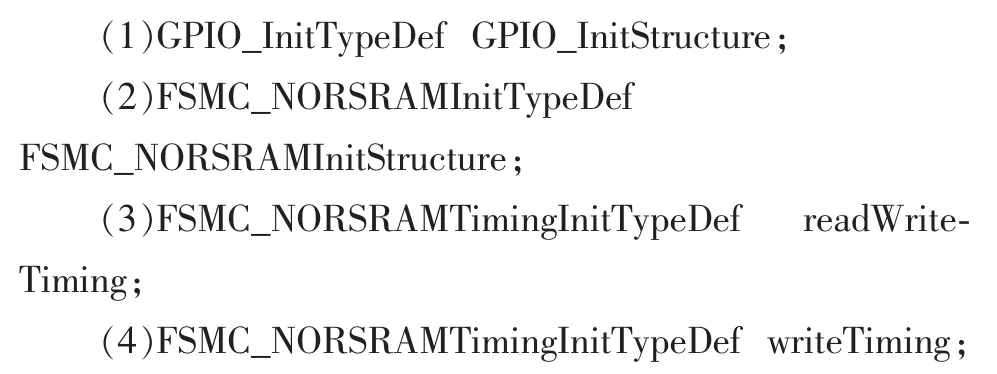

在实际编程中,根据STM32与LCD之间硬件电路连接关系,主要配置四个结构体参数[3,4]:

其中第二个结构体FSMC_NORSRAMInitStructure是FMSC接口配置最为重要的结构体,主要完成以下参数配置:

4 结束语

基于STM32的FSMC接口配置是驱动LCD正常显示的最为关键的环节,本文重点分析了FSMC接口的地址映射和软件配置,经实验验证,FSMC接口配置是可行可靠的。