基于芯片仿真验证软件实现的一种试题库与试卷库建设方法

2018-08-01赵鸿昌

赵鸿昌

(无锡城市职业技术学院 物联网工程学院,江苏 无锡214153)

《国家教育事业发展“十三五”规划》指出,未来教育信息化的重点是信息技术与教育过程相融合的创新,重点发展教育的效率和质量,并鼓励社会力量为学校提供信息化课程包和试题库及试卷库建设。与此同时,基于移动端的“雨课堂”等软件与基于PC端的“极域电子教室”等软件均已实现了课堂习题或试卷的编制和实时发布,国外也有学者研究了试卷中的习题排列顺序对学生考试成绩的影响[1]。但是,将课程试题库与试卷库作为一个整体来设计,并且从整体上提供实用的建设方法仍是国内外研究中尚未论及的,存在诸多难点。

一、试题库与试卷库建设的要求

测验与考试环节作为教学过程中检测学生学习情况的有效方法,其设计的优劣直接决定了教学质量,因此高效的试题库和试卷库历来是课程建设的重中之重[2]。然而,建设过程存在诸多实现难点。

衡量试题库优劣的标准主要包括试题能完全覆盖教学大纲规定的知识点,而且试题的形式和变体足够丰富从而避免雷同,不要成为令学生厌倦的“题海”。另外,试题库中覆盖同一个知识点的相同题型的题目必须标识为互斥题目,以方便后续试卷库的生成。

衡量试卷库优劣的标准比较多,很多与试题库的要求截然不同。尽管各类教育教学的形式千差万别,核心要求包括:①指定试卷总份数及每份试卷中每类试题的总数;②由经验丰富的教师指定每份试卷对试题库中的知识点产生有效覆盖的要求,表现为必须覆盖的知识点集合,从而避免必要知识点的遗漏;③试题抽取时要具有一定的随机性,表现为多套试卷之间试题的重复率要有上限;④能够使用试题库中标识的互斥题目的信息,避免相同知识点和类型的试题重复出现于一份试卷中。

衡量试题库和试卷库整体建设水平的另一个重要指标就是信息化工具的应用程度,这也是影响实际建设水平的重要指标。一方面,理想情况是试题抽取和试卷的排版工作要尽量自动化,以实现试题库改动后试卷库的即时生成,但是当前绝大多数情况下涉及太多的人工操作,出题人疲于应对从而令试卷库的整体建设常常流于形式。另一方面,试题库和试卷库软件本身的研发效率也是一个重要考量,而能解决上述问题的此类软件的研发一般是非常困难的,只能考虑借用现有的成熟软件解决最核心、最难以实现的随机约束生成问题。

笔者在此背景下提出一种实用的试题库与试卷库建设方法,通过分析芯片仿真验证领域的随机激励生成的原理,找到激励生成与试卷生成之间的共性,然后通过面向对象的仿真验证语言System Verilog予以抽象建模,将试卷生成问题转化为基于芯片仿真验证软件的随机约束生成问题。本文详细阐述了建模机制及实现技巧,在信息化教育教学领域具有很强的实用性及推广价值。此外,以成熟的芯片仿真验证软件为基础解决试题库与试卷库的建设问题,对于教育信息化软件的研发尤其是快速原型化也提供了很好的借鉴。

二、试卷生成软件的工作原理

尽管上述对试卷生成的要求繁多复杂,但是经过分析可见试卷生成软件的核心难点在于试题的约束随机抽取功能、试题按知识点的覆盖功能以及试卷的自动排版功能。笔者结合自身在大规模集成电路仿真验证领域的工作经验,发现原理上只要将每道试题是否出现于试卷中编码为1位数字量,则每道试题即可与集成电路仿真验证时的一个二进制输入测试激励相对应。因此,前两个核心难点完全等同于集成电路仿真验证时多个位宽为1的测试激励的随机生成,采用目前成熟的集成电路仿真验证软件实现是完全可行的。

试卷生成软件的工作原理如图1所示。首先准备好试题库,直接用记事本程序编辑并保存为文本文件即可,每行一道试题。然后在此基础上按试卷库的建设要求书写System Verilog程序并仿真,最后根据仿真结果从试题库中多次抽取试题组成试卷,并完成试卷的格式排版。需要着重指出的是试卷的自动排版使用成熟的Latex排版软件实现,生成的PDF文件不但比Word文件格式更稳定从而方便阅读和打印,而且整个排版过程完全可以一键自动运行。可以预见,在素质教育的大背景下,试卷生成的终极目标是按学生定制化,即根据每个学生的知识点掌握情况即时生成最适合个体学习的试卷,因此Latex排版软件亦是未来试卷库建设必不可少的工具。

图1 试卷生成软件的工作原理图

三、集成电路System Verilog语言的应用

众所周知,在描述和处理复杂问题时要用相对复杂的编程语言。System Verilog语言作为一种面向对象的集成电路建模与仿真软件,输入激励的随机约束生成是其最基本的功能,还提供了灵活的描述硬件行为的类与封装机制,例如更规范的System Verilog类库框架是2011年提出的通用验证方法学 (Universal Verification Methodology,UVM),其应用了集成电路建模与仿真领域最新的面向对象技术[3]。System Verilog对试卷生成问题的适用性表现在以下几点:

1.问题建模与映射

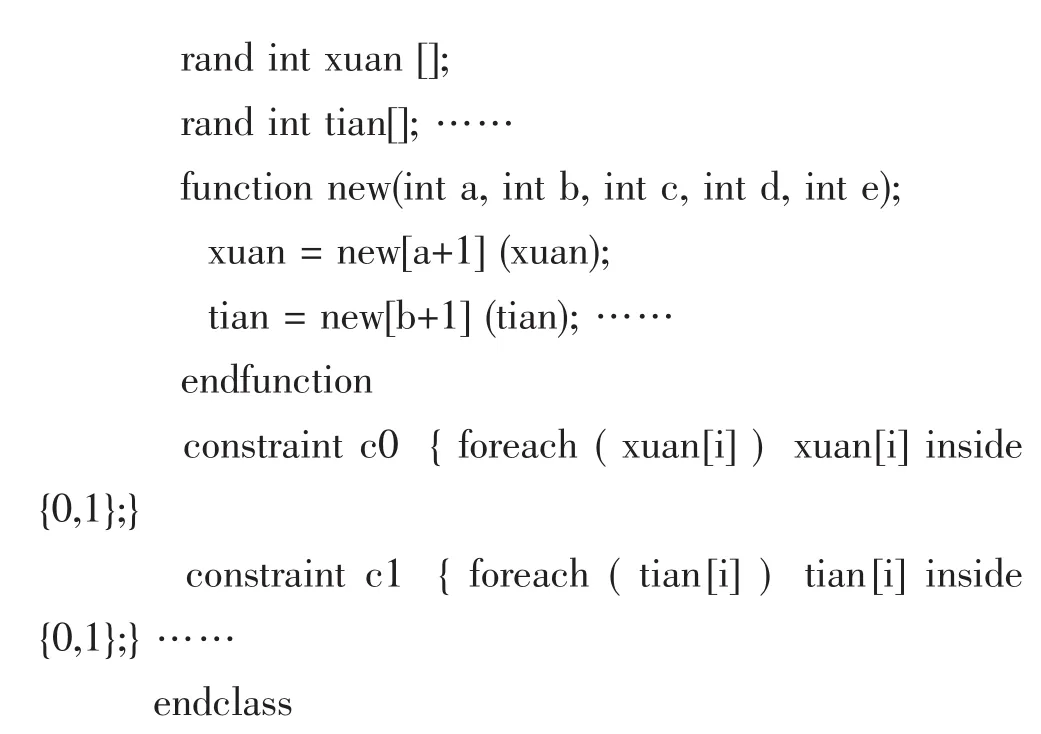

首先,试题库中的试题按教材的章号和题型组织,一份试卷中的试题则来自多个章节并具有不同的题型,因此自然地将每章抽象为一个chapclass类。该类的成员变量包括5个随机数组以对应于5个题型的题目,数组中的元素数目在构造函数中设置,每个元素只能取值0或1,取为1表示此章中此题型的某道题是否出现在试卷中。由此可见,chapclass类中最重要的约束是诸如以下核心代码中的c0二进制约束,表示每道选择题是否出现在试卷中。

因为试卷中的试题可归于教材的相应章节,所以将试卷建模为一个名为paper的类,类中的成员变量只有16个实例化的chapclass对象,分别描述课程教材中共15章的题型及相应的试题数量。为理解与设计方便起见,chap[0]不使用,并且每个数组中的0号元素均不使用。试卷paper类的构造函数中设置各章的各类题型及题量,其关键代码如下:

由代码可见,第二章中的选择题、填空题、名词解释、简答题以及综合题依次各有 10、6、3、2、1 道。

至此,试卷生成问题就等效为试卷paper类中的各个对象chapclass的按约束随机化,每次随机化的结果是一串取值为0、1的数,1表示需要抽取出的题目。paper类的多次约束随机化即可生成多份试卷。因为System Verilog语言最显著的特性正是输入激励的约束随机化,它完全适用于试卷生成问题,其余的建模工作即是在paper类中设定对试卷的各类约束。

2.题目总量约束的实现

生成试卷时首先需要指定各类题型的试题总量,例如,用以下System Verilog功能块实现对综合题共有两道的约束。

以上约束C5表示第1到第5章各有1道综合题而第9章则有2道综合题,需要从中随机取出共2道生成试卷。

3.互斥题目与知识点覆盖的实现

约束1==chap[1].xuan[1]+chap[1].xuan[2]+chap[1].xuan[3]就可以限定试题库中第一章的前三道选择题只能取一个,从而避免相同知识点的相同类型题目重复出现在一份试卷中。而约束1==chap[1].xuan[1]+chap[1].tian[1]+chap[1].zong[1]则表示第一章中某一知识点对应的不同类型的题目要出现一次,至于是以选择或填空或综合题的形式出现则完全由仿真软件随机确定。

由此可见,各种形式的试题抽取原则上均可以灵活地映射为System Verilog语言中提供的约束功能。

4.多份试卷的生成

生成多份试卷只需要对paper类的多次随机实例化,可以用System Verilog语言中的循环命令repeat来实现。例如以下代码段中的repeat(N)表示生成N份试卷,每次生成则只需调用函数randomize()进行一次不同的随机化。可见,如下System Verilog程序的运行过程包括100次随机实例化paper对象并将随机化的结果打印为一串0或1的数字,依次代表试题库中的相应题目是否要出现在试卷中。

5.试卷的相似率检测

不同试卷中的题目需要满足一定的相似率要求,即限制同时出现在两份试卷中的题目总数。一种实现方法是构建更大的类,例如构建试卷库repos类并包含100个paper对象作为成员变量,然后将相似率约束写在repos类中即可,但是仿真实践表明相似率约束的数目出现了组合爆炸,如此实现的仿真速度大幅降低。另一种简单的方法是基于每份试卷表现为一串0或1的数字这一特点,用简单的C语言程序实现多串数字的对比和统计。以本文为例,只要仿真时指定的试卷份数略大于100,就可以用C语言程序快速筛选出相似率符合要求的100份试卷,实现过程简单,此处不再赘述。

四、试题抽取与试卷排版

以本文为例,试题库中共有177道题,因此100份试卷对应的仿真结果文件中包括一串共17700个0或1的数字。首先用Linux中的split命令将其分成100个文件,并命名为paperxx.txt,然后按每个文件中所指定的0或1抽取试题,例如抽取选择题的Linux脚本命令如下:

结合tiku.txt中选择题的格式“章号 题型 题目 答案”,上述第1行命令表示将第一份试卷的0、1数字号与试题库内容按列拼接起来,并且按题型排序后只取出以“1”开头的题目。随后的 grep“zz.*zz1zz”过滤出所有题型1即选择题。之后的脚本命令均为Latex排版软件要求的文件输入格式,例如使用iconv命令从GBK到UTF-8的转码就是因为Latex排版时的中文宏包默认支持UTF-8编码。

图2是生成的试卷首页,试卷答案和试题纸未作展示。试卷头信息包括试卷名称、系别专业、姓名、学号以及评分卡等事先作成一个PDF文件,然后用tikz宏包提供的pgfimage命令插入到试卷的开头。然后将自动抽取出的题目及答案分类组织即可,所有抽取与排版工作全是Linux脚本命令一键完成的。

图2 排版后的试卷样例

五、结束语

信息技术的运用是无所不在的,本文展示的是丝毫不相关的芯片仿真验证用到的System Verilog程序解决试卷的自动生成问题。整个项目的实现过程巧妙,具有很强的参考价值。

当前的不足主要包括:①素质教育大背景下,试卷生成的终极目标是学生定制化,即根据每个学生的知识点掌握情况即时生成最适合个体当前发展水平的试卷,每个学生都能实现学习能力的最优发展。这是试卷生成领域很难的研究课题,需要探索学生知识点掌握情况的量化指标。②现有研究与实验结果大多数都将学生的考试成绩作为最终考量点,没有将学习理论中的知识结构图作为首要考量点,深入研究知识点网络的特性与知识点掌握程度之间的关系,给教育信息化带来了前所未有的挑战,值得进一步研究和实践。③试题库的编辑界面要改进为更易用、更反映知识结构的用户界面,例如思维导图界面对于出题者的知识结构理解和调整就大有裨益。最后一点改进是利用芯片时序分析软件PrimeTime的路径分析功能,来梳理大规模耦合知识点之间的逻辑关系,以期利用机器学习技术从深层次上为学生挖掘出更利于自主发现新知识的试题,这将加速信息时代学习、应用与创造的融合,为实现未来高效率、高质量的素质教育提供前瞻性的理论研究成果。