一种SAR极坐标格式成像算法的FPGA实现

2018-07-25朱岱寅胡晓琛

李 威 朱岱寅 胡晓琛

(南京航空航天大学电子信息工程学院雷达成像与微波光子技术教育部重点实验室 江苏 南京 211106)

0 引 言

合成孔径雷达[1-4]在地形测绘、资源探测以及灾害监测等军用和民用领域都有广泛的应用,因此高精度的SAR实时成像成为研究的热点问题。在聚束SAR成像[5-7]模式中,插值能够实现极坐标格式算法PFA(Polar Format Algorithm)中的两维数据坐标格式的变化。文献[5]针对SAR成像PFA中不同的插值方法从距离向和方位向的分辨率、最大旁瓣电平以及计算量等方面进行了详细的分析,最终推出截断有限点数的SINC插值优于其他插值方法,且8点SINC插值优于4点SINC插值的结论。本文采用SINC插值实现PFA中的两维数据重采样,因此SINC插值是影响极坐标格式SAR成像算法计算速度和精度的重要因素。近年来,采用可编程门阵列FPGA(Filed Programmable Gate Array)进行SAR数据实时处理取得了飞速发展[8-11]。FPGA采用硬件并行架构,功耗低,资源丰富数据吞吐量大,DSP的串行处理架构决定了它本身的局限性,因此采用FPGA对于信号处理过程复杂、数据量大的SAR实时成像进行处理是最佳的选择。文献[8]提出的FPGA实现SINC插值的方法是将采样点数据缓存到整块RAM中。该方法经过8个周期选出8个采样点数据,并根据8点SINC插值原理加权求和得到插值结果。这种方法虽然在FPGA上实现了SINC插值,但并没有实现流水线形式输出数据,速度不快,没有发挥FPGA并行结构的优势。文献[9]在FPGA平台上利用横截型FIR滤波结构设计了7点SINC插值模块,该方案同样也不能实现插值结果的流水线输出。

针对上述方法的不足,本文提出了一种基于分块RAM组的并行结构SINC插值方法,应用于两维插值极坐标格式成像算法的FPGA实现。首先将采样点坐标经过浮点转定点操作,以结果的整数部分寻址分块RAM组存储回波数据和定点数的小数。分块RAM组由8个子块RAM组成,它们可以同时进行寻址操作,在一个周期内找到所有满足8点SINC插值条件的采样点数据,并且没有增加占用的FPGA资源。最后对找到的采样点数据进行加权求和,流水线输出待插点结果,理论上本文方案的效率是串行实现方式的8倍。此外,文中还对基于SINC插值的极坐标格式成像处理系统资源的占用情况、处理速度以及计算精度进行了分析。系统时钟频率200 MHz,在Xilinx 公司生产的VCT690T 开发板上处理8 KB×8 KB机载SAR实测数据用时约1.78 s。对实测数据进行验证,该方案的运算速度可以达到SAR实时成像的需求,具备实用性。

1 极坐标格式算法

聚束SAR工作模式的几何模型如图1所示,其中斜视角为θs,在正侧视的情况下航迹与x轴平行,假设雷达做匀速直线运动,速度为v。θ和φ分别是雷达天线相位中心APC(Antenna Phase Center)的瞬时方位角和俯仰角,在合成孔径中心处分别为0和φ0。雷达天线相位中心的瞬时坐标为(xa,ya,za),在孔径中心时刻为(0,yc,zc)。场景中分布点目标P,其位置矢量为rt=(xt,yt,0)。Ra和Rt分别为天线相位中心到场景中心和目标的瞬时距离矢量,瞬时距离值分别为Ra和Rt。

图1 聚束SAR数据采集几何模型

为了使原点处回波相位为零,需要对回波数据做运动补偿和匹配滤波,同时利用驻留相位原理可以得到成像处理前的信号格式为:

(1)

式中:τ为快时间变量,Tr为脉冲宽度,k为信号线性调频斜率,fc为发射信号载频,信号带宽B=kTr,其中c为电波传播速度,t为方位慢时间,Ta为方位孔径时间。

基于平面波前假设,Ra-Rt可以用下式表示:

(2)

将式(2)代入到式(1)中得到的信号模型为:

(3)

可以得到点目标的距离徙动曲线可表示为:

RCMB(t)=

(xtcosθs+ytsin2φ0sinθs)cosφ0Ωt+

ytcosφ0+ο(t3)

(4)

从信号耦合的角度来看,极坐标格式算法就是通过插值来去除耦合,通过插值使得式(3)中距离和方位的距离徙动部分均变成距离频率fτ和方位时间t的线性函数。

为了消除距离向上的耦合,对式(3)做如下尺度变换:

(5)

RCMR(t)=ytcosφ0+xtcosφ0tanθ

(6)

式中:

(7)

将式(7)代入到式(6)中可以得到:

RCMR(t)=ytcosφ0+xtcosφ0cosθsΩt-

(8)

距离向校正完成之后,距离向变量yt的解耦合完成,剩余只与方位向有关的徙动需要消除。

接下来对经过距离向处理的数据进行方位向重采样,继续对式(3)做如下变量替换:

(9)

经过距离向和方位向插值之后,此时目标距离徙动曲线为:

RCMKT(t)=ytcosφ0

(10)

可以看到,经过方位向插值后,距离徙动曲线中与方位向变量有关的距离徙动得到全面的校正。因此高效、高精度的插值可以信号解耦合快速、准确的完成。

目前常用的插值算法有线性插值、多项式插值、三次样条插值和SINC插值等。线性插值虽然简单便捷但处理精度不高。多项式插值和样条插值结构涉及除法和循环迭代,实现结构复杂,利用FPGA实现时程序复杂度高。SINC插值的点目标聚焦效果较好,而且SINC插值本身结构基于卷积架构,核心为乘和累加,适合FPGA实现。综合考虑资源、精度和算法复杂度,本系统选用SINC插值进行PFA成像。根据8点SINC插值原理,采样点坐标处于[W-4,W+4)范围内所有回波数据与对应的SINC系数相乘并求和即可获得该待插点的插值结果。其中,SINC系数的计算公式为:

(11)

式中:W是待插点坐标,Wi是采样点坐标。8点SINC插值的时域重建方程为:

(12)

式中:fd(i) 是f(x) 在x=i处的采样值,实际上就是用SINC系数对回波数据进行加权求和得到插值结果。

2 两维插值SAR成像的FPGA设计方案

2.1 系统的整体结构

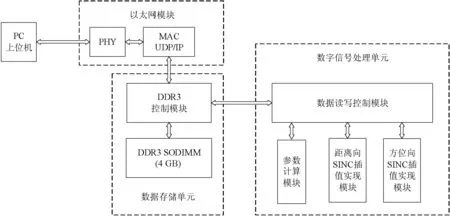

本方案SAR成像处理系统所处的板级结构如图2所示。分析上述原理可知,对方位向和距离向数据进行高效、高精度的插值可以保证距离徙动得到准确的校正[12]。本系统处理的是雷达采样的回波数据,在FPGA中进行处理的数据格式是单精度浮点型复数。

图2 系统板级结构

图2中所示的板级结构包括三个主要模块:以太网数据传输模块、DDR3数据存储模块以及数字信号处理模块。其中三态以太网数据通信模块通过SFP-GE-T型收发器[13]、ISE中的IP(Intellectual Property)核及UDP/IP协议实现,它确保了大量SAR数据在PCB板和PC之间快速、低出错率的传输。数据存储单元通过调用MIG(Memory Interface Solution)核,对用户接口端的信号进行控制,实现对回波数据、中间处理结果的存储和转置读写。数字信号处理单元基于PFA成像算法对FPGA的逻辑架构和时序进行协调控制,从而实现对采样数据距离和方位向处理进而完成高分辨SAR成像[13];为了满足SAR实时成像的需求,并且基于FPGA并行架构的特点,距离向和方位向数据重采样均使用SINC插值实现,最大程度地压缩FPGA实现信号处理的时间。该系统工作在200 MHz的时钟频率下,数据从PC传输到板卡的DDR3中暂时存储,经过PFA成像算法处理后,成像结果再由以太网高速传输接口以及外接的SFP收发器传输到PC上位机中进行显示成像。

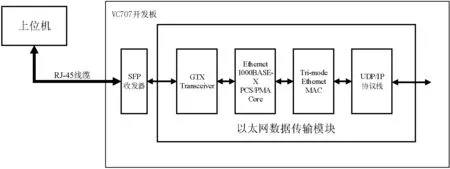

2.2 以太网数据传输模块

在进行SAR成像处理过程中,回波数据和成像处理结果数据通过以太网模块实现在上位机和FPGA板卡之间的传输[14]。本设计用Xilinx提供的LogiCORE IP Ethernet 1000BASE-X PCS/PMA实现物理层;Xilinx提供的三态以太网介质访问控制器解决方案IP Tri-Mode Ethernet MAC完成物理地址寻址、数据的组帧、检错重发等数据链路层的功能;UDP/IP协议栈分别实现网络层和传输层的功能。图3显示的是以太网模块内部的构成及在整个系统架构中的位置。

图3 以太网传输模块结构图

2.3 数字信号处理单元

本方案使用两维SINC插值实现数字信号处理单元中的距离向和方位向数据的重采样[15],这里重点介绍了在FPGA上实现基于分块RAM组的SINC插值算法。在距离向和方位向处理过程中都是调用的这个SINC插值模块。图4是基于并行RAM组实现SINC插值的流程图。

图4 基于并行RAM组的SINC插值算法流程图

本文方案在资源占用率不变的情况下,极大加快了插值速度。整个SINC插值过程可以分成四个步骤进行,下面以插值长度为16 384为例,对每个步骤进行详细的介绍。

步骤一:缓存采样点数据。由于时序上采样点数据和坐标不能同步输入到插值模块中,需要将输入的采样点数据暂时缓存至FIFO。

步骤二:采样点坐标浮点转定点。本方案设计首先将浮点型采样点坐标转化成定点型坐标,定点型数据整数位宽的设置要保证不会溢出,本文中设置为16位。同时,为了满足16等分SINC量化系数表的要求,小数位宽的设置要大于或等于4位,本文中设置成16位。

步骤三:以定点型采样点坐标的整数为地址存储采样点数据和采样点坐标的小数部分。RAM中一个地址只能存储一个数据,如果两个及以上采样点坐标整数部分相同而小数部分不同,就会出现前面一个坐标的数据被具有相同整数部分的数据覆盖的情况。本方案结合机载实测数据,经过验证最多会出现两个采样点坐标具有相同的整数部分,本文中分别设定两组相同的分块RAM组,即Data_RAM1、Data_RAM2和X_Fraction_RAM1、X_Fraction_RAM2。本方案采用如图5所示的RAM组存储结构。该RAM组由8个独立的子块RAM组成并按照箭头方向顺序存储数据。假设采样点坐标的整数部分为Entire_address,在子块RAM中的地址为,Sub_RAMi表示第i个子块RAM,两个地址之间的关系式可以表示为:Entire_address=8·Sub_address+i,其中Entire_address∈[0,16 383],Sub_address∈[0,2 047],i∈[0,7]。

图5 并行分块RAM组结构图

图6给出此步骤实现过程的编程举例。

图6 数据存储程序举例

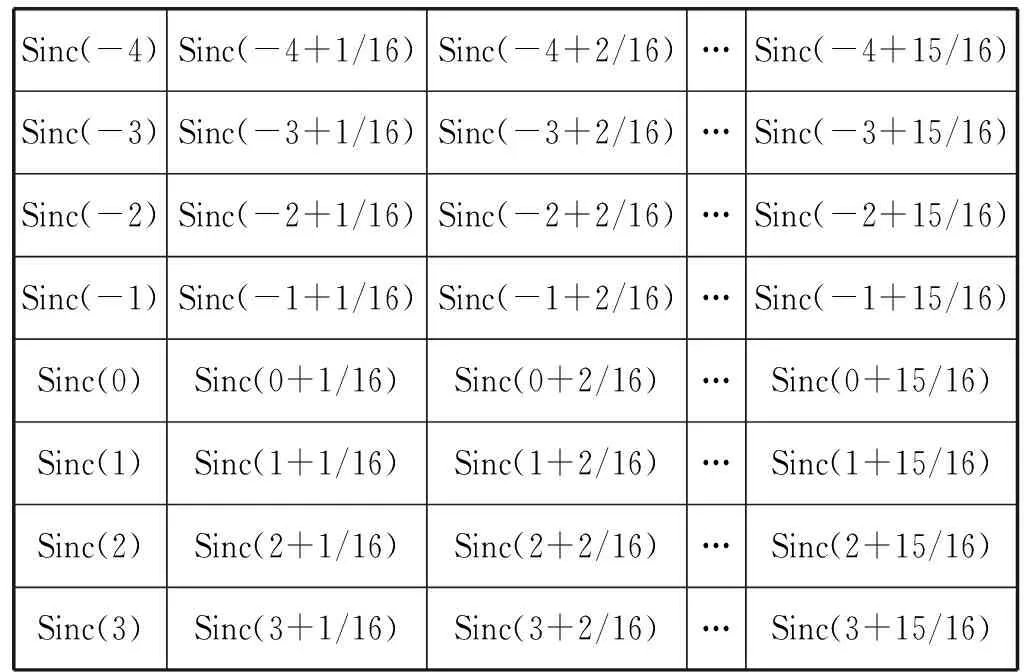

步骤四:插值结果的计算。在步骤三中,按照采样点坐标的整数为地址对回波数据进行存储,假设待插点的坐标为W(W是整数),即由Entire_address为W- 4、W-3、W-2、W-1、W、W+1、W+2、W+3时,计算出8个子块RAM的Sub_address,寻址存储的回波数据和小数部分,取出待插点周围满足条件的采样点。然后,通过小数部分在SINC量化系数表中找到对应的SINC系数。其中,在FPGA中采用的SINC系数量化的方式如表1所示,它主要将每个单元距离均分成16份,从而实现对SINC系数的量化。最后,根据该SINC系数对回波数据进行加权求和得到最终插值结果。

表1 SINC插值核系数表

本方案通过设置子块RAM组,可以在一个周期内对8个子块RAM进行寻址操作,从而实现插值结果的流水线输出,没有增加占用的FPGA资源;相比于文献[6]的串行实现方式,处理速度提高了7倍;另外本方案中一次插值处理的点数是16 384,插值点数可以实现向下兼容。

2.4 数据存储模块

由于进行SAR成像需要处理的数据量大,比如本文中提到的图像大小为1 GB,使用FPGA的片内资源是远远不够的,本系统采用DDR3 SDRAM对回波数据和中间结果进行存储。在具体设计实现过程中采用Xilinx公司提供的内存接口解决方案MIG(Memory Interface Solution)IP核。该IP核提供了一个简单的内存控制器,但是在进行SAR信号处理时,需要能够实现对距离和方位数据的转置读写、对读写地址和操作长度的控制。为了结合SAR信号处理需要的功能,需要在调用IP核的同时在IP核外部增加逻辑控制单元。图7是本设计方案中的实现数据存储模块的用户接口模块图。

图7 用户接口模块结构图

3 SAR实测数据处理结果与分析

在分析实验结果时,本模块是在以Xilinx公司Virtex7系列的xc7vx690t芯片为处理核心的处理板上进行验证的,当系统时钟频率为200 MHz时,成像处理系统用时 1.78 s完成8 KB×16 KB点的数据处理。Matlab的处理过程是在硬件配置为Intel(R)Core(TM)i7-4890 CPU@3.60 GHz处理器上进行的,单线程完成同样处理耗时为1 546.091 9 s,对比可知FPGA在实现数据处理加速方面的效果相当显著。表2显示的是各个信号处理模块中MATLAB处理时间和FPGA处理时间的对比情况。

表2 MATLAB与FPGA处理时间比较

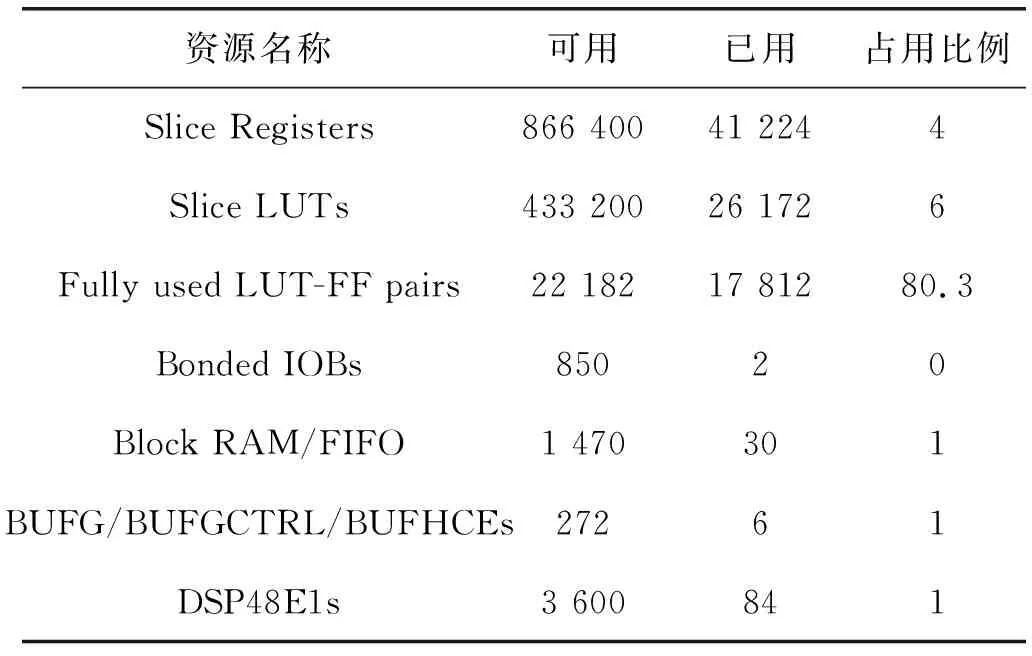

整个基于两维插值极坐标格式算法的FPGA系统包括数字信号处理模块、DDR数据存储模块、以太网数据传输模块以及参数计算模块,该系统在xc7vx690t芯片上综合得到资源占用情况,如表3所示。

表3 资源占用情况

本文通过计算FPGA和MATLAB的相对误差对基于分块RAM组的SINC插值模块进行误差分析,相对误差的计算公式为:

(13)

本文方案SINC插值的FPGA实现与MATLAB之间的相对误差如表4所示,在数值上可以看出基于分块RAM组实现的SINC插值精度高、误差小。

表4 相对误差

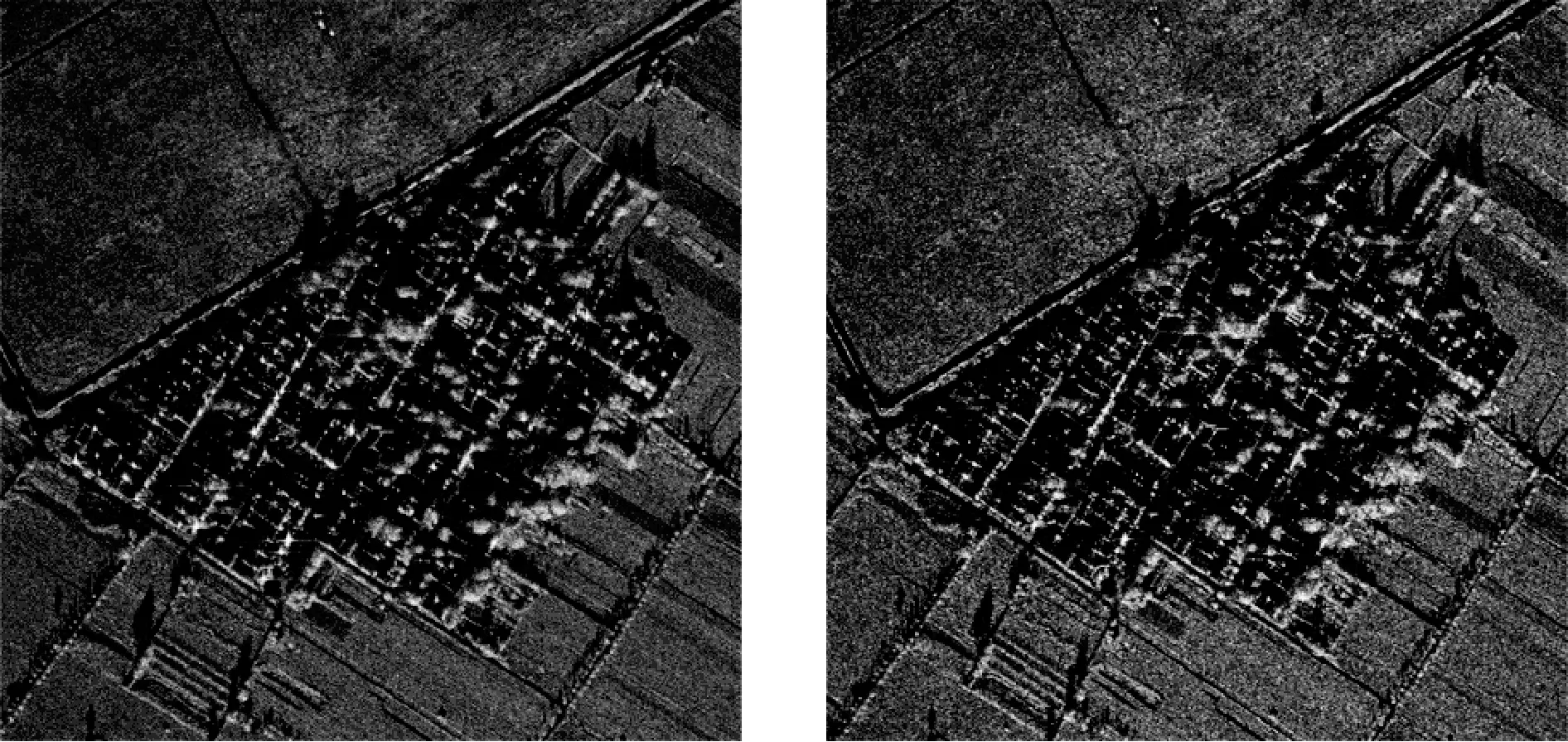

图8是FPGA和MATLAB分别对大型机载SAR录取的实测数据处理结果的对比图,表5是该组大型机载实测数据对应的参数,图8(a)和(b)分别使用FPGA和MATLAB对实测数据进行处理得到的SAR图像,(c)和(d)分别是(a)和(b)的局部放大图。

(a) FPGA处理结果 (b) MATLAB处理结果

(c) FPGA处理结果局部放大 (d) MATLAB处理结果局部放大 图8 FPGA与MATLAB处理结果图

v/(m·s-1)122R0/m5 000H/m7 155θs/(°)0.56λ/m0.03fs/MHz512B/MHz420Tr/μ16PRF/Hz1 799

可以看出,两者整体效果几乎完全相同,FPGA成像处理结果能够清晰地反映地貌状况和地面纹理信息。同时局部放大图效果相差无几,全面地展示了目标场景的细节信息,聚焦效果明显。因此两维SINC插值的SAR成像系统的精度满足SAR成像的处理要求。

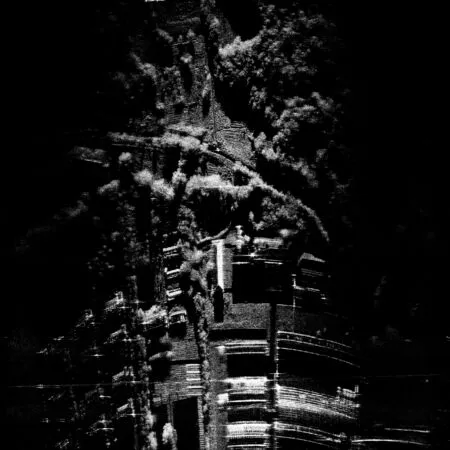

另外,本系统不仅可以用来处理大型机载SAR的回波数据,还可以对MiniSAR系统的回波数据进行成像处理,能够应用于MiniSAR系统的实时成像当中。图9显示的就是本系统对MiniSAR系统回波数据的成像处理结果,该结果与使用MATLAB进行处理得到的成像处理结果相同。表6是MiniSAR系统录取回波数据的参数。图9的成像分辨率没有图8高,这是因为两种数据采用的雷达发射电磁波的带宽不同,所以成像效果的分辨率不同。通过图片可以看出本FPGA成像系统的成像效果清晰,能够清晰地反映地面纹理信息。图10显示的是本系统应用于MiniSAR系统的实物图。

表6 MiniSAR系统数据参数

图9 MiniSAR飞行数据图像

图10 本系统的应用场景MiniSAR实物图

4 结 语

本文提出了一种基于两维SINC插值极坐标格式SAR成像算法的FPGA实现方法。在实现SINC插值时重点在于如何快速高效地找到待插点周围满足条件的贡献点,利用FPGA的并行架构流水线输出SINC插值结果,将存储回波数据的整块RAM分成8个子块RAM,在同一个周期内实现对8个子块RAM的寻址,实现每隔一个时钟周期输出待插点的计算结果。同时,本文所提方法,没有增加资源消耗率,能够并行输出插值结果,同时极大地缩短了成像处理时间,为基于两维SINC插值的极坐标格式SAR实时成像的实现提供了可行性。