增强型AlGaN/GaN HEMT势垒层优化设计

2018-07-23郭伟玲吴月芳

雷 亮,郭伟玲,都 帅, 吴月芳

(北京工业大学 信息学部,北京 100124)

GaN 基材料的优良物理特性如高电子饱和速度,高击穿场强,以及良好的导热性等使得GaN材料成为目前全球半导体研究的前沿和热点,也是研制微电子器件、光电子器件的新型半导体材料,并与SiC、金刚石等半导体材料一起,被誉为是继第一代Ge、Si半导体材料、第二代GaAs、InP化合物半导体材料之后的第三代半导体材料。GaN具有宽的直接带隙、强的原子键、高的热导率、几乎不被任何酸腐蚀的化学稳定性等性质和强的抗辐照能力,在光电子、高温大功率器件和高频微波器件应用方面有着广阔的前景。

GaN的电学特性是影响器件的主要因素。由于AlGaN/GaN 界面的压电极化效应和界面两侧的 AlGaN 层、GaN 层的自发极效应的存在使得AlGaN/GaN 异质结界面形成高浓度的二维电子气(1.1×1013cm-2)和高电子迁移率(2 185 cm2·V-1·s-1),非有意掺杂的GaN在各种情况下都呈n型,最好的样品的电子浓度约为4×1016cm-3[1-2]。由于常规的 GaN 器件是常开型器件,在不施加栅极偏压时,漏极就会有电流通过,为了抑制漏极电流,就需要向栅极施加负电压,如发生栅极无法控制的情况时,电流就会一直处于流动状态,这将导致器件被烧坏。所以GaN电力电子器件为了安全工作,在实际应用过程中,必须首先确保实现与普通硅器件一样的常关,即在栅极电压为零时,漏极没有电流产生。因此,增强型AlGaN/GaN HEMT器件实现常关模式及抑制电流崩塌现象的研究得到了重视。

目前基于AlGaN/GaN异质结结构制作的增强型HEMT器件主要实现方法有:薄势垒层、槽栅结构、栅下区域氟等离子体注入、栅极注入结构等[3-7]。为进一步探索和优化P-GaN栅增强型AlGaN/GaN HEMT器件的电学特性,采用Atlas进行仿真模拟,研究了AlxGa1-xN势垒层厚度H及Al组分X对器件转移特性、输出特性、耐压特性的影响以及对增大漏极偏压时电流崩塌效应产生程度的影响。

1 器件模型

Atlas模拟软件是基于载流子连续性方程、漂移扩散输运方程、泊松方程,利用二维有限元的分析方法来得到器件的电学特性[8]。仿真中所使用的器件模型如图1(a)所示,该器件结构,是来源于文献[9]具有P-GaN栅的GaN HEMT器件。器件基本参数如下:2 μm的AlGaN缓冲层,35 nm GaN沟道层,未掺杂AlxGa1-xN势垒层厚度为H分别取10 nm,15 nm,20 nm,25 nm,30 nm,Al组分X分别取0.2,0.23 0.25, 0.3,P-GaN采用均匀Mg掺杂浓度为3×1017cm-3,器件的栅长为1.4 μm,栅源和栅漏间距分别为1 μm和6 μm。在栅源和栅漏电极间采用Si3N4作为钝化层。

图1 器件模型

模拟采用栅极选择性生长PN结方法来制作增强型AlGaN/GaN HEMT器件,利用栅极零偏压时栅极pn结较高的内建电势使器件沟道电子耗尽。这里P-GaN栅HEMT是在器件的栅下和未人为掺杂的AlxGa1-xN势垒层之间引入Mg掺杂的P-GaN材料,栅电极与P-GaN形成欧姆接触构成栅极注入结构晶体管[9-10]。AlxGa1-xN势垒层形成具有内建电压VF的pn结,由于栅极下P-GaN掺杂会提高能带势垒高度如图1(b)所示,在栅极零偏压时使栅下沟道电子耗尽,从而实现增强型器件特性[10-12]。此外,当栅极偏压低于内建电压VF时,器件以场效应管原理工作;当栅极偏压高于内建电压VF时,将使空穴从P-GaN 注入沟道,同时沟道电子向栅极的注入则被AlGaN/GaN界面势垒阻挡,注入的空穴将从源极吸引等量的电子以保持沟道的电中性,这些电子在漏极电压的作用下以高迁移率移动到漏极,而空穴迁移率比沟道内电子低约两个数量级,位于栅下沟道区域。这一动态的电导调制作用明显增加了漏极电流而保持较小的栅极电流[13-14]。

2 仿真结果与讨论

仿真中ATLAS设置的部分模型:使用了Shockley- Read-Hall复合模型consrh、俄歇复合模型auger、迁移率模型GaNsat.n、本征费米模型ni.feirmi、考虑晶格的自加热效应lat.temp参数,设置压电极化参数和自发极化参数,设置衬底热接触的热阻倒数alpha=2 500 W/(cm3·K)。其中源极和漏极肖特基金属的功函数设置为4.04 eV,栅极金属与P-GaN为欧姆接触,为保证仿真的精确程度和速度对器件结构网格在材料接触界面进行细分。

2.1 势垒层厚度变化对器件输出特性的影响

图2所示为AlxGa1-xN势垒层 Al组分X=0.2,厚度分别取10 nm,30 nm时对栅极电压步进时的两组输出特性曲线。由两组曲线可见随着栅源电压Vgs增加,漏极饱和电流也逐渐增大,且在对应栅极偏压下,势垒层为30 nm时的输出特性曲线均比10 nm时高。在5 V栅压下沟道已完全开启,当栅压>4 V时,随着漏极偏压的增加,漏极饱和电流会出现下降且势垒层为30 nm时下降较10 nm时更明显,该现象可由电流崩塌效应解释[15],即是一种在漏极施加高电压达到一定临界值时,由于大量电子聚集在通道旁边而造成沟道动态导通电阻增加的现象。该现象持续长时间发生会使器件过热,导致器件损坏和误操作,从而给器件带来灾难性的后果。

图2 不同栅压和势垒层厚度变化时输出特性曲线

图3为同一栅极偏压Vgs=3 V下,Al组分取X=0.2,AlxGa1-xN势垒层厚度分别取10 nm,15 nm,20 nm,25 nm,30 nm时的输出特性曲线,比较图中5条曲线可发现,随着势垒层厚度的增大,漏极电流逐渐增大,导致这一变化的原因是势垒层厚度的增加使得沟道内二维电子气浓度增加了,且势垒层厚度越大,随着漏极偏压增大而产生的电流崩塌效应会越显著。

图3 不同势垒层厚度的输出特性曲线

2.2 势垒层厚度变化对器件转移特性的影响

图4为AlxGa1-xN势垒层厚度变化时的转移特性曲线,沟道内二维电子气的浓度随着H增加而逐渐增大,使器件开启电压逐渐减小至低于1 V。由于增强型器件在取得较大漏极饱和电流Idsmax时,首先要保证栅压对器件沟道有较强的控制能力[9],开启电压要求尽量满足Vth>1V。当H=10 nm时,Vth=2.4 V>1 V,Idsmax=0.17 A;H=15 nm时,Vth=1.5 V>1 V,Idsmax=0.28 A;H=20 nm时,Vth=1.1 V>1 V,Idsmax=0.38 A;H>25 nm时,Vth=0.5 V<1 V。综上分析得出势垒层厚度取15~20 nm为宜。

图4 势垒层厚度变化时的转移特性曲线

2.3 势垒层厚度变化对器件击穿特性的影响

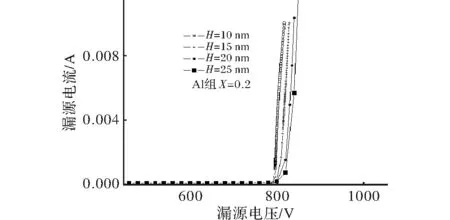

图5为不同AlxGa1-xN势垒层厚度的击穿特性曲线,当固定Al组分为X=0.2时,随着势垒层厚度增加,击穿电压也会增加,耐压值从势垒层10 nm时的800 V变化为25 nm的841 V。

图5 不同势垒层厚度的击穿特性曲线

2.4 Al组分变化对器件输出特性的影响

综合考虑之前模拟结果势垒层厚度不易超过20 nm,现固定势垒层厚度H=15 nm。为方便观察Al组分渐变对漏极临界饱和点右移及电流崩塌效应的影响,图6为同一栅极偏压Vgs=3 V,Al组分取0.2,0.23,0.25,0.3时的输出曲线,在Al组分X=0.3时,漏极临界饱和点明显右移,且电流崩塌效应明显。导致这一现象的原因是,Al组分增加也会导致二维电子气密度增加,且过大的Al组分会引起势垒层应变弛豫,令异质结材料恶化。

图6 不同Al组分的输出特性曲线

2.5 Al组分渐变对器件转移特性的影响

图7为固定势垒层厚度H=15 nm, AlxGa1-xN势垒层中Al组分渐变时对器件转移特性的影响。随着Al组分的增大,沟道内二维电子气的浓度逐渐增大。当Al组分X=0.2时,使得器件的开启电压达到2 V,但是漏极电流较小;当Al组分取X=0.3时使得器件的开启电压逐渐减小至低于1 V ;由于增强型器件在取得较大漏极饱和电流时,首先要保证栅压对器件沟道有较强的控制能力,综合上述原因认为Al组分X取0.2~0.25较为理想。

图7 Al组分变化的转移特性曲线

3 结束语

本文利用Atlas完成对了P-GaN栅增强型AlGaN/GaN HEMT的势垒层厚度及Al组分的模拟优化,为取得器件良好的电学特性,势垒层厚度应该控制在15~20 nm范围,Al组分应控制在0.2~0.25之间。为了增大器件的漏极电流可适当增加势垒层厚度和Al组分。但为了保证栅极的控制能力提高增强型器件的开启电压及同时减小电流崩塌效应的产生,势垒层厚度H不易超过20 nm、Al组分X不易超过0.25,过高的势垒层厚度和Al组分反而会给增强型HEMT带来不利的影响。故在设计器件时要综合这几方面的考虑,选取最优化的器件结构。