基于ARM和FPGA超声波压电陶瓷数字变频驱动*

2018-07-11,,,,,,

,,,,,,

(1.长沙理工大学 物理与电子科学学院,长沙 410114;2. 长沙亿旭智能科技有限公司;3.近地空间电磁环境监测与建模湖南省普通高校重点实验室)

引 言

压电陶瓷是一种能够将机械动能和电能之间互相转换的陶瓷材料,它的原理是压电效应,压电陶瓷具有正压电效应和逆压电效应[1]。通过压电陶瓷的逆压电效应可以生成超声波信号,且功率可调,广泛应用于超声换能器、超声波焊接、超声波清洗、医学美容、超声马达等[3]。目前国内主要压电陶瓷驱动存在精度、发热、低频特性低和零点漂移等问题[4],因此研究一种频率精度高、功率大的压电陶瓷是本设计的主要目的。本文研究的是利用ARM控制FPGA产生死区可调的PWM波,实现调节输出频率、输出电压的功能设计。通过以IGBT为驱动元件的H桥输出,经滤波后变为频率、电压可变的正弦信号驱动超声波探头。

1 相关原理介绍

1.1 超声波压电陶瓷数字变频驱动原理

压电陶瓷材料是工业发展过程中可以进行机械能和电能之间互相转化的材料,它的原理是压电效应,所谓压电效应就是压电陶瓷材料(微位移器)可以对电能和机械能进行互相转化[2]。当把电能与压电陶瓷作用它会发生形变,如果作用的电能是持续性的,那么压电陶瓷就可以不断形变产生不同的频率波;如果频率超过20 kHz就生成了超声波,这就是压电材料逆压电效应。

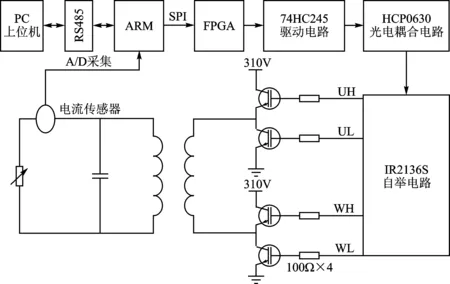

利用逆压电效应可以把高频电压转化为高频率的振动,从而产生超声波。该系统的结构如图1所示,电路中ARM芯片采用STM32F103系列CPU。

图1 超声波压电陶瓷驱动实现原理图

系统主要分为控制板和驱动板两个部分:控制板主要是通过FPGA产生4路PWM波输出(UH/UL/WH/WL),频率在16~40 kHz之间变化。 FPGA产生的PWM输出信号,其输出频率、占空比、死区时间等数据由ARM通过SPI总线通信送来。而改变输出数据,或者停止PWM输出的控制,均由ARM负责。ARM通过RS485串口连接LCD触摸屏或者PC电脑上位机,实现人机交互功能。因此超声波陶瓷所需要的输出频率和电压、功率等参数均可通过LCD来设置。另外CPU通过交流电流、电压传感器采集压电陶瓷的工作电流与电压并计算出实际输出功率,ARM将它与设定的输出功率比较,通过PID控制方法改变输出PWM波的占空比,从而达到调节输出电压与功率的目的。

驱动板采用了工频交流电直接供电,220 V/50 Hz的交流电通过全桥整流和电容滤波后,获得一个约310 V的直流电压。控制板产生的PWM波经过驱动电路74HC245芯片增强信号后,通过光耦隔离电路后引入驱动板,然后4路信号通过IR2136S自举升压驱动后由IGBT组成H桥电路。最后通过变压器隔离降压,电容滤波后输出驱动超声波压电陶瓷产生相应频率的超声波。

1.2 PWM波原理

PWM的基本原理是:以正弦波作为逆变器的调制输出期望单极性PWM波形,然后用频率比期望波形高很多的等腰三角波来作为载波(Carrier wave) ,再用频率与所要形成的波形相互统一的正弦波作为调制波(Modulation wave)。

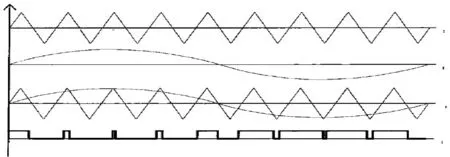

当调制三角波与正弦波曲线发生相交时,在其相交时刻输出控制信号, 用于控制功率器件的开通与关断, 通过这样的方式就可以获得一系列所需要的幅度相等且脉宽正比于对应区间正弦波曲线的函数值的矩形脉冲。即把正弦波平均分成n等分,再用与其等面积的矩形脉冲来替换每等分的正弦曲线,用以替换的矩形脉冲的幅值恒定,各脉冲的中点与每等分的中点重合,这样所得到的矩形波就与期望的正弦波等效。这种调制方法称作正弦波脉宽调制,这种序列的矩形波称作PWM波[9]。单极性PWM的原理图如图2所示。

图2 单极性PWM原理图

本设计中,通过IR2136S驱动两对IGBT功率管,共4路PWM输出,分别是UH、UL、WH、WL,无重叠的PWM信号UH/UL为一对,称为上管与下管,上管和下管不能同时导通,利用输出波的死区时间来设置导通时间,死区可以改变PWM波的输出大小从而也可以达到调节输出电压大小、调节输出功率的目的。

图3 死区产生原理图

由于本设计中使用的开关器件的特性,在这里需要设置死区。死区时间被插入到一个开关器件的关断和另一个开关器件的导通之间。设置死区其实就是用来保证在任何情况下,每条支路上在一个开关器件没有完全关断时,另一个开关器件不导通。极端的情况包括用户装载了一个比占空周期更大的死区值或占空比为100%或0%的死区值。设置死区也就是产生某种延时,这种延时使得一个开关器件在开启前,另一个开关器件已完全关断。所需要的延时时间是由开关器件的开启或关断特性和负载的特性所决定的即设置合适的死区值[7]。死区产生的波形如图3所示。图3中输入的是FPGA的主频时序,然后利用程序设计输出的一对(两路)PWM波如UH/UL,输出两路波形的波峰和波谷,它们是利用死区时间错开的,避免同时导通,虚线时间段表示两路波的死区时间。

2 硬件设计

驱动电路硬件部分主要分为4大模块:主控制器模块、电源模块、通信模块与显示模块,主控制器模块采用FPGA+ARM系统架构,主要用于产生PWM信号。

2.1 主控制器模块

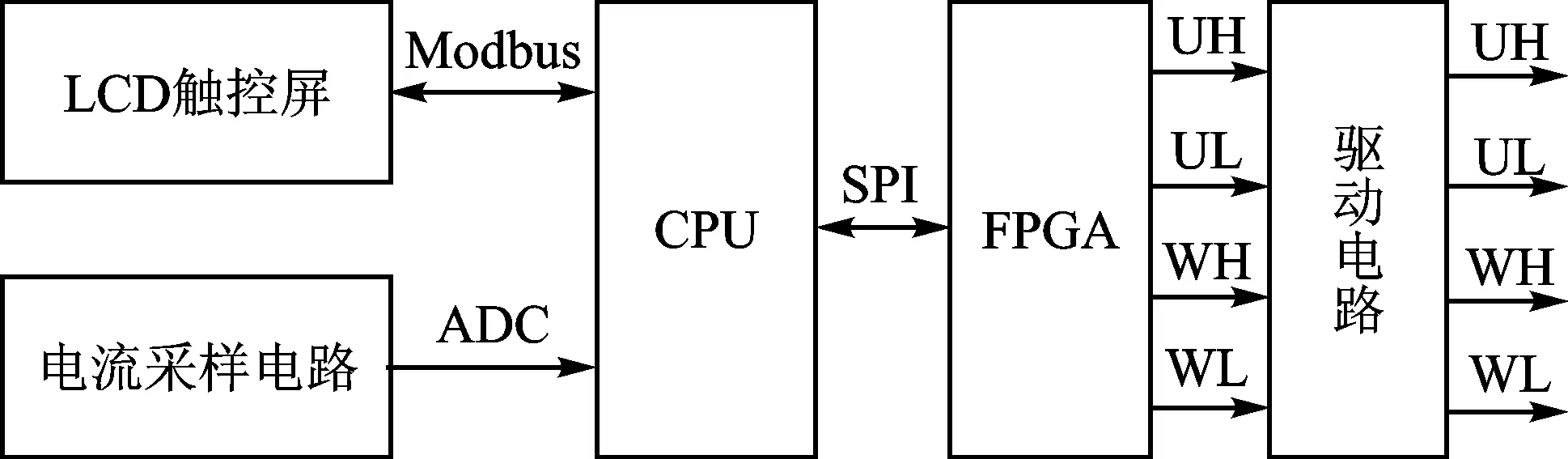

主控制器模块的ARM处理器通过RS485与上位机连接,再通过Modbus通信协议的方式接收上位机发送的频率、死区时间等参数,然后利用SPI总线将数据发送给FPGA,产生所需要的PWM波。考虑到FPGA驱动能力有限,此处加入74HC245驱动芯片来提高驱动能力,随后输出4路PWM波。控制部分结构如图4所示。

图4 控制部分结构图

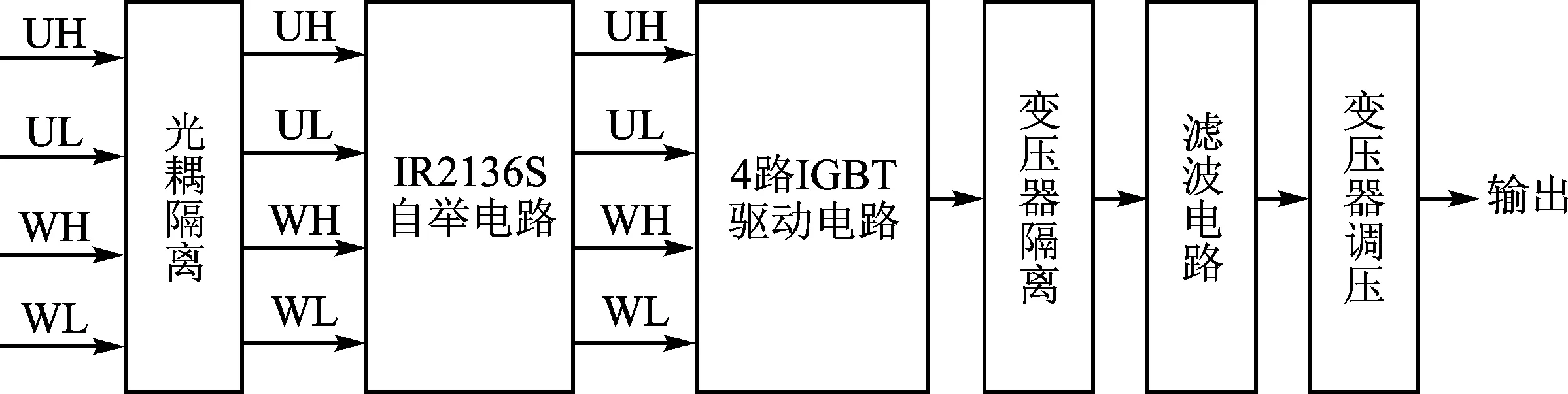

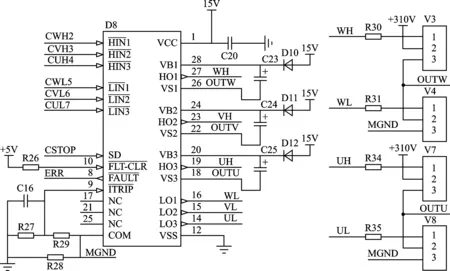

FPGA产生的4路驱动信号通过光耦隔离电路后引入驱动板,通过IR2136S自举后驱动由IGBT组成的H桥电路。最后通过变压器隔离降压,电容滤波后输出驱动超声波压电陶瓷产生相应频率的超声波。驱动部分结构图如图5所示。

图5 驱动部分结构图

2.2 电源模块

超声波压电陶瓷数字变频驱动的输入端采用工频交流电直接供电,220 V/50 Hz的交流电通过全桥整流和电容滤波后,得到一个310 V左右的直流电压,电路如图6所示。

图6 输入电源整流电路

主电路通过控制IGBT开关器件的导通与关断实现DC-AC的转换。这里利用FPGA产生的带死区的PWM波来控制IGBT的开通和关断[7-8]。采用单相H桥电路,下面来说明基本原理。H桥驱动电路原理图如图7所示。

图7 H桥驱动电路

图7中输入直流电压为E,RL代表负载。当开关Q1、Q4接通,Q2、Q3断开时,电流流过Q1、RL、Q4时,负载上的电压极性是左正右负,电流从左流向右;当开关Q2、Q3接通,Q1、Q4断开时,电流流过Q3、RL、Q2时,负载上的电压极性是左负右正,电流从右流向左,电压和电流极性与之前反相。若两组开关Q1、Q4和Q2、Q3以某个频率f交替切换工作时,负载RL上就可得到频率为f的交变电压Uo,其数值等于E[9-10]。本设计的开关Q1、Q2 、Q3、Q4是由开关器件IGBT来代替的。输入的控制信号是带死区的PWM波形,由FPGA产生。H桥IGBT具体驱动电路如图8所示。

图8 H桥IGBT驱动电路

2.3 通信与显示模块

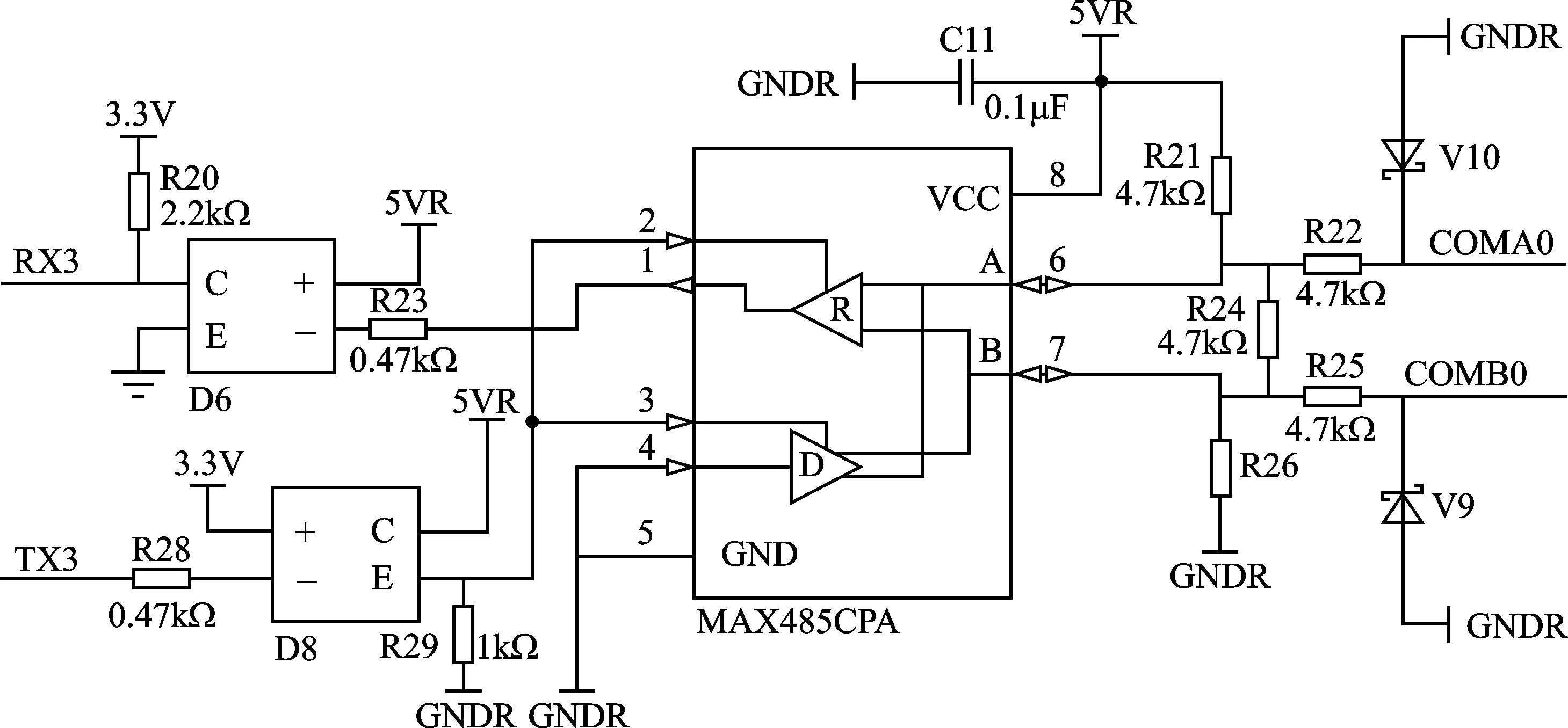

电源输出频率、功率在LCD触控显示屏上显示,ARM将数据通过串口线传送给LCD触控显示屏,通信采用的是Modbus协议。LCD触控显示屏,而电源控制板作为从机,主机和从机可以互相请求和应答。LCD触控屏界面主要显示输出电压、频率。通信模块由RS485器件及其外部电路组成。 RS485通信模块电路图如图9所示。

图9 RS485通信模块电路图

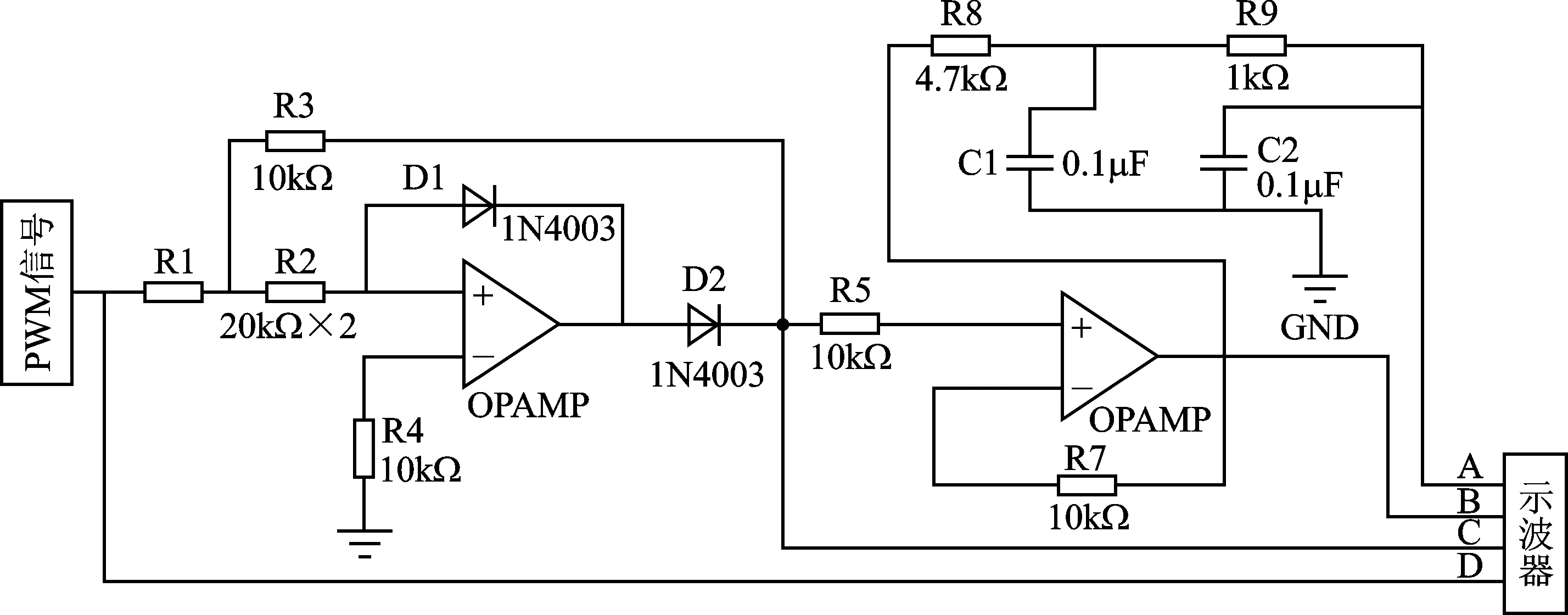

图10 电路原理图

在输出显示部分,本设计加入了电流电压传感器用于检测输出电流和输出的电压,由CPU的DMA做A/D采集。主控CPU采集处理后送LCD显示,同时能改变电流值进行反馈调节,提高电路输出稳定性[10]。本设计的超声波频率在20 kHz以上,A/D采集范围过高。采用单运放T型全波整流可以很好地解决问题,整流、滤波后输出电流电压在A/D采样范围内,整流电路R1=R2=2R3,设置增益为1/2,输出端是同相放大器,增益设置为2。具体电路及仿真如图10和图11所示。

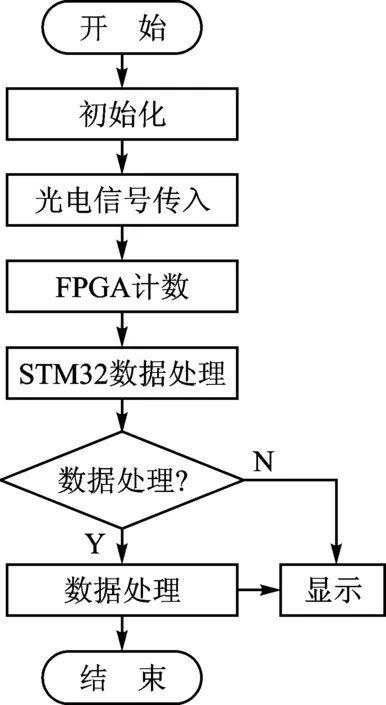

3 系统软件设计

系统软件要完成PWM波的产生、RS485数据控制和数据处理通信等功能,因此主程序设计包括了FPGA信号产生、STM32数据控制处理、数据校正和显示等。该系统的主程序流程图如图12所示,两路光电数据的采集是在FPGA中完成,采集数据实质为光电信号的低电平脉冲时间,包括标准棒的时间和待测工件的时间。FPGA将计数时间通过SPI协议传输给STM32微控制器,STM32接收数据后进行数据计算,再将计算的工件结果通过串口发送到上位机中,上位机对数据进行实时显示,还可以对结果进行校正调试。

3.1 FPGA生成PWM波程序设计

通过SPI发送4个字节给FPGA来控制PWM输出的占空比。.spi接收4个字节的数据,暂时只用了两个,预留两个做备用。T0:设置频率,地址为0;T1:设置电压,地址为1。相当于放到一个数组中,有4个16位的元素。

module PWM_Out(

sys_clk,

图11 Proeus仿真波形

图12 主程序流程图

sys_rst_n,

mosi,//定义spi的时钟、数据、片选

sck,

Rstn_T,

T0_clk,

clk_25m,

LED3,

LED4,

testpin_bank4,

testpin_bank3,

testpin_bank2,

testpin_bank1,

clk_out,

F_STOP,//停止驱动芯片

F_ERROR,//驱动芯片报

//错信号输入

clr_error_in,//CPU 的报警

//清除信号

F_ERROR_OUT,//驱动器报错

//信号输出CPU

jumper_new_pcb,//IR2136=1,IR2131=0;

cpu_clk,

pwm_out_UH,

pwm_out_UL,

pwm_out_VH,

pwm_out_VL,

rs232_tx//串口发送

);

3.2 FPGA和单片机 SPI数据传输模块

实现STM32发送数据给FPGA,使FPGA芯片输出的SPW波按正弦信号输出,同时将输出信号送入驱动板。代码。

通过改变Modbus的设定频率改变输出信号的频率,输出PWM的频率在16~50 kHz之间可以调节。改变Modbus的电压控制死区的范围,死区越大则输出功率越低,死区越小输出功率越大。

4 实验结果与分析

4.1 FPGA计数、晶振倍频

FPGA的晶振50 MHz倍频到150 MHz,计数150 MHz主时钟,计数值设置为T,则对应超声波输出的频率为150 M/T。例如输出频率设置为20 kHz则150 000 000/7 500=20 000 ,也就是FPGA计数7 500次。

例化PLL产生模块:

//50 MHz倍频150 MHz

pll pll_inst {

CLKI(sys_clk),//PLL输入时钟50 MHz

STDBY(locked),

//PLL输出有效标志位,低表示PLL输出有效

RST(pll_rst),//PLL复位信号,高电平复位

CLKOP(clk_150m),//PLL输出150 MHz时钟

CLKOS(clk_200m)//PLL输出200 MHz时钟

};

endmodule

4.2 实验数据结果分析

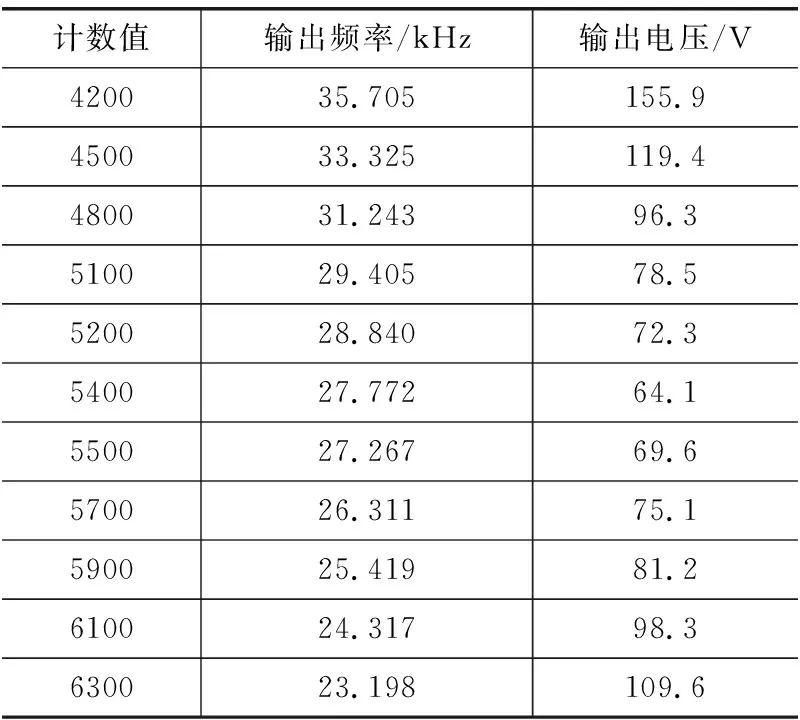

为了测试产生的超声波信号是否可以驱动换能器,对普通的一款超声波换能器进行测试,其共振频率在28.34 kHz,然后对其相关性能进行测试,通过设置FPGA的计数值从而改变其输出频率。设计数值为T,相关值如表1所列。

表1 超声波换能器测试数码

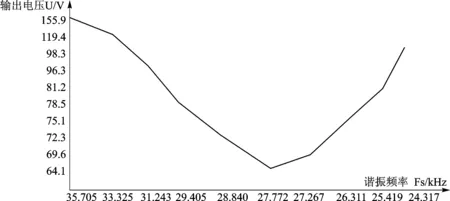

图13 频率与输出电压

实际输入的电压为310 V,考虑测试安全性采用的输入电压为30 V,输出电压和谐振频率特性图如图13所示。当频率在27.772 kHz附近时,输出的电压是最小值,说明此时换能器处于共振状态,也就是处于它的工作频率,这说明测试的这个换能器(28.34 kHz)实际工作频率应该在27.772 kHz。

结 语