通过I2C总线接口的MCU 固件升级方法

2018-07-11

(珠海市光联通讯技术有限公司 OMS/软件组,珠海 519030)

引 言

嵌入式系统(Embedded system)是一种“完全嵌入受控器件内部,为特定应用而设计的专用计算机系统”,根据英国电气工程师协会的定义,嵌入式系统为控制、监视或辅助设备、机器或用于工厂运作的设备。与个人计算机这样的通用计算机系统不同,嵌入式系统通常执行的是带有特定要求的预先定义的任务。由于嵌入式系统只针对一项特殊的任务,设计人员能够对它进行优化,减小尺寸降低成本。

Linux是类Unix操作系统,是一个基于POSIX和UNIX的多用户、多任务、支持多线程和多CPU的操作系统,用C语言写成,符合POSIX标准的类Unix操作系统。

Linux是一款免费的操作系统,用户可以通过网络或其它途径获得,并可以任意修改其源代码,这是其它的操作系统所做不到的。正是由于这一点,来自全世界的无数程序员参与了Linux的修改、编写工作,程序员可以根据自己的兴趣和灵感对其进行改变,这让Linux吸收了无数程序员的精华,不断壮大。

Linux内核的主要模块(或组件)分为以下几个部分:存储管理、CPU和进程管理、文件系统、设备管理和驱动、网络通信,以及系统的初始化(引导)、系统调用等。

本系统主机采用的是Linux嵌入式操作系统。

1 系统构成

本系统由主机和从机构成,主机采用嵌入式Linux操作系统,从机为K20 MCU,主、从机之间采用I2C总线通信方式:

从机MCU型号是恩智浦MK20DN512ZVLL10-ND,自带I2C总线接口和SCI接口(备用),通过I2C总线接口与主机通信;通过SCI接口可与PC机通信。

2 系统硬件I2C总线部分原理图

系统硬件I2C总线部分原理图如图1所示。

图1 I2C部分原理图

3 从机MCU firmware升级实现方法

从机MCU firmware升级主要有两种方法:通过PC和通过主机。

方法一:通过PC,该方法在没有主机的情况下大量使用,技术成熟,本文不做详细描述。

从机利用备用的SCI接口,通过PC按XMODEM协议升级下载firmware成功,验证从机代码和firmware升级包都正确。

升级包描述如下:

I2C从设备地址(1byte)FWDATA(6 bytes)0x20(1 byte)Data0……Data31

每包包长度为40个bytes=从设备地址+FWDATA的ASCII码(不分大小写)+0x20+Data0+……+Data31。

方法二:通过主机,系统主机通过I2C总线接口与从

机通信,在发送命令、接收数据等都正常的情况下,主机通过网页界面、I2C总线通信对从机firmware升级,下载失败,下面做详细描述。

用示波器抓SDA波形,正确的和错误的SDA波形比较如下:

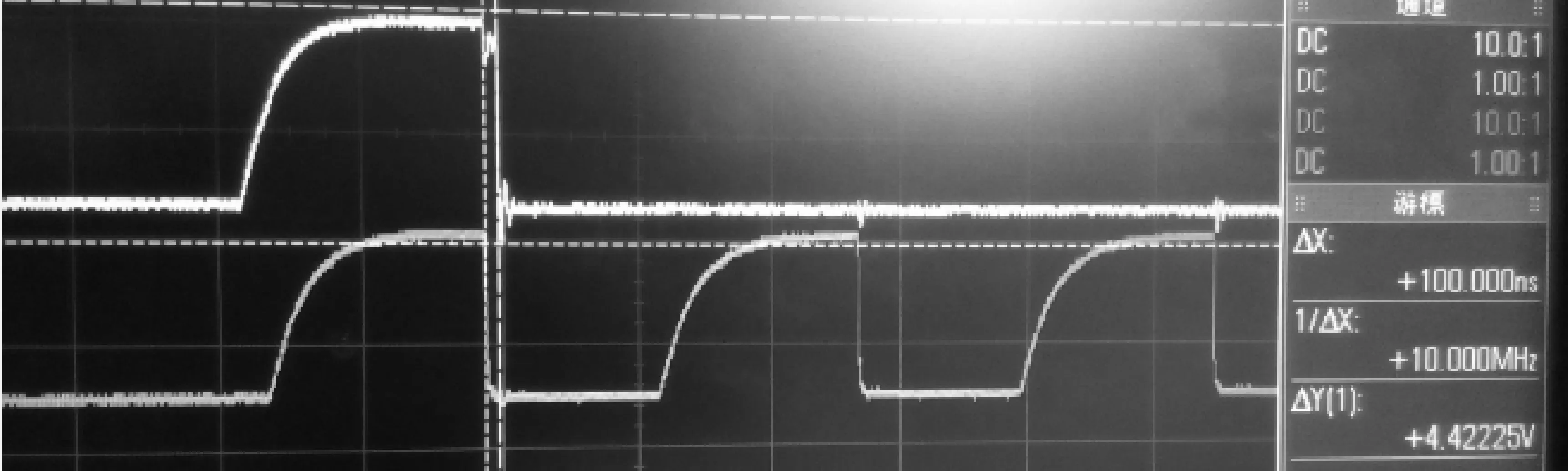

① 正常的波形是每个byte后跟ACK(即第9个SCK对应的SDA为0),正确波形如图2所示。

② 从机接收升级数据包时,前8个bytes正常,每个byte后跟一个ACK,即Data0之前的地址、命令(FWDATA)等都正常,从Data0开始到Data31,不定某个位置开始出现NACK,直到stop前一直都是NACK,错误波形如图3所示。

图2 正确波形

图3 错误波形

下面对升级失败原因进行分析:

① 对不同主、从机I2C总线升级结果及波形对比结果如下:

主机S3C2440主机XA9S12从机DSP升级OK,波形如图4-----------从机K20升级NO,波形同DSP升级OK,波形如图5

②两种升级成功的SDA波形比较及有关参数如图4、图5所示。

所采用的改进措施和改进结果比较如下:

① 改硬件上拉电阻,无效,方法如下:去掉从机I2C

总线上拉电阻(图1的R24和R25),波形无改善,升级不成功;去掉从机I2C总线上拉电阻(图1的R24和R25),并且短路图1的U4芯片,波形无改善,升级不成功。

② I2C总线 通信速度由400 kHz降为100 kHz,升级不成功。

③ 配置主机SDA延迟时间(即SDA hold时间)由5clocks改为0,升级通过,但SDA建立时间仍为80 ns,SDA hold时间由200 ns变为100 ns,波形如图6、图7所示。

图4 S3C2440&&DSP(SDA建立时间为80 ns)

图5 XA9S12&&K20(SDA建立时间为460 ns)

图6 SDA延迟5clocks(SDA hold时间为200 ns)

④ 增加SDA建立时间,修改后SDA建立时间由80 ns增加到180 ns,满足I2C总线 datasheet要求,针对上述第3条两种配置,升级都成功。

参考s3c2440A白皮书(图8)以及K20 白皮书(图9)。

图7 SDA延迟0clocks(SDA hold时间为100 ns)

图8 s3c2440A白皮书部分

图9 K20白皮书部分

主机代码做了如下修改,升级成功,I2C总线接口时序符合标准:

① 修改函数static int i2s_s3c_irq_nextbyte(struct s3c24xx_i2c *i2c, unsigned long iicstat),增加ndelay(1);//等待建立时间

② 增加ndelay(5)后,SDA建立时间为580 ns,波形如图10所示。

结 语

图10 增加ndelay(5)后波形图