用于桥式电路的多路隔离电源

2018-07-05张延迟赵博文

李 翔, 张延迟, 解 大, 赵博文

(1. 上海电机学院 电气学院, 上海 200240; 2. 上海交通大学 电子信息与电气工程学院, 上海 200240)

随着电力电子技术的快速发展,以金属氧化物半导体场效应晶体管(Metal-oxide-semiconductor Field Effect Transistor, MOSFET)和绝缘栅门极晶体管(Insulated Gate Bibolar Translator, IGBT)为主的全控型开关器件广泛用于电力场合。为保证各开关管驱动电路的稳定可靠,需要将电源做成多路隔离型。一方面隔离电源可保证每个模块单独供电,防止一个模块损坏后影响其他模块正常工作,同时相对于多个单输入电源,简化了电路结构,降低了电路成本;另一方面由于驱动信号对应各开关管的门极和源极,不同开关管之间无法共地,所以它们之间的驱动电压随源极电位的变化而对地浮动。因此,设计这种非等电位多路隔离电源具有非常重要的意义。

目前,对于多路隔离驱动电源已有许多相关研究。文献[1]中提出一种直流电流母线型多路恒流输出LED驱动电源,包括一个源变换器及多个负载变换器。文献[2]中设计了一种应用于逆变电路中驱动IGBT的隔离驱动电源方案,采用双DC-DC降压电路输出恒定直流电流,再经全桥逆变电路输出高频交变方波电流,最后通过电流变压器实现磁隔离和多路输出。文献[3-8]中研究了一种高压隔离性能的多路输出驱动电源,利用全桥串联谐振在桥臂间形成电流型交流母线,结合高压电缆线、光纤传输实现高压隔离性能,并可通过控制磁环数目改变电源输出路数。文献[9]中采用级联变压器和一次侧单匝变压器,设计了500 kV固态Marx发生器的多路隔离驱动电源,并介绍了关键工艺技术。文献[10-12]中设计了一种用于三相逆变器中IGBT的驱动电源,通过一个多绕组变压器,实现了4路相互隔离的输出,并制作了一个70 W的反激式电源用于1 200 V/600 A IGBT的驱动。文献[13-14]中设计了一种多路隔离驱动电路,包括多路隔离驱动电源、基于改进传统NE555多谐振荡器实现的脉冲宽度调制(Pulse Width Modulation, PWM)信号发生电路和基于TLP250实现的隔离电路。文献[15]中提出了一种基于高频电流互感器的多路低压直流电源设计方案。其中,主回路采用单端反激电路,将其输出的脉动大电流通过高压绝缘线穿过多个高频电流互感器的中心,从而实现多路相互隔离,同时针对不同驱动电路的要求,高频电流互感器的二次侧可通过分压电路输出不同等级的电压和电流。

1 多路隔离电源的设计

本文设计的多路隔离输出开关电源性能指标如下:输入电压DC 24 V;输出电压DC +15 V/-9 V;输出电流0.8 A;输出电压精度≤±1%;电压调整率≤±10%;负载调整率≤±5%;输出纹波系数≤±0.1%;工作环境温度为-5~45 ℃。

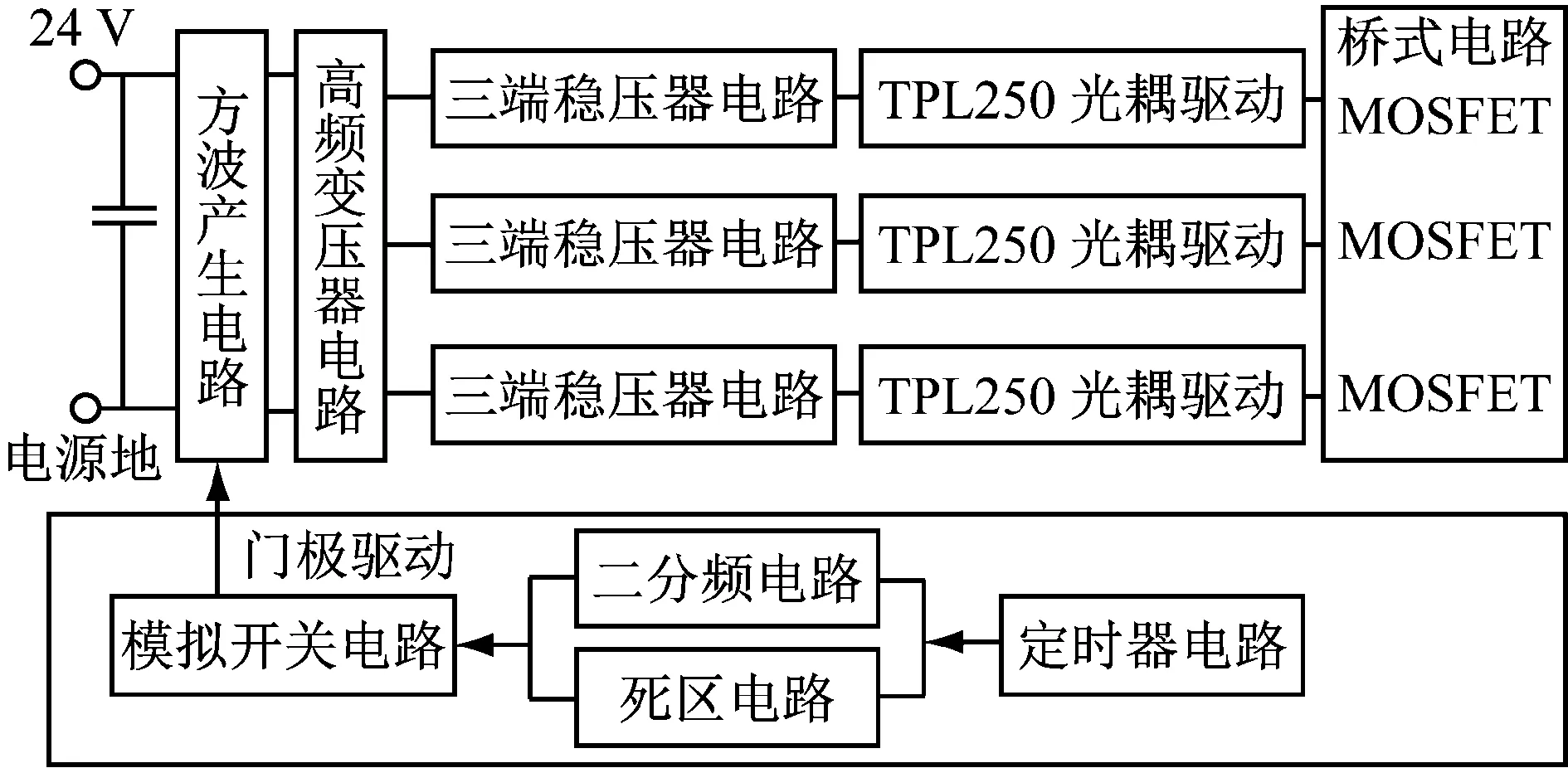

图1为多路隔离电源原理图。DC 24 V电源经电容滤波后输入到方波产生电路,产生24V的高频方波,并将此方波输入到高频变压器的一次侧一端,一次侧另一端并联隔直电容滤除直流,产生±12 V的交变电压,而变压器二次侧可采用多路绕组输出,从而实现多路隔离供电。本文采用3路输出,输出交流电经全桥整流电路后输出3路直流电压,然后分别接入三端稳压器电路,每路输出+15 V、-9 V和接地(GND),最后通过TPL250光耦驱动开关管。其中,24 V高频方波由定时器电路、二分频电路、死区电路和模拟开关电路产生。

图1 多路隔离驱动电源原理图

1.1 方波产生电路

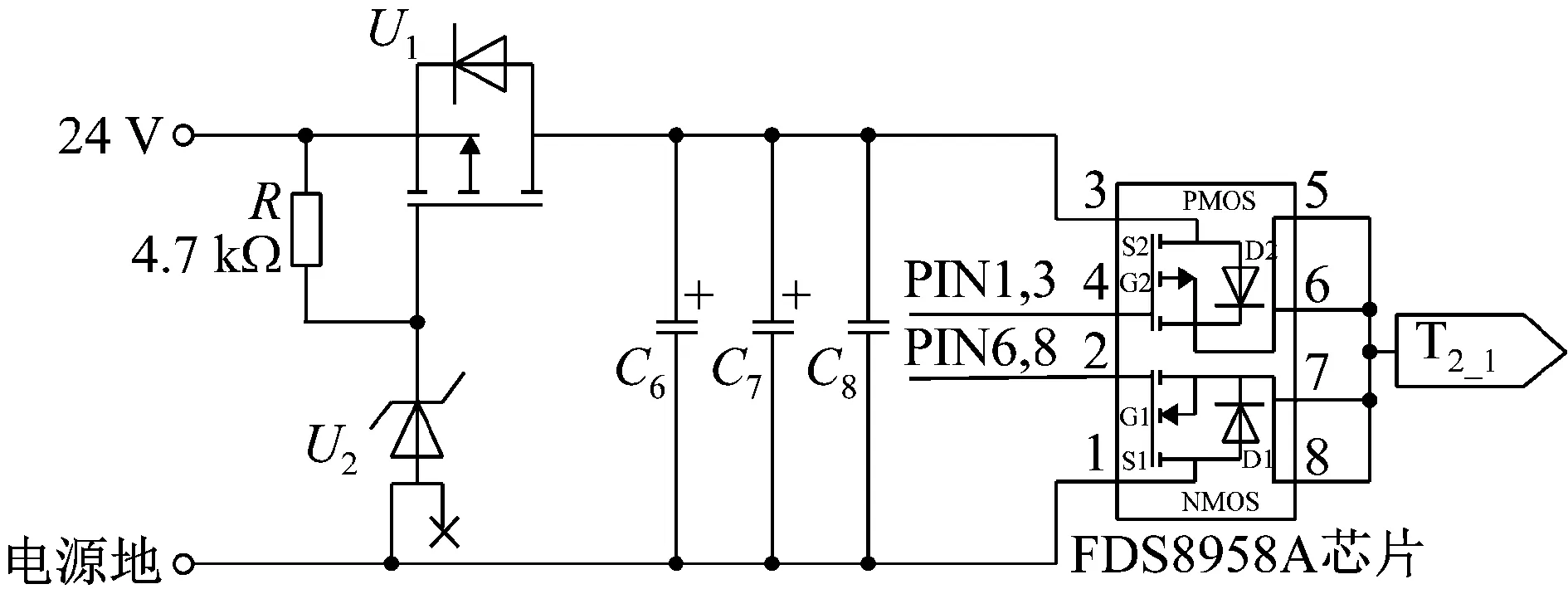

方波产生电路如图2所示。其中,U1为P型MOSFET(以下简称PMOS电压),U2为15 V稳压二极管电压。DC 24 V电源经电阻R接入到U2,保证PMOS管的正常导通。本电路中PMOS管和稳压管组成低电压保护电路,当直流供电电压偏低或在电路起动过程中,由于供电电压偏低,PMOS不导通,后级电路处于断电状态,从而起到保护后级设备的作用。两个电解电容和一个瓷片电容起电源滤波的作用。芯片FDS8958A由一对推挽MOSFET管组成,其中,引脚3电位为24 V,引脚1电位为0 V。引脚4和引脚2为栅极驱动电路产生的两路带死区方波,当引脚4为高电平时,引脚2为低电平;当引脚4为低电平时,引脚2为高电平。因此,当引脚4的电压小于引脚3电压时,PMOS管导通,N型MOSFET(以下简称NMOS)管关断,输出端T2_1输出24 V;当引脚2电压大于引脚1电压时,NMOS管导通,输出端T2_1输出0 V。

图2 方波产生电路

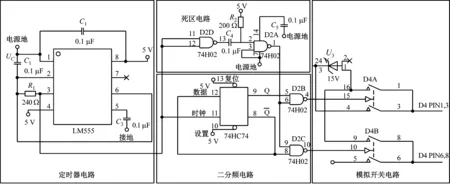

芯片FDS8958A的栅极驱动电路如图3所示。主要由定时器电路、二分频电路、死区电路、模拟开关电路组成。LM555定时器连接成振荡器电路,输入直流5 V,输出5 V高频方波;二分频电路主要通过芯片74HC74实现分频功能,输出两路电平互补的方波;死区电路由四路或非门组成,其中两路用于产生死区延迟时间,两路结合二分频电路输出方波,产生带死区的方波驱动模拟开关电路,防止两路波形同时接通或关断,造成开关管短路;模拟开关电路的输入引脚16、4、9和5分别接9V(经15V稳压管V3后获得),24 V,9 V和SGND,双刀双掷模拟开关MAX4622ESE的两个开关控制引脚15和引脚10,由74HC74和74HC02芯片产生的包含死区的推挽脉冲分配信号接入,模拟开关电路输出脚1,3和6,8分别接FDS8958A中两个MOSFET管的栅极控制引脚。

图3 FDS8958A栅极驱动电路

栅极驱动电路各部分分析如下。

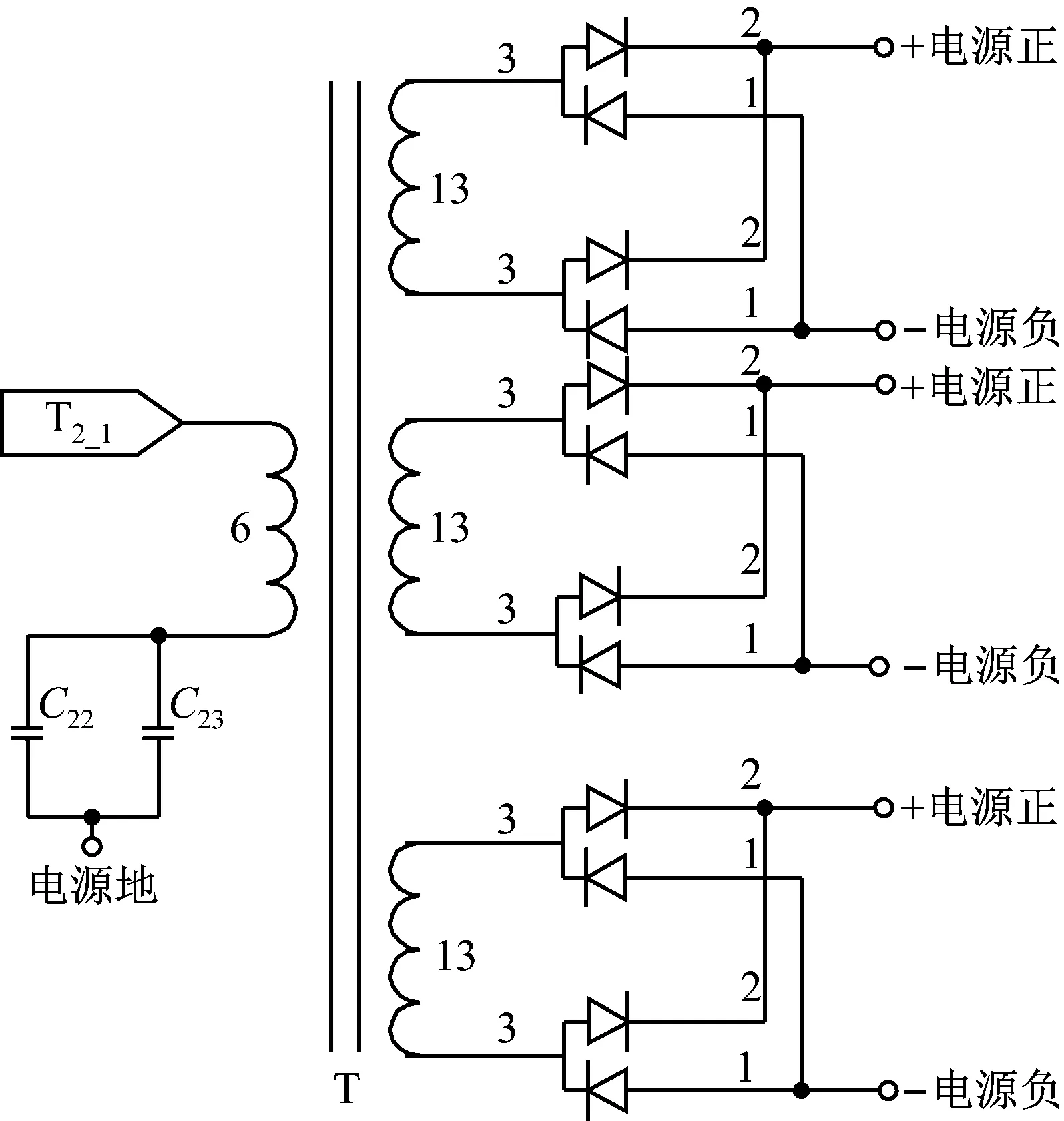

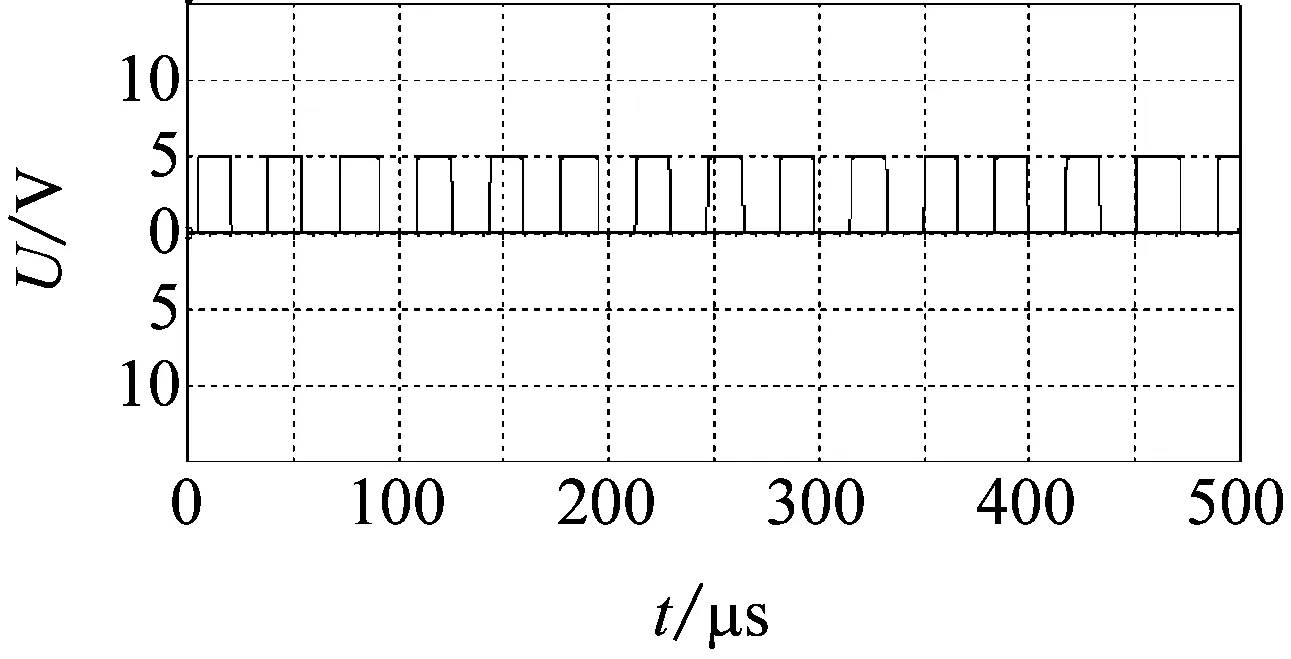

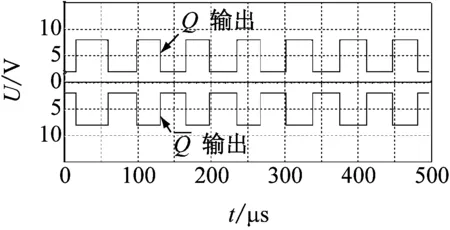

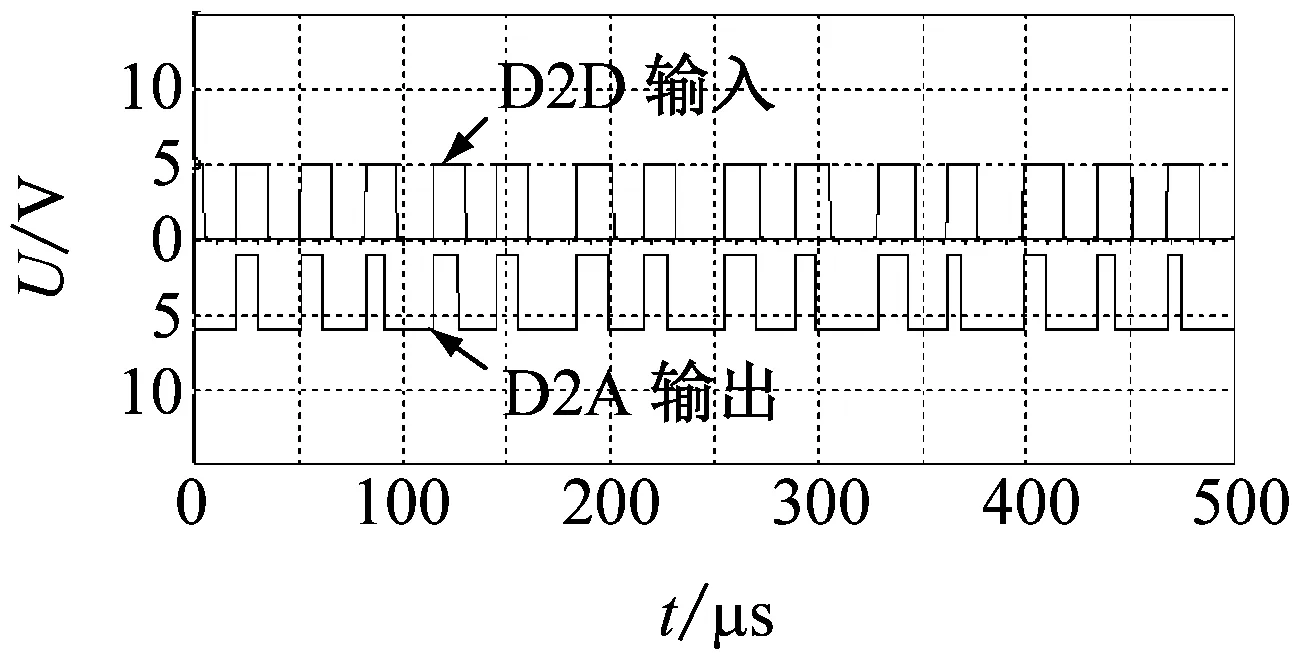

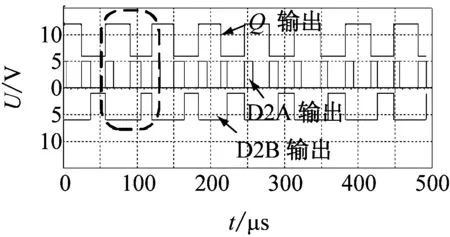

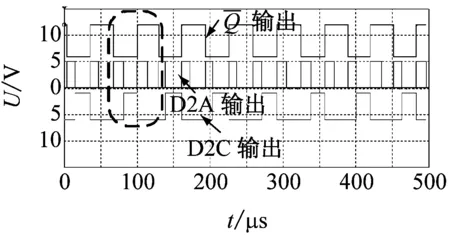

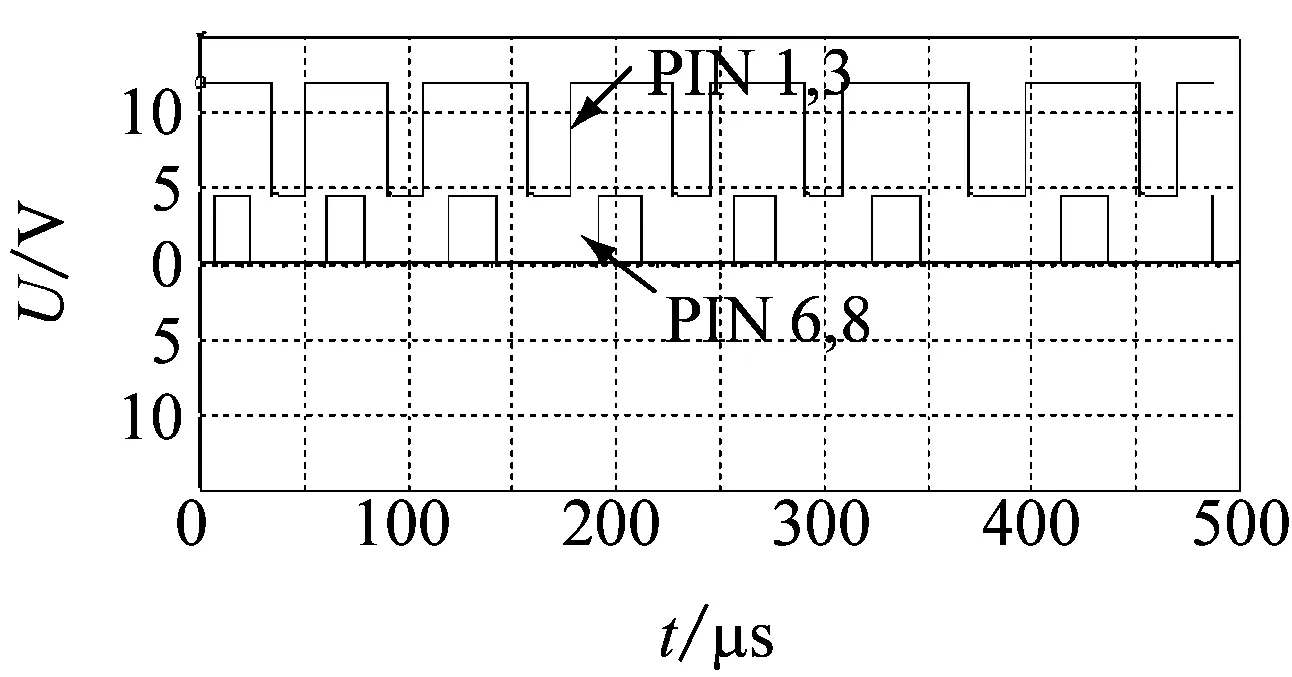

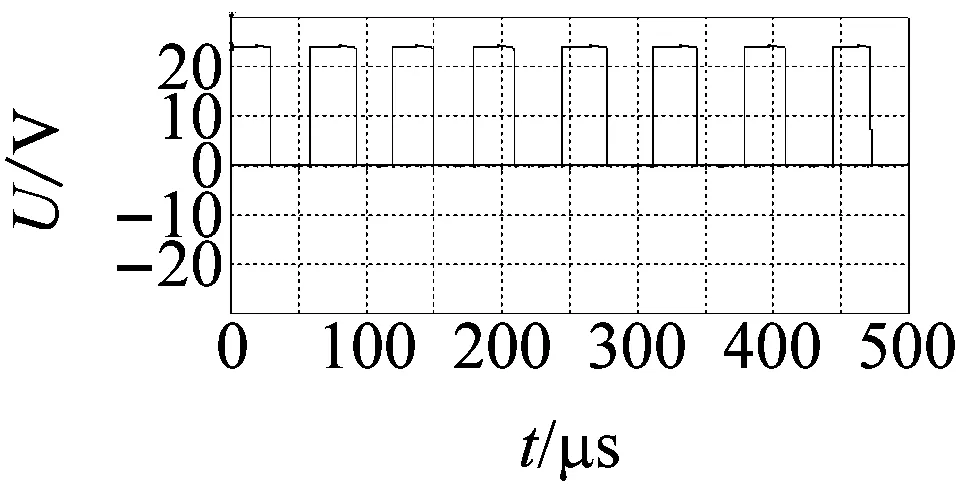

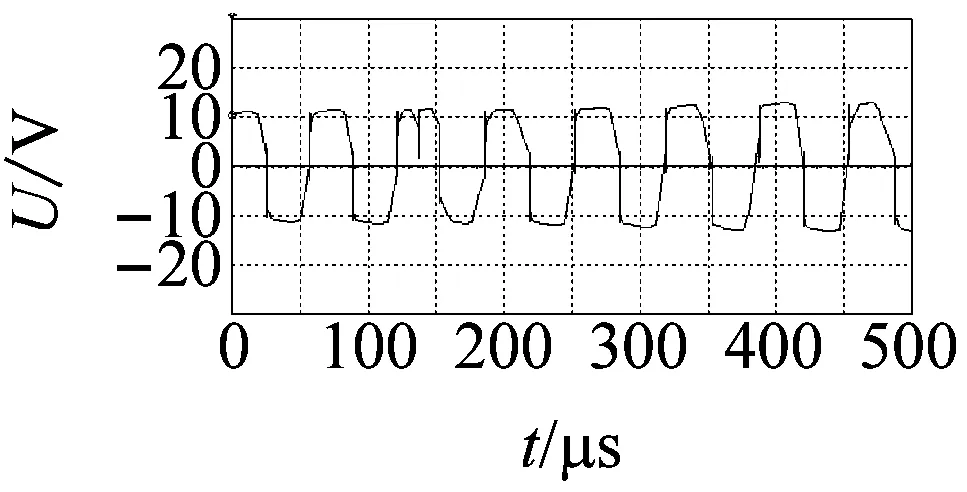

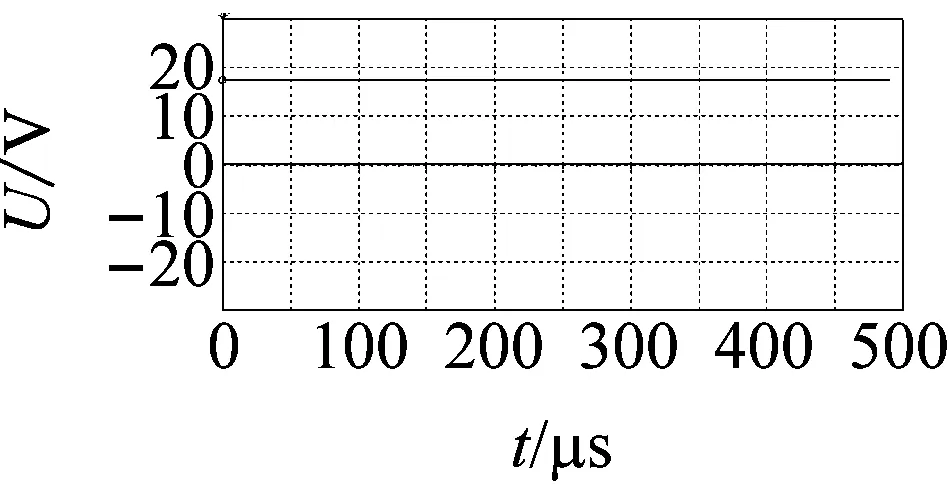

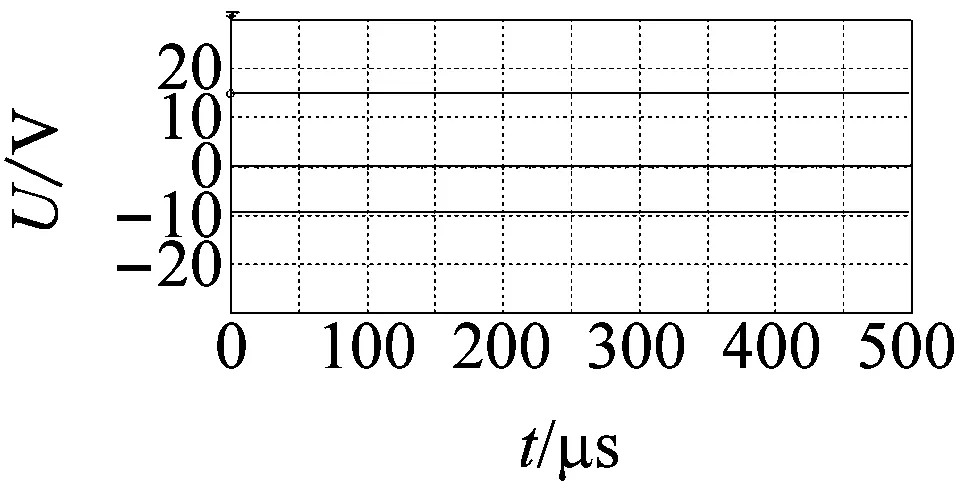

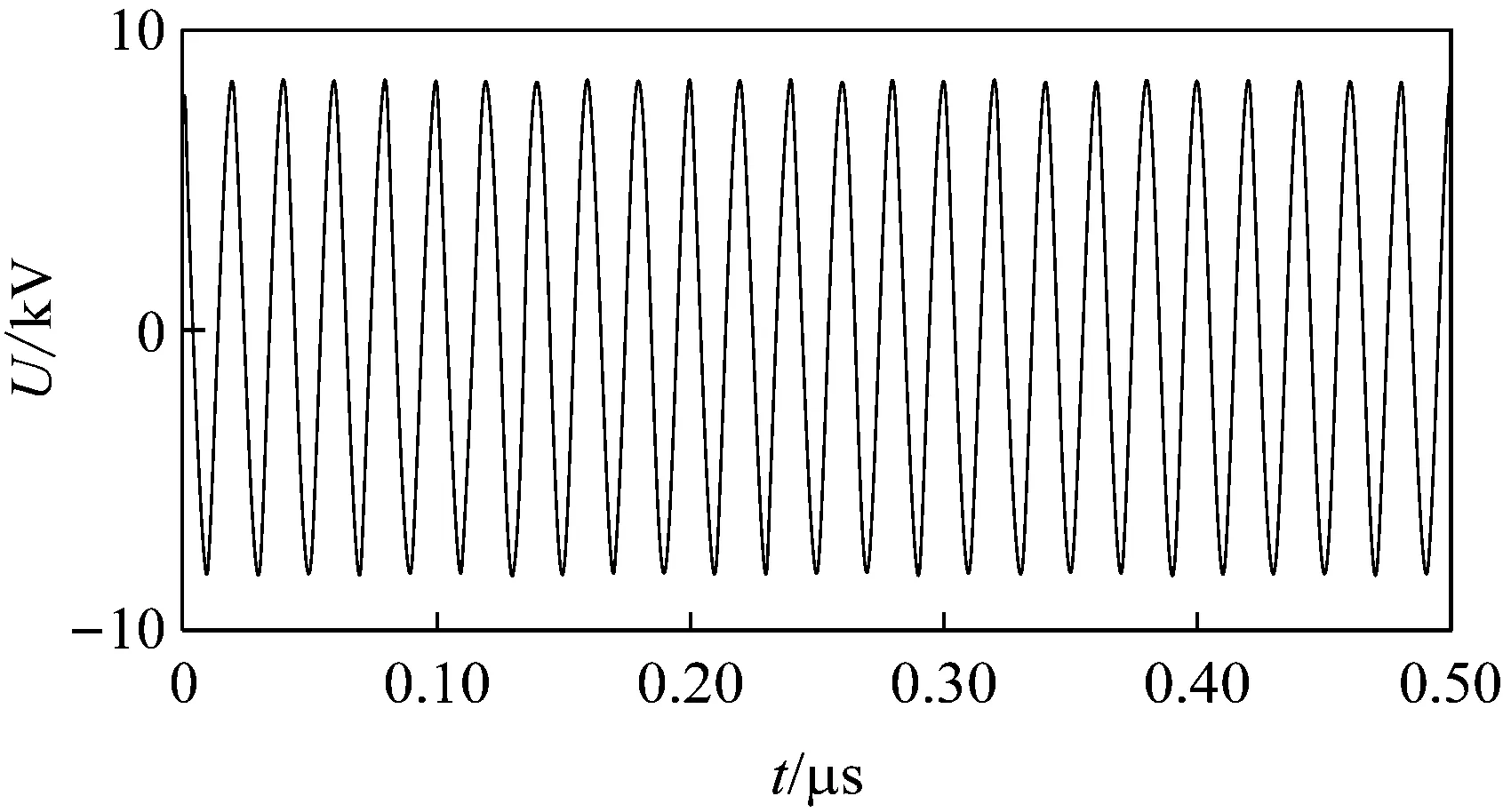

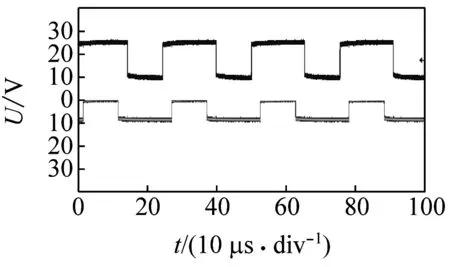

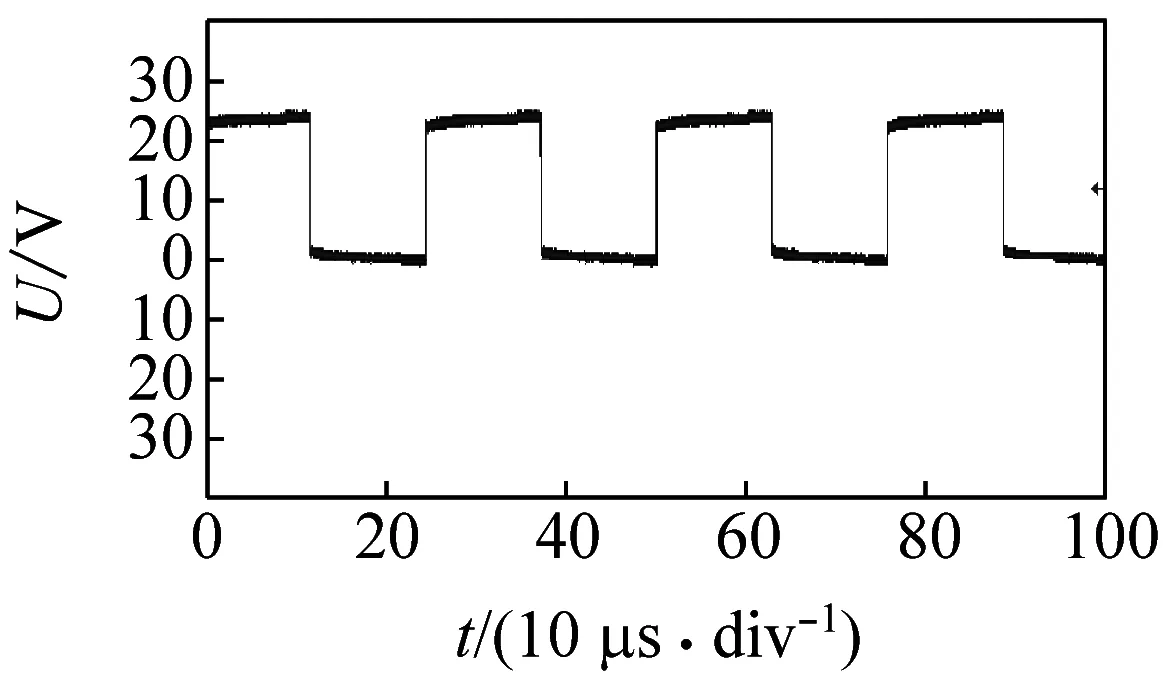

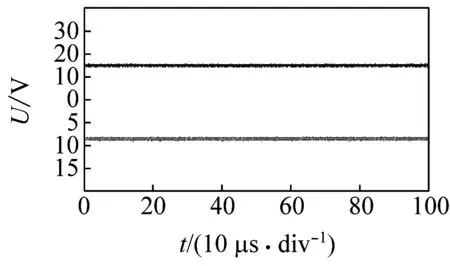

(1) 定时器电路。主要由LM555芯片组成,本文将其连接成振荡器电路。其中输入端5 V电压,可通过24 V电源经78L05稳压芯片得到。假设接通电源时,电容C1两端的电压UC=0,由于电容电压不能突变,输出端为高电平,此时输出端电压通过电阻R1向电容C1充电,使C1两端电压按指数规律上升。当UC>2U+/3时,电路输出低电平,C1经R1放电,C1两端的电压按指数规律下降,直到降为U+/3为止。当UC 由于输出矩形波的周期与电容C1的充放电时间常数和引脚2、引脚6输出的触发电压有关,故可利用一阶RC电路三要素公式,计算振荡脉冲频率。由三要素公式可得振荡电路充电和放电时间均为 (1) 式中:τ为电容C1充放电时间常数;UC(0),UC(∞),UC(T)分别为C1两端电压的初始值、终点值和充放电时间T时的值。 则其振荡频率为 (2) (2) 二分频电路。为了产生两路互补的驱动波形,本文将定时器电路输出的5 V高频方波,输入到二分频电路,产生两路互补波形且频率变为原来的1/2。二分频电路主要采用74HC74芯片实现分频功能,该芯片是双路D型上升沿触发器,带独立的数据输入、时钟输入、设置和复位输入,以及互补的Q和Q非输出。设置和复位引脚输入为高电平,5 V方波输入74HC74芯片的时钟引脚。当时钟处于上升沿时,若数据引脚为高电平,则Q端输出为高电平,Q非端为低电平;若数据引脚为低电平,则Q端输出为低电平,Q非端为高电平。 (3) 死区电路。为防止两个开关管同时导通,本文设计了死区电路。死区延时主要通过芯片74H02完成。该芯片由4个或非门组成。其中,D2A、D2D两个或非门和R2C4微分电路作用于死区电路,完成死区电路延时功能,D2D起缓冲作用,D2A电路中输入脚的电阻R2和电容C4形成RC微分电路,确定开关状态变化时的死区时间,死区延迟时间τ=R2C4。74H02芯片的另外两个或非门D2B、D2C的输入端分别接二分频电路和死区电路的输出,输出端产生带死区的方波,驱动模拟开关。 (4) 模拟开关电路。模拟开关电路由MAX4622ESE芯片组成。当控制输入脚15为低电平、引脚10为高电平时,引脚4和引脚9对应的开关导通,PIN1,3和PIN6,8输出电压分别为24 V和9 V,FDS8958A芯片的NMOS管导通、PMOS管关断,T2_1输出0 V;当控制输入脚15为高电平、引脚10为低电平时,引脚6和引脚5对应的开关导通,PIN1,3和PIN6,8输出电压分别为9 V和0 V,FDS8958A芯片的PMOS管导通、NMOS管关断,T2_1输出24 V。通过这些复杂的驱动电路使两个MOS管的推挽控制电路获得可靠的死区和良好的驱动、关断效果,减小开关损耗及发热,最终在输出端获得24 V的高频方波信号。 变压器部分采用磁环变压器,磁环变压器由一路输入多路输出,实现相互多路隔离,然后将输出的交流电压经全桥整流电路后输出直流电压。 磁环变压器电路如图4所示。变压器一次侧采用6绕组输入,二次侧采用三路13绕组输出。其中,一次侧T2_1端输入24 V方波,另一端接并联电容滤除直流电压,使输入端变为±12 V的交流电,变压器的二次侧输出±24 V的交流电,实现一路12 V输入,三路24 V输出。然后将磁环变压器输出电压接入全桥整流电路,全桥整流电路由两个BAV99芯片组成,输出DC 34 V,最后将输出电压接入三端稳压器电路。 图4 磁环变压器电路 图5所示为以LM7809稳压芯片为核心三端稳压器电路。电路输入端由整流电路接入,正负极分别为+24 V和-9 V,经过稳压芯片LM7809和电容分压后,输出+15 V,-9 V和接地,然后接入TPL250光耦。其中+15 V和-9 V为光耦供电,接地端连接于MOSFET源极,保证各开关管可靠关断。 图5 三端稳压器电路 Multisim是加拿大Interactive Image Technologies公司(简称IIT公司)在EWB5.0(Electronics Workbench)的基础上推出的一款专门用于电子电路设计与仿真的软件。本文利用Multisim软件搭建了多路隔离电源仿真电路模型。方波产生电路中FDS8958A芯片的门极驱动电路仿真波形如图6所示。 图6(a)为定时器电路输出波形,5 V电源经定时器电路后,输出幅值为5 V,频率为30 kHz,占空比为0.5,决定整个驱动电源的频率。由式(2)知,通过调节电阻R1和电容C1的值,可改变电源频率。图6(b)为二分频电路Q和Q非输出波形,将定时器电路输出的5 V方波变为两路幅值相同、频率变为原来一半的互补波形,分别驱动模拟开关。图6(c)为死区电路输入输出波形对比。定时器电路输出方波经D2D,D2A两级缓冲后,产生死区延时。当死区电路输入为高电平时,经D2D后输出低电平,此时5 V电源经电阻R2向电容C4充电,D2A输入低电平输出高电平,经过一定时间延迟后,电容C4充电完成,D2A输入高电平输出低电平;当输入为低电平时,经D2D后输出高电平,D2A输入高电平输出低电平,直到下一周期再次出现高电平,如此循环往复,产生延时方波。另外可通过改变R2,C4的值,可调节死区时间;图6(d)为二分频电路输出端Q,D2A输出端和D2B输出端波形对比。由于Q端输出波形周期变为原来2倍,所以当Q输出1个周期时,死区电路输出2个周期,且只有死区电路和二分频电路同时输出低电平时,驱动波形输出为高电平,因此输出波形中高电平占空比为0.25;图6(e)为二分频电路输出端Q非、D2A输出端和D2C输出端波形对比,其结果与图6(d)图类似。D2B和D2C两路输出为模拟开关电路输入端驱动波形,由图6(d)和图6(e)分析可知,两路驱动波形中高电平分别位于二分频电路输出波形的后半周和前半周,由此产生死区保护作用。图6(f)为模拟开关电路输出波形,由于输入端驱动波形中高电平占空比为0.25,因此输出的9~24 V方波中低电平9 V占空比为0.25,而0~9 V方波中高电平9 V占空比为0.25,分别作用于FDS8958A的控制输入端。 (a) 定时器输出波形 (b) 二分频电路Q和Q非输出波形 (c) 死区电路输入输出波形对比 (d) 二分频电路输出端Q、D2A输出端和D2B输出端波形对比 (e) 二分频电路输出端Q非、D2A输出端和D2C输出端波形对比 (f) 模拟开关电路输出波形 图6方波电路驱动波形 模拟开关电路输出两路方波分别驱动FDS8958A的栅极后,方波产生电路输出24 V方波,并接入磁环变压器的一次侧T2-1,变压器一次侧另一端接并联电容滤去直流,使输入端变为±12 V的交流电,磁环变压器的二次侧输出经整流电路后,输出DC 34 V,34 V电压经三端稳压电路后输出+15 V,-9 V和GND,仿真波形如图7所示。图7(a)为方波产生电路输出的24 V方波,由于只有当FDS8958A的PIN1,3输入为9 V时,PMOS管导通,电路输出24 V,而PIN6,8输入9 V时,NMOS管导通,电路输出0 V,因此方波产生电路占空比为0.5。图7(b)为磁环变压器输入交流波形。24 V方波经过并联电容滤去直流后输出±12 V的交流电压,作为磁环变压器的交流输入。图7(c)为磁环变压器二次侧交流方波,经整流电路输出的DC 34 V。图7(d)为整流电路输出端经三端稳压器电路后输出的+15 V和-9 V波形。 (a) 方波产生电路输出的24 V方波 (b)磁环变压器输入的交流波形 (c)磁环变压器二次侧交流方波经整流电路输出的DC 34V (d) 整流电路输出端经三端稳压器电路后输出的+15 V和-9 V波形 图7磁环变压器及稳压电路波形 三端稳压器电路输出+15 V和-9 V 为TPL250光耦独立供电,最后由光耦驱动MOSFET,实现开关管可靠关断。如图8所示为三路隔离电源为光耦供电作用于桥式电路各MOSFET后,输出的正弦波形,可通过调节光耦触发端使电路输出不同波形。 图8 桥式电路输出波形 为验证本设计方案的可行性,本文制作了一台样机,并测试了电路各部分输出波形。电源实物图如图9所示。 图9(a)为24 V方波产生电路;图9(b)为高频变压器电路和三端稳压器电路。24 V电源接入后,经稳压管和PMOS后,接入FDS8958A芯片。驱动电路中LM555芯片的供电由24 V电源经过78L05稳压芯片后输入5 V,输出的5 V方波经74HC74芯片、74H02芯片和MAX4622ESE驱动FDS8958A芯片,输出24 V方波,然后接入磁环变压器的输入端,磁环输出3路分别接入由两个BA V99芯片组成的整流电路,最后接入三端稳压器电路并通过光耦驱动开关管。本文采用1路驱动电压,同时驱动3个FDS8958A芯片,然后输入到3个磁环变压器。由此可见,该电源结构简单、体积较小、价格便宜并且损耗较少。 通过对多路隔离电源的各部分进行测试,得出如图10所示的试验波形。图10(a)为定时器电路输出幅值为5 V,频率为30 kHz,占空比为0.5的5 V方波。图10(b)为二分频电路输出幅值5 V,频率变为原来一半的两路互补试验波形;图10(c)为模拟开关电路输入端带死区的两路驱动试验波形,高电平约占0.25。图10(d)为模拟开关电路输出的9~24 V和0~9 V方波,两方波中9 V电平约占0.25。图10(e)为方波产生电路输出的24 V方波试验波形。图10(f)为经磁环变压器和整流电路后,三端稳压电路输出的+15 V,-9 V试验波形。从试验波形可以看出,试验波形与理论分析和仿真结果基本吻合。 (a) 24 V方波产生电路(b) 变压器和稳压电路 图9电源实物图 (a) 定时器电路输出波形 (b) 二分频电路输出波形 (c) 模拟开关电路输入端驱动试验形波 (d) 模拟开关电路输出波形 (e) 24 V方波试验波形 (f) 三端稳压电路输出波形 图10试验波形 设计了一种多路隔离电源,主要用于解决非等电位电路中多个开关管之间不共地问题。电路主要包括方波产生电路及其内部栅极驱动电路、高频变压器电路和三端稳压器电路。从理论分析、Multisim软件仿真和实物试验三个方面详细分析了各电路输出波形,验证本设计方案的正确性,然后通过试验测得电源输入、输出功率,并求出电源效率,最后从芯片FDS8958A的推挽MOS管的开通、关断损耗和磁环变压器的磁滞损耗两方面分析了电源损耗。本设计方案结构简单、体积较小、稳定性高、成本较低、电源效率较高,完全能够满足非等电位电路中多路隔离电源的需求。 [1] 罗全明,黄健,马坤,等.一种直流电流母线型多路恒流输出LED驱动电源[J].中国电机工程学报,2016,36(22):6201-6209. [2] FEI W M, LU Z Y, XIA L H, et al. High insulation multiple output switch power supply used for driving of IGBTs in medium-high voltage inverter[C]∥Applied Power Electronics Conference and Exposition, Miami, USA, 2003: 1066-1092. [3] 方春恩,王猛,李伟,等.混合式直流断路器的多路隔离驱动电源设计[J].高电压技术,2016,42(6):1746-1753. [4] 陈哲,肖岚.多路输出高压隔离驱动电源的研究[J].电力电子技术,2012,46(1):19-24. [5] 苏斌,吕征宇.新型中高压隔离驱动电源的架构[J].电工技术学报,2010,25(2):121-126. [6] 苏斌,吕征宇. 新型电流型固态短路限流器驱动电源[J]. 中国电机工程学报,2009,29(27):48-53. [7] 金高先,吕征宇.多路输出隔离驱动电路及其在短路限流器中的应用[J]. 电源技术应用, 2003,6(12):61-64. [8] 宋佩云,肖岚.电流母线型多输出高压隔离驱动电源[J]. 电力电子技术,2015,49(1):29-32. [9] 王凌云,王传伟,李洪涛,等.500KV固态Marx发生器IGBT多路驱动高压隔离供电电源设计[J].高电压技术,2012,38(1):236-240. [10] CHANG Liuchen.Development of a driver board power supply for high power IGBTs used in three-phase inverters[J].IEEE Aerospace and Electronic Systems Magazine,1996,11(8):24-28. [11] FUJITA H. A resonant gate-drive circuit with optically isolated control signal and power supply for fast-switching and high-voltage power semiconductor devices [J]. IEEE Transactions on Power Electronics, 2013, 28(11):5423-5430. [12] WANG J, CHUNG S H, LI T H. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance [J]. IEEE Transactions on Power Electronics, 2013, 28(1):573-590. [13] 陈珊珊. 一种多路隔离驱动电路的设计与实现[J]. 西南师范大学学报(自然科学版), 2015, 40(8):86-91. [14] 李艳. 多输入直流变换器电路拓扑及控制策略研究[D]. 南京:南京航空航天大学, 2009. [15] 赵秋山,冯冬青,卢宜.高压隔离的多路低压直流电源[J].电力自动化设备,2010,30(1):136-138.1.2 高频变压器电路

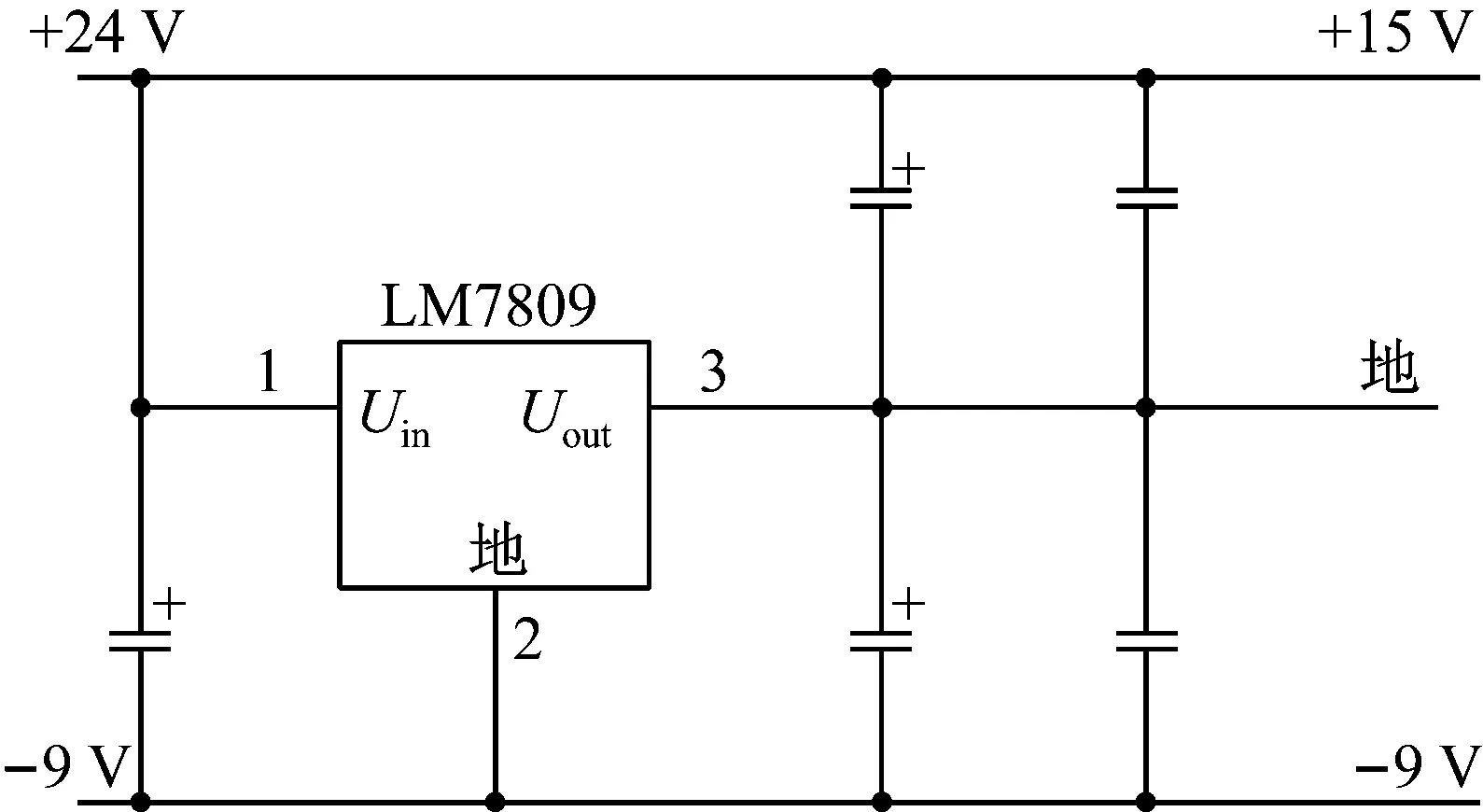

1.3 三端稳压器电路

2 多路隔离电源仿真分析

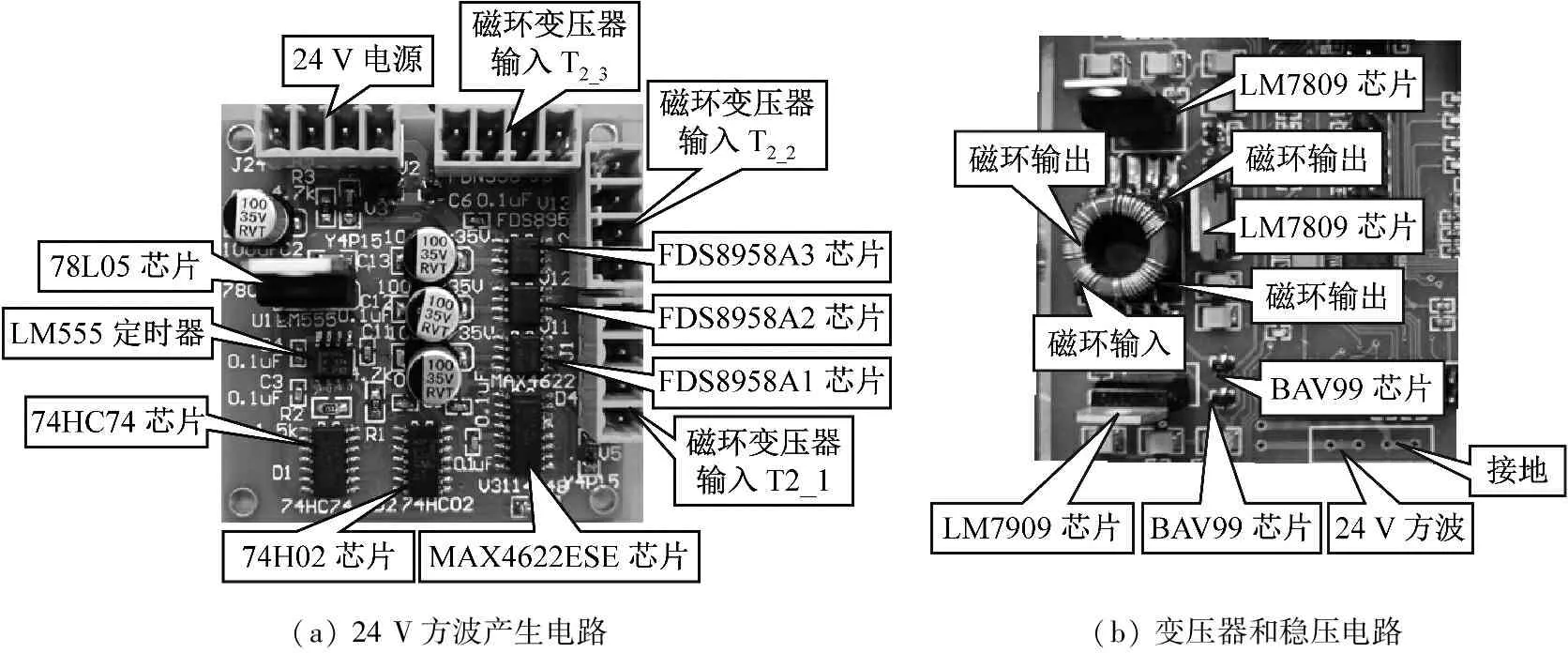

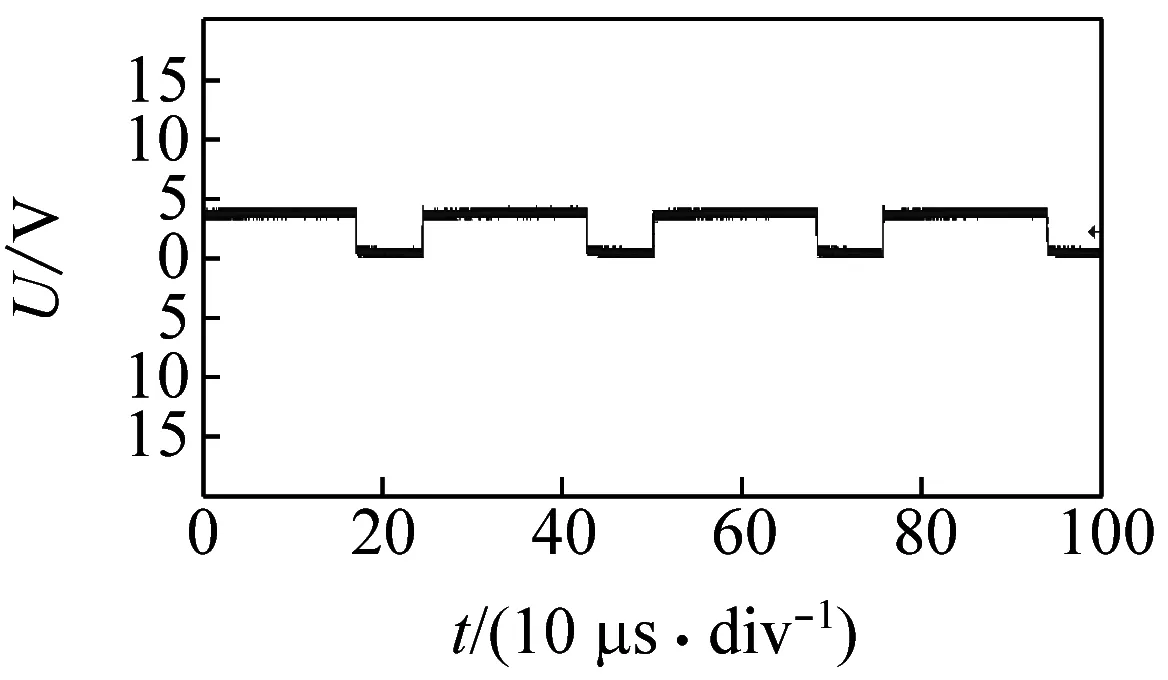

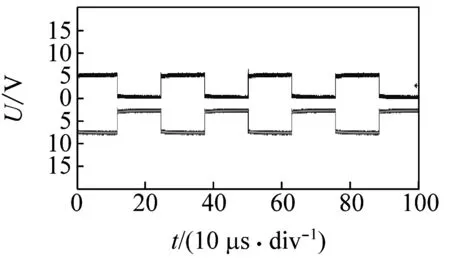

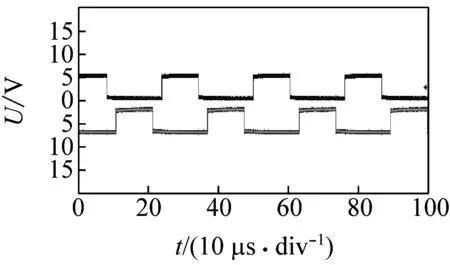

3 多路隔离电源试验分析

4 结 语