FPGA多模式高效脉冲压缩工程应用

2018-07-03张振华

李 翱, 于 勇, 褚 超, 张振华

(北京遥测技术研究所,北京 100076)

0 引 言

现代雷达系统基于其多样化的功能需求,往往根据不同的应用场景,需要不同的参数设置,发射信号的脉宽与带宽均存在差异,最终成像的场景范围与分辨率亦有所不同。而作为目前大多数成像系统的基础,脉冲压缩模块对于多工作模式的适应性与可移植性就变得尤为重要。

在传统的雷达成像机制中,脉冲压缩技术已经能够在DSP上得到成熟地运用,但随着雷达信号处理机处理要求的提高,通过DSP进行脉冲压缩在处理实时性上的局限性逐渐显现出来。近年来随着可编程门阵列(Field programmable gate array,FPGA)器件的快速发展以及雷达成像处理平台小型化的趋势,各科研单位开始采用FPGA逐步替代DSP实现脉冲压缩功能,并在工程应用上开始普及;但在实践过程中仍然存在着资源消耗量与信号处理实时性,设计可靠性与应用灵活度等一系列需要权衡的问题。多模式高效脉冲压缩的难点主要在于保持较高信号处理实时性,同时仍能够灵活地适应各种工作场景的转换需求;并且需要综合考虑FPGA的使用效率,尽可能以较少的资源消耗来达到工程应用目的。

本文将对FPGA多模式高效脉冲压缩的设计方案与工程应用效果进行阐述。

1 脉冲压缩基本原理

脉冲压缩技术是雷达信号处理的关键技术之一。其在接收时采用相应的匹配滤波方法以获得较窄的脉冲信号,在获取雷达回波信息的同时,能够较好地解决距离分辨率与雷达脉冲峰值功率受限之间的矛盾[1-2]。

基于线性调频信号的脉冲压缩可以通过匹配滤波处理来实现,而匹配滤波的实现有时域卷积和频域相乘两种方法。由参考文献[3]可知,理想条件下时域和频域上匹配滤波输出y(t)和Y(ω)可分别简化为

(1)

式中:s(t)为时域输入信号,S(ω)为s(t)对应的频域信号,S*(ω)为S(ω)的共轭信号,⊗为卷积运算符。由式(1)可知,时域上匹配滤波输出为输入信号与其镜像函数的卷积,频域上则为输入信号频谱与其复共轭值的乘积。

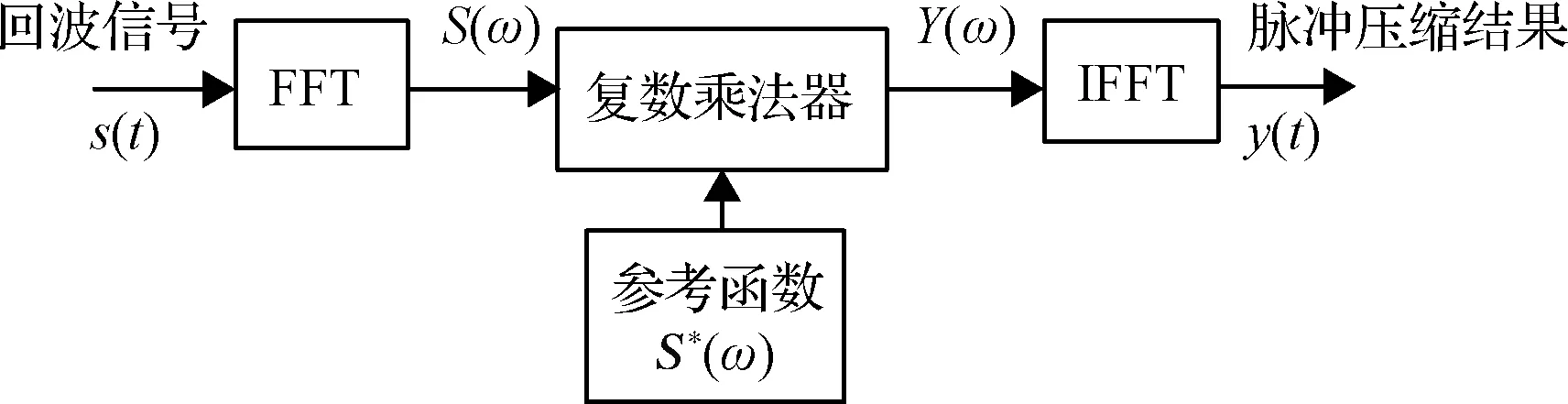

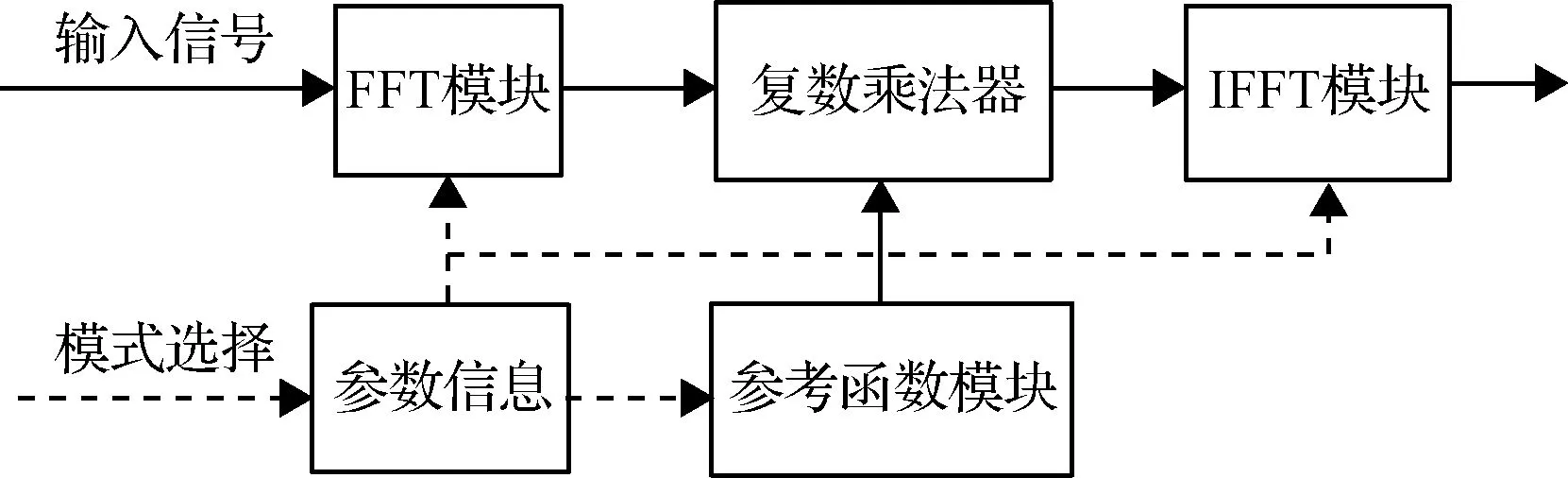

相较于时域上较为繁琐的卷积运算处理,频域脉冲压缩法仅需进行复数相乘运算,大大减少了运算量,降低了设计复杂度和资源开销,便于硬件实现。因此,在工程实践中,频域脉冲压缩法有更广阔的应用空间,其原理如图1所示。

图1 频域脉冲压缩原理图Fig.1 The schematic diagram of frequency-domain pulse compression

2 多模式高效脉冲压缩IP核的设计

1)FFT、IFFT模块

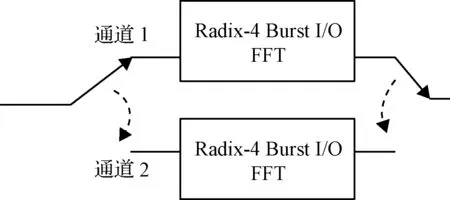

FFT运算作为实现频域脉冲压缩的关键环节,其运算效果会对脉冲压缩的信号质量产生直接影响。为在保持FFT模块灵活性的同时较好地节约资源,提高使用效率,本文采用图2所示的基于乒乓工作机制的复式FFT结构[4]以替代工程中普遍使用的Streaming I/O结构,在保证信号实时处理能力的同时优化了资源分配。

图2 复式FFT结构Fig.2 Compound FFT architecture

对于FFT与IFFT模块,多工作模式下对其最大的影响因素是运算点数的改变,而雷达信号带宽、脉冲宽度、采样率等参数的改变并不会影响该模块的工作方式。若各工作模式下FFT的运算点数相同,则FFT模块的工作状态可以固化通用。但雷达工作场景的变换往往伴随着处理数据量的变化,从而导致FFT运算点数的更改。

本文复式FFT结构中采用的基-4 FFT运算结构均采用Xilinx FPGA中提供的FFT IP核实现[5]。该IP核中设置有专门的配置寄存器对IP核的相关工作状态做出调整,其中对NFFT寄存器进行更改,可以实现FFT运算点数的实时变更。因此可以根据雷达工作模式的变更状态对NFFT寄存器进行实时配置,以实现FFT模块对多个工作模式的实时响应。

2)参考函数模块

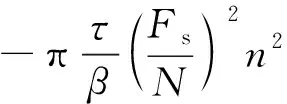

在采用基于匹配滤波的频域法实现线性调频信号的脉冲压缩处理时,其参考函数一般设置为匹配滤波器的频域冲激响应。为方便在数字信号处理器件上实时生成参考函数,可以根据驻定相位原理和近似量化处理得到参考函数的量化表达式[4,6]:

S(n)=

(2)

式中:n为整数,β为信号带宽,τ为信号脉冲宽度,Fs为信号的采样率,N为脉冲压缩处理点数。

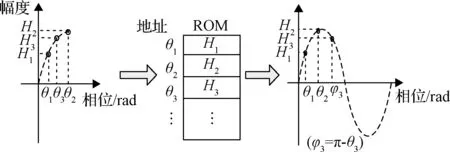

在雷达系统工作模式趋于多样化,其发射信号特征趋于复杂化的应用背景下,采用以相位作为地址,对函数幅值表进行实时动态提取的查表法来生成参考函数比cordic算法等现有方法更有优势[4];且相较于将完整参考函数直接固化存入ROM的方法[7-9]和借助外部接口对参考函数进行实时更新等方式[10],实时查表法在硬件实现上也更为灵活高效、简洁可靠。

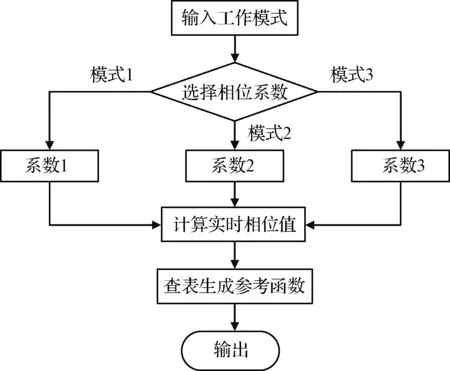

图3 查表法原理图Fig.3 The schematic diagram of LUT method

图4 参考函数生成流程图Fig.4 The flow diagram of generating reference function

3)复数乘法器

在工作模式变换过程中,为方便数据处理,各模式的数据位宽往往是统一固定的。因此在多模式工作环境下复数乘法器的设置往往可以保持不变以实现共用。由此可得出多模式脉冲压缩模块处理结构如图5所示。从图5可以看出,多模式脉冲压缩模块共有两组数据流,一组是雷达回波信号,用于进行脉冲压缩处理,在图中用实线表示;另一组是工作模式及相关参数,用于对各处理模块的工作状态进行配置,在图中用虚线表示。基于此处理机制,对其进行IP核封装。

图5 多模式脉冲压缩模块结构图Fig.5 Diagram of pulse compression module with multiple working modes

Vivado软件平台为用户自主进行IP核的设计与封装提供了平台与工具,设计者可以根据自己的需求将具有特定功能的FPGA代码模块进行封装处理,如此既能使源代码得到保护,又能让模块移植变得更加简便高效。

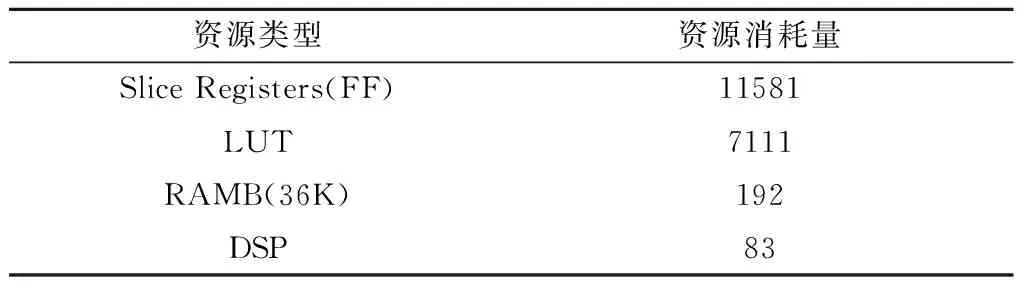

本节以Vivado软件为处理平台,根据参考文献[11]中相关处理步骤,对多模式脉冲压缩模块进行封装得到IP核。该IP核总共可设置9种工作模式,以满足系统多工作模式需求,并对脉冲压缩处理点数和相位系数进行了参数化设计;设计者可以根据不同工作环境的需要,对每种模式的脉冲压缩点数和相位参数进行单独修改,以满足不同成像场景的需求,这体现了其在不同平台间复用与移植的可行性与使用的灵活性。此外,可以根据实际应用情况对该IP核进行版本升级,扩充工作模式配置数量,以满足更多的应用需求。基于Vivado软件平台的多模式脉冲压缩IP核资源消耗情况如表1所示。

表1 多模式脉冲压缩IP核资源消耗统计Table 1 The resource utilization summary of pulse compression IP core with multiple working modes

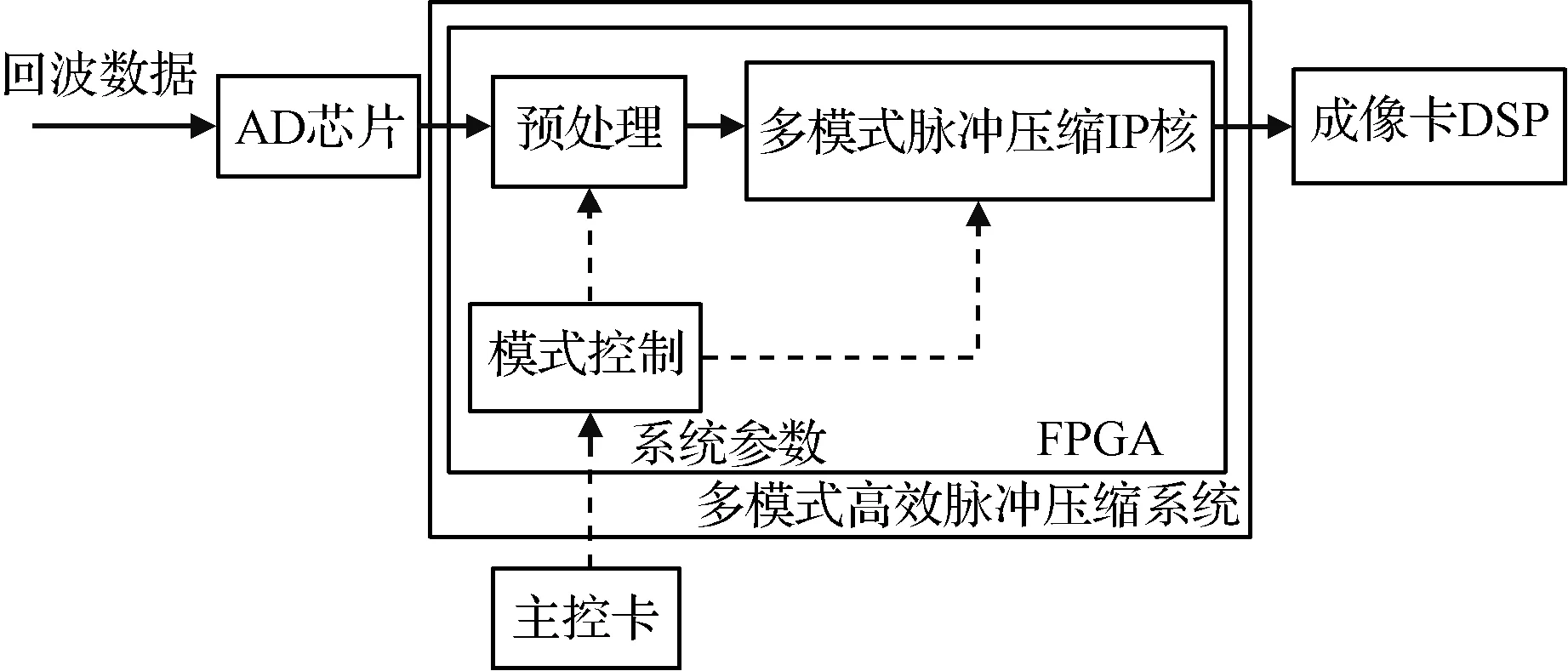

3 多模式高效脉冲压缩功能的硬件验证

为了更加贴近实际应用,本文在多模式脉冲压缩IP核的基础上加入预处理、AD采集等模块构建了一个多模式脉冲压缩小型系统用于功能测试,其结构如图6所示。平台上配有一块AD采集芯片用于回波信号的采集与传输;一块Xilinx Virtex-7 FPGA芯片用于包括数字下变频和数字滤波抽取在内的信号预处理以及多模式脉冲压缩功能的实现,其脉冲压缩结果通过FPGA传输至成像卡DSP进行后续成像处理。其间,主控卡通过板间接口将当前工作模式及关键系统参数传输至FPGA模式控制模块中,模式控制模块根据相关参数对预处理和脉冲压缩模块进行配置从而实现系统在各工作模式之间的转换。

基于以上平台,本文对5种工作模式进行了测试,各模式发射信号带宽范围包含78 MHz至800 MHz,脉冲压缩处理点数包含8192点至32768点,测试信号的输入重频为3 kHz。各模式脉冲压缩测试结果如图7所示。图下标注N表示脉冲压缩处理点数,B表示信号带宽。各图横坐标为处理样本点数,纵坐标为信号归一化幅值,单位dB。

图6 多模式脉冲压缩系统结构图Fig.6 Diagram of pulse compression system with multiple working modes

从各模式测试结果可以得出,该脉冲压缩系统具备在3 kHz处理重频条件下,对多工作模式,多脉冲压缩处理点数,不同带宽的信号进行脉冲压缩实时处理的能力。各模式脉冲压缩结果底噪均低于-60 dB,符合实际工程应用需求。

随着FPGA芯片工艺的迅速发展,其高效并行的处理机制、丰富的逻辑与运算资源令FPGA在数字信号处理领域发挥越来越重要的作用;而FPGA使用灵活、可反复烧写、容量大、速度快等优势也使得其在卫星和空间设备上有很高的应用价值,在航天领域有广泛的应用前景[12-13]。基于FPGA脉冲压缩的雷达成像技术也逐步从机载、弹载平台向星载平台发展,可应用于对地监测、资源普查、目标搜索等。

图8 雷达成像结果Fig.8 Radar image

图8为某航天项目飞行试验中对地场景成像结果。该试验在距离向处理中采用了基于FPGA多模式高效脉冲压缩技术,充分利用了FFT IP核与基于查表法的实时参考函数,能够适应不同成像场景下的大点数脉冲压缩处理,提高了雷达成像处理实时性。该场景下成像分辨率为1 m,从图中可以清晰观测到地面场景(农田、湖泊、公路等)。

4 结 论

本文通过研究雷达信号脉冲压缩原理,针对现代雷达系统功能需求多样化、信号处理数据量大的特点,提出一种基于FPGA处理平台的多模式高效脉冲压缩方式。本文采用了复式FFT结构,既满足工程应用对于信号处理实时性的要求,又减少了资源消耗,并充分利用FFT IP核可配置的特点对多工作模式进行响应;采用查表法生成参考函数,并通过对各工作模式下相位系数进行参数化处理,既保证了多模式工作背景下,信号处理的实时性,又保持了参数修改的灵活性;对脉冲压缩模块进行了可配置的IP核封装处理,使其既能适应多工作模式实用需求,又能够便利地进行移植和复用。经试验验证,本文研究成果在采用脉冲压缩信号体制的小型化、低成本处理平台上具有较大的应用价值。

参 考 文 献

[1] 刘少强,姜军.基于FPGA的线性调频信号脉冲压缩设计[J].国外电子测量技术,2017,36(4):44-47.[Liu Shao-qiang, Jiang Jun. Design of linear frequency modulation signals pulse compression based on FPGA[J].Foreign Electronic Measurement Technology, 2017,36(4):44-47.]

[2] Tian H S, Chang W G, Li X Y. An improved method for the real-time pulse compression based on FPGA[C].The 8th International Congress on Image and Signal Processing, Shenyang ,China, October 14-16,2015.

[3] 丁鹭飞,耿富录,陈建春.雷达原理[M].北京:电子工业出版社,2014.

[4] 李翱,于勇,褚超,等.基于FPGA的高效脉冲压缩工程应用研究[J].遥测遥控,2017,38(2):13-21.[Li Ao ,Yu Yong, Chu Chao, et al. Engineering application research of efficient pulse compression technology based on FPGA[J].Journal of Telemetry, Tracking and Command, 2017,38(2):13-21.]

[5] Xilinx, Inc. Fast Fourier transform v 9.0 product guide [EB/OL]. 2017[2017]. https://www.xilinx.com/support/docum-entation/ip_documentation/xfft/v9_0/pg109-xfft.pdf.

[6] Richarsd M A.雷达信号处理基础[M]. 邢孟道,王彤,李真芳,等译.北京:电子工业出版社,2008.

[7] Fu N, Wang Y, Xu H, et al. Method of LFM pulse compression implementation based on FPGA[C].The 11th International Conference on Electronic Measurement & Instruments, Harbin, China,August 16-19,2013.

[8] 王静,朱剑,杜科.宽带正交解调和脉冲压缩优化处理及FPGA实现[J].制导与引信,2015,36(1):23-28.[Wang Jing, Zhu Jian, Du Ke. Optimization processing and FPGA implementation of wideband demodulation and pulse compression[J].Guidance and Fuze,2015,36(1):23-28.]

[9] Vikram T, Amit K V, Paramananda J,et al.Design and implementation of FPGA based digital pulse compression via fast convolution using FFT-OS method[C]. International Conference on Microwave, Optical and Communcation Engineering, IIT Bhubaneswar, India, December 18-20,2015.

[10] 顾峰,戴健.一种基于FPGA的频域脉冲压缩处理器的实现[J].舰船电子对抗,2016,39(4):105-109.[Gu Feng,Dai Jian.Realization of a pulse compression processor in frequency domain based on FPGA[J].Shipboard Electronic Counter Measure,2016,39(4):105-109.]

[11] 何宾.Xilinx FPGA权威设计指南—Vivado2014集成开发环境[M].北京:电子工业出版社,2015.

[12] 顾义坤,倪风雷,刘宏.Xilinx FPGA自主配置管理容错设计研究[J].宇航学报,2012,33(10):1519-1527.[Gu Yi-kun,Ni Feng-lei, Liu Hong. Fault-tolerance design of Xilinx FPGA with self-hosting configuration management[J]. Journal of Astrona-utics, 2012,33(10):1519-1527.]

[13] 侯建文,张爱兵,郑香脂,等.FPGA 单粒子翻转事件在轨探测研究[J].宇航学报,2014,35(4):454-458.[Hou Jian-wen,Zhang Ai-bing,Zheng Xiang-zhi,et al.Research on in-orbit detection of SEU of FPGA[J].Journal of Astronautics,2014,35(4):454-458.]