基于ATE的ADSP测试

2018-06-25武乾文奚留华张凯虹

武乾文,奚留华,张凯虹

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

ADSP就是高级信号处理器[1-2]。美国模拟器件公司 (ADI)继ADSP-TS101后在2003年推出新一代Tiger-SHARC处理器ADSP-TS201。此处理器片内集成更大容量的存储器,性价比高,兼有ASIC、FPGA的信号处理性能以及指令集处理器的可编程性和灵活性,适用于性能要求高、存储量大的信号处理以及图像应用,如雷达与声纳、无线基站、图像处理以及工业仪器等领域。

ADSP的应用广泛,其在生产、应用等各个阶段都要进行测试以确保产品质量以及研制出符合系统要求的电路,尤其应用于军工设备的ADSP,为控制质量,保障装备可靠性,集成电路检测、筛选至关重要[3-6]。但ADSP属于大规模集成电路,其内部集成度高、模块复杂,外部引脚数量大,其功能测试具有一定的难度。

2 测试仪器和电路

G150测试机具有精度高、操作方便等特点,适于对ADSP-TS201S电路的测试。该系统测试频率30 MHz,测试通道数达512个,测试向量深度可达1M。

3 功能测试

3.1 ADSP功能原理

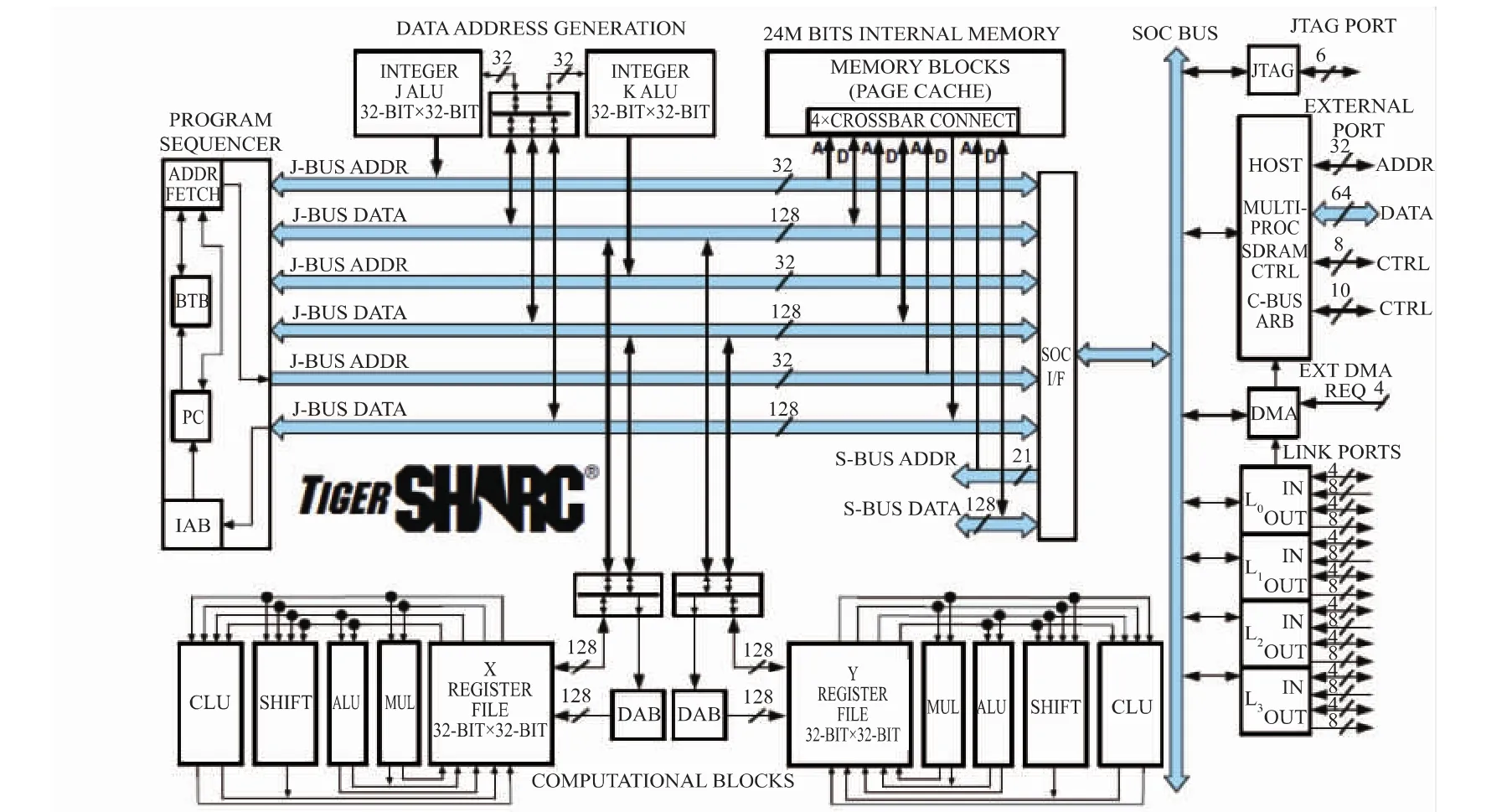

TS201在TS101结构的基础上做了进一步改进。其改进结构如图1所示,TS201S可分成DSP核以及I/O接口,通过4条总线传输数据、地址及控制信号。

DSP包含程序控制器、地址产生器及双运算模块。程序控制器能提供可中断的编程模式,可以支持汇编语言C/C++编程以及10指令周期流水;IAB能预存5条指令;BTB能够减小分支跳转延迟。地址产生器包括2个IALU,能支持立即寻址以及间接寻址;支持位反序以及环形缓冲寻址,方便对数字信号处理特殊运算。双运算模块能独立工作实现SIMD引擎,每个周期运算模块能执行2条运算指令。

图1 ADSP-TS201S电路原理图

I/O接口包含内部存储器、外部设备接口、DMA控制器、链路口以及JTAG口。内部存储器为24 Mb DRAM。TS201S及TS101S采用0.13 μm CMOS工艺制造,TS201S的存储器容量为TS101S的4倍,其性能比TS101提高了很多。外部设备接口包含主机接口、多处理器接口、SDRAM接口以及EPROM接口。14个DMA通道无需干预可完成设备的数据交换;完成了双向链路口应用低压差分信号(LVDS)链路口技术,达到4 Gbps数据吞吐量。IEEE1149.1兼容JTAG接口,可用于片上仿真。

TS201S支持32位及40位浮点运算和8、16、32和64位定点运算。每周执行4条指令,在600 MHz时钟频率下能够达到48亿次/s乘法运算(GMACS)以及36亿次 /s浮点运算(GFLOPS)速度[7]。

3.2 ADSP功能码编写

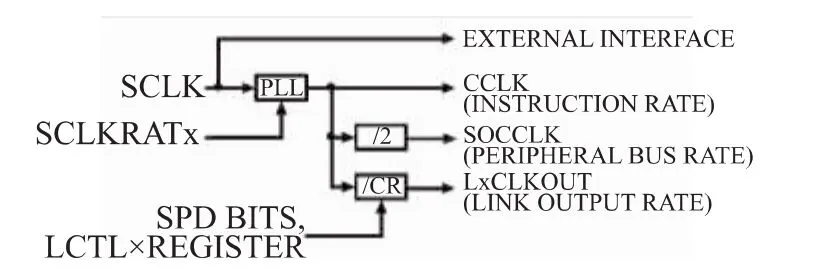

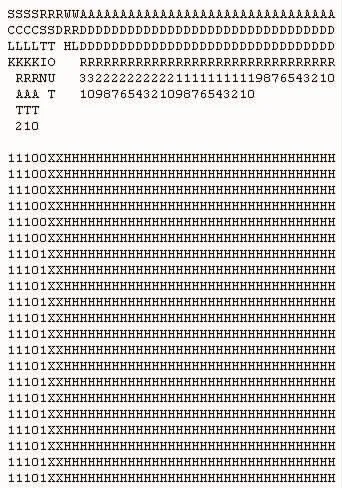

应用ATE对ADSP-TS201S功能码测试格式为二进制格式。ADSP-TS201S电路共有512个管脚,其中265个是INPUT、OUTPUT及INPUT/OUTPUT管脚,由于芯片管脚数多,为了验证其功能,先要启动芯片。选择系统时钟管脚及复位管脚分别输入信号,观察芯片输出管脚的情况。如图2所示,ADSP-TS201处理器的系统时钟有4种,分别是系统时钟(SCLK)、内核时钟(CCLK)、外设总线时钟(SOCCLK)以及链路口输出时钟(LxCLKOUT)。

图2 ADSP-TS201处理系统时钟

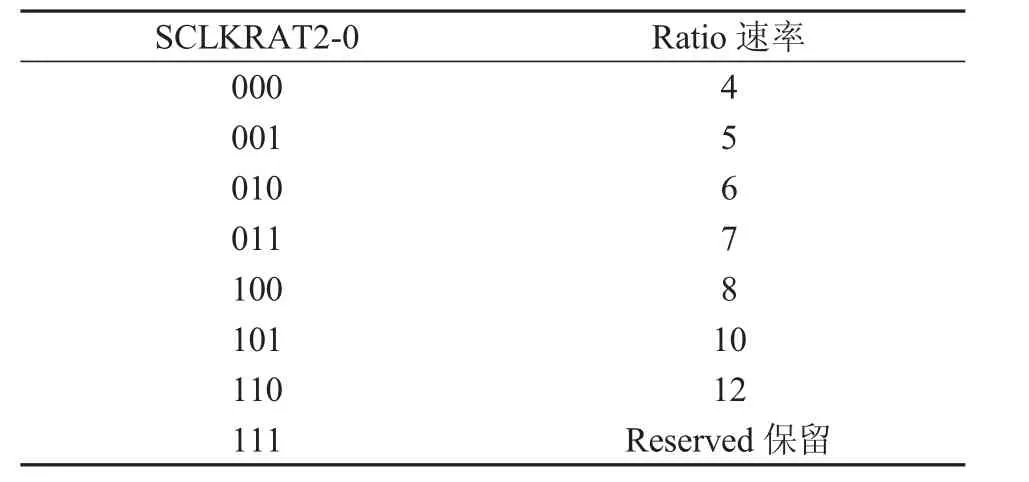

其系统时钟为外部总线口提供时钟,作为外部总线信号AC规范参考。内核时钟为内核、内部总线、存储器、链路口来提供时钟,其指令执行速度为CCLK。CCLK=SCLK×SCLKRATx,如表 1所示,SCLKRATx的取值范围为4~12。

外设置总线时钟,即为SOC总线工作的频率,为1/2×CCLK。链路口输出的时钟为CCLK/CR,其CR是LCTx速度设置位,取值范围是1~4。

系统时钟输入管脚分别为SCLK、SCLKRAT2、SCLKRAT1、SCLKRAT0等管脚。根据对外部总线速度以及CCLK、指令的执行速度考虑,测试本芯片时SCLK取30 M,应用于设置PLL时钟的倍率N值是由3个外接引脚SCLKRAT2-0来决定的,3个外接引脚连接了拨扭开关,可以随时调整倍频系数的大小,系数默认状态取5,核时钟由SCLK倍频产生,核时钟CCLK=N×SCLK=150 M。

表1 ADSP-TS201时钟速率

复位输入管脚是RSTIN管脚。ADSP-TS201S有3个引脚决定了复位电路,分别是RST-IN、RST-OUT以及POR-IN。RST-IN是复位输入,是复位引脚,其作用是设置DSP为确定状态,使得程序进入空闲状态,再根据复位操作的类型,RST-IN在指定时间确认。RST-OUT是复位输出,是RST-IN的同步延迟,说明DSP复位已经完成了。PORIN是DRAM电源复位设置。

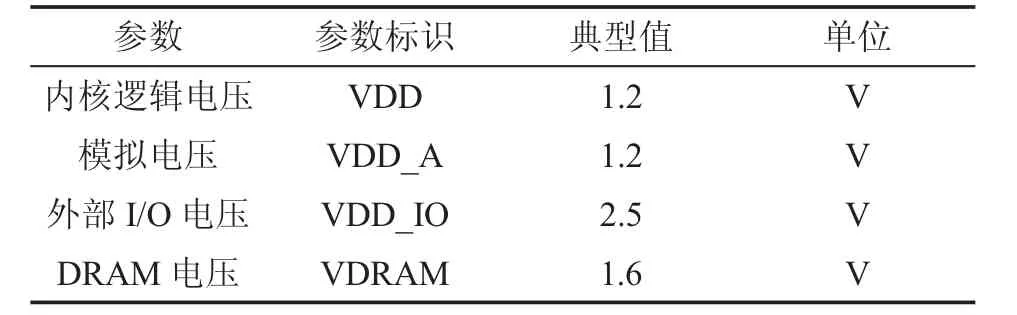

除此以外,电源管脚分别是VDD_IO、VDD_DRAM、VDD_A、VDD 等,如表 2 所示,VDD 为内核逻辑电源、VDD_A为模拟电源、VDD_IO为外部I/O电源、VDRAM为DRAM电源。

表2 ADSP-TS201处理系统电源

参考电压管脚分别为SCLK_VREF、VREF。参考电压定义输入缓冲阈值点,对输入引脚及时钟输入信号设置电压。在测试过程中,分别设置SCLK_VREF、VREF管脚为1.2 V。

如上所述,加电及输入时钟、复位信号后,得到如图3的运行结果,所有地址位都显示H(高电平),芯片并没有启动工作,分析其原因,可能是因为某些管脚未加入信号,导致启动失败。

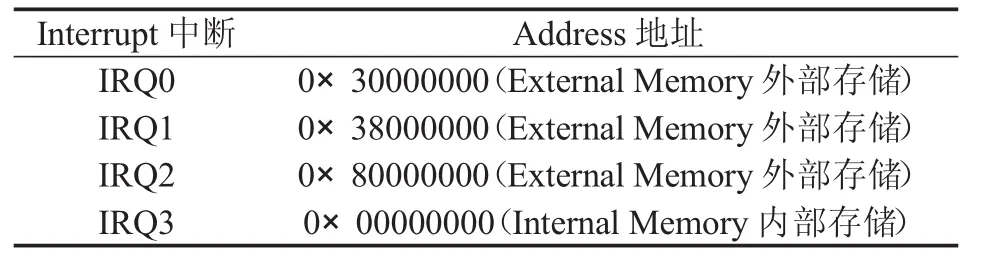

经分析,芯片未加入中断信号,在重置之后对于启动操作,ADSP-TS201S有 4种引导选择:(1)EPROM 引导;(2)外围设备引导;(3)链路口引导;(4)无引导模式,如表3所示,一个IRQ3-0的中断信号输入,存储器启动地址选择。

图3 ADSP-TS201S未启动状态

选择无引导模式,当输入一个中断信号,ADSP-TS201S启动存储器。

表3 无引导模式启动存储器地址

ADSP-TS201S处理器在理想状态总是跳出重置,等待一个中断信号的输入。在输入一个IRQ3-0的中断信号后,ADSP-TS201S仍然没有出现存储器地址的叠加状态,直到循环了60万次以后,芯片启动,存储器地址开始叠加。经分析,芯片反应过慢可能是某个控制管脚未输入信号导致的。

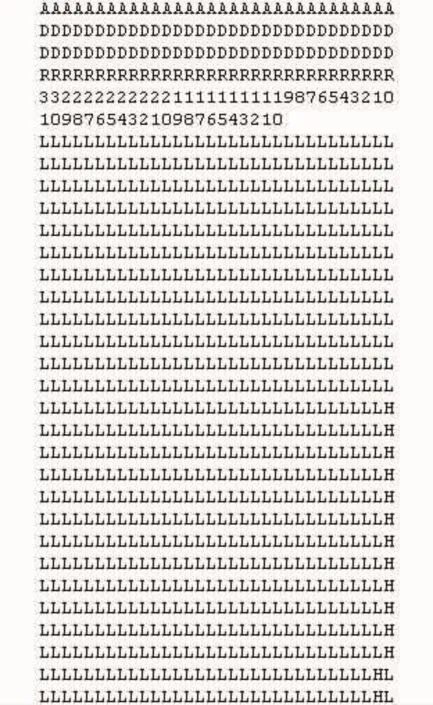

当输入BM及BMS等管脚信号,ADSP-TS201S启动迅速,地址开始自动叠加,如图4所示。

图4 ADSP-TS201S启动状态

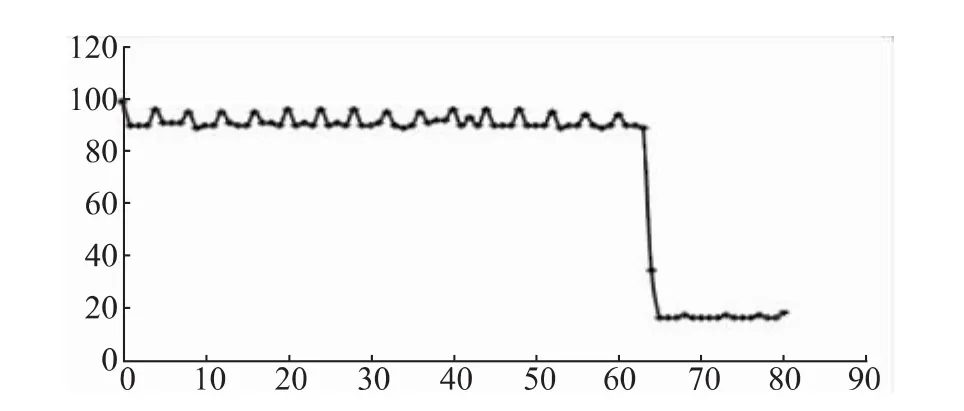

由图4所示,同组地址数为12个,此时SCLKRAT2-0的输入数据为011,当其输入不同信号时,同组地址数不同。以输入数据110为例,如图5所示,0地址的地址数为99个,当经过66个地址变化,同组地址的个数稳定为18个。

图5 地址数随地址的变化

4 ADSP直流参数测试

直流参数测试包括开/短路测试(O/S)、输出高/低电平测试(VOH/VOL)、输入高/低电流测试(IIH/IIL)、输入漏电流测试(ILI/ILO)、电源电流测试(ICC)等等。

5 ADSP交流参数测试

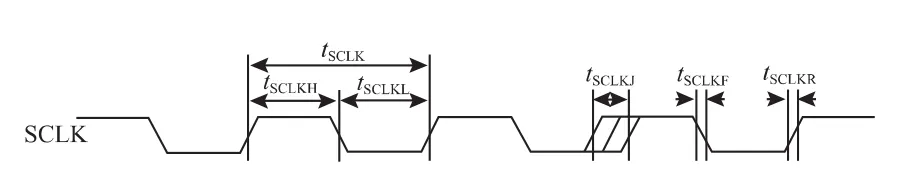

交流参数测试是测量器件晶体管转换的时序关系,目的是保证器件在正确的时间发生状态转换。如图6、图7所示,ADSP-TS201S交流参数包括核心时钟循环时间tCCLK、系统时钟循环时间tSCLK、系统时钟循环高电平时间tSCLKH、系统时钟循环低电平时间tSCLKL、系统时钟转换时间下降沿tSCLKF、系统时钟转换时间上升沿tSCLKR、系统时钟抖动容忍度tSCLKJ。

图6 参考时钟——系统时钟循环时间

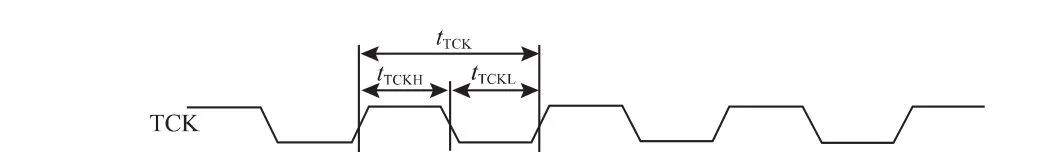

测试时钟循环时间tTCK、测试时钟循环高电平时间tTCKH、测试时钟低电平时间tTCKL,见图7。

图7 参考时钟——测试时钟循环时间

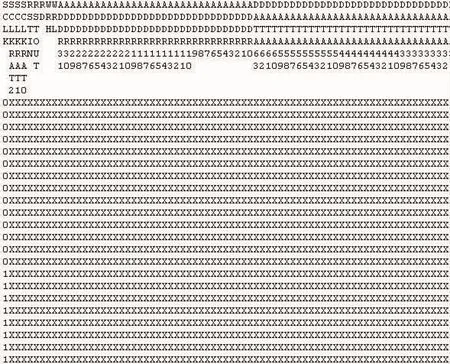

由于各交流参数的测试原理和测试方法基本相同,仅以测试TSCLKR为例来说明交流参数的测试过程。在常温下,把被测器件接入测试系统,电源电压调到规定的电压值,其余输入端施加规定的电平。测量系统时钟从0变到1上升沿时间tSCLKR,通过搜索的方式获得其值,功能码如图8所示。

图8 tSCLKR测试的功能码

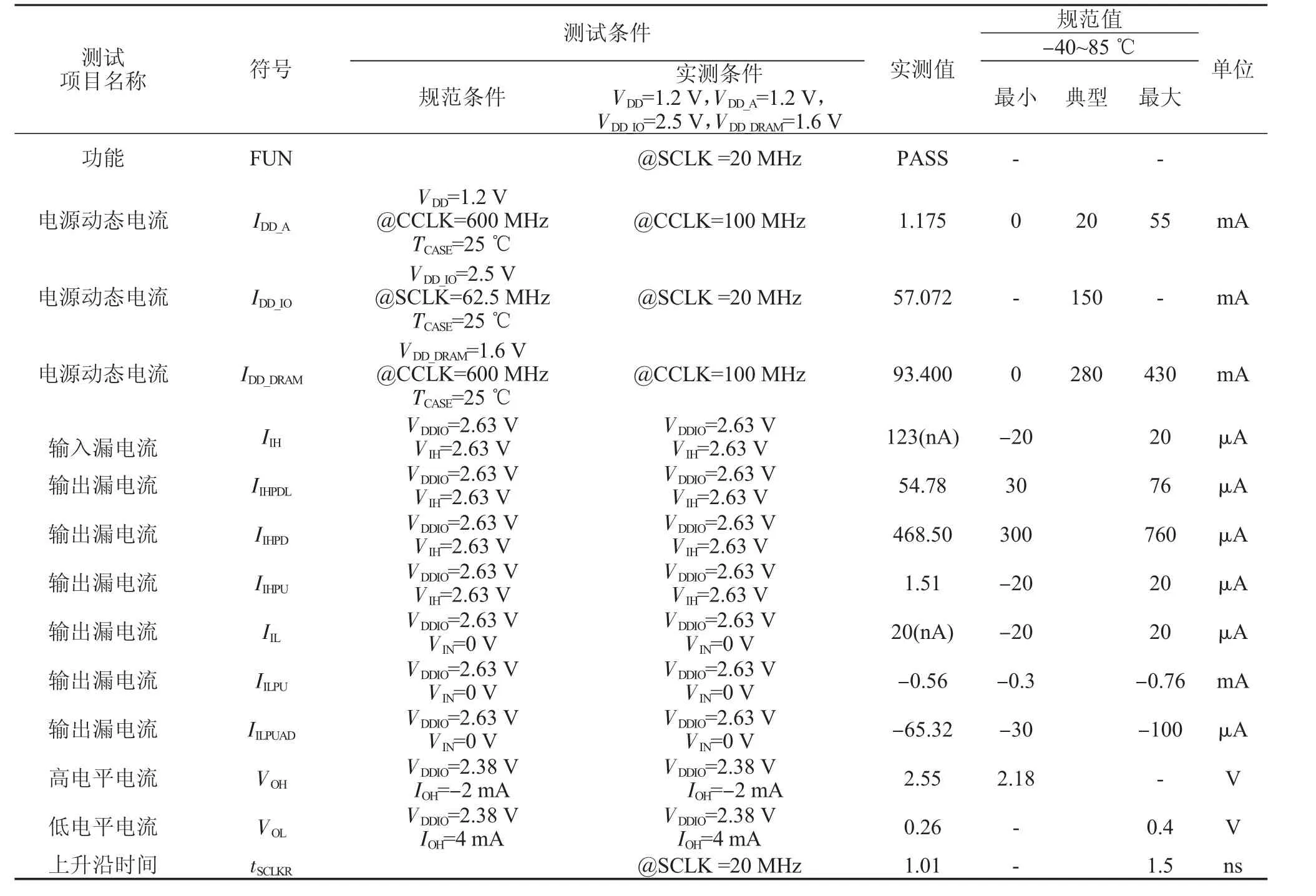

6 测试方法与标准验证

参考SRAM测试的直流参数规范标准,在规范测试条件下的测试值在标准范围内,验证了测试方法的正确性,如表4所示。

7 结论

文章简要介绍了ADSP的重要组成部分,提出了一种ATE对ADSP测试的方法。主要介绍了电路的功能测试及交流参数测试的关键技术。通过Ultra Edit软件编辑生成测试码,导入测试仪器,对被测器件进行地址叠加操作,以检查其功能。与此同时,结合部分功能码,在ATE软件中设置相关参数,测试了ADSP的交流参数。

[1]孙洁朋,魏建民,闫华,等.一种FPGA芯片中DSP模块的内建自测试方法[J].电子与封装,2017,17(10):9-12.

[2]李炜,于清涛,李旭,等.基于DSP的高压节点在线测试系统设计[J].油气田地面工程,2016,(11):89-92.

[3]时万春.集成电路测试技术的新进展[J].电子测量与仪器学报,2007,21(4):1-4.

[4]谢正光.集成电路测试相关标准研究与探讨[J].微电子学,2004,34(3):246-253.

表4 测试实际值与规范标准对比验证

[5]毕威.简述 IC 测试的意义和作用[J].微处理机,2017,(1):6-12.

[6]俞建峰,陈翔,杨雪瑛.我国集成电路测试技术现状及发展策略[J].中国测试,2009,35(3):1-5.

[7]庞娜,刘书明,徐平.ADSP-TS201S芯片的功能和应用[J].国外电子元器件,2005,(1):48-51.