碳化硅MOSFET电路模型及其应用

2018-06-14周郁明刘航志杨婷婷

周郁明, 刘航志, 杨婷婷, 王 兵

(安徽工业大学 电气与信息工程学院,安徽 马鞍山 243002)

相较传统的硅(Si)材料金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor,MOSFET),基于第三代半导体材料碳化硅(SiC)的MOSFET更能胜任大功率、高温度等严酷的应用环境[1-2].

在实际情况下,由于人为因素或者负载故障,功率半导体器件有时会运行在短路或雪崩条件下,这种情况尽管一般非常短暂,但是会退化器件的特性甚至引起器件失效.目前,不少文献对SiC MOSFET在短路状态下的鲁棒性和失效进行了实验测试以及理论模型分析[3-8],这些文献多集中在直流母线电压、驱动条件以及线路寄生参数等外部影响因素的研究.

众所周知,SiC MOSFET在热氧化生长氧化层(SiO2)的过程中,在SiC/SiO2界面生成了大量的陷阱[9].这些陷阱能够降低沟道中自由电子Fowler-Nordheim(FN)遂穿的有效势垒高度,增强电子在SiC MOSFET氧化层中的隧穿几率;同时,为了减小导通电阻,SiC金属氧化物半导体(Metal Oxide Semiconductor,MOS)器件的氧化层厚度一般要比Si MOS器件的薄[7],这在一定程度上也增强了电子在氧化层中的隧穿几率.电子隧穿几率的增加,直接导致栅极氧化层的泄漏电流增加.另外,处于短路状态下的功率半导体器件承受着很高的电流应力,器件温度急剧上升,温度升高加剧了电子往氧化层中的注入,也导致了氧化层泄漏电流增加.同时,在栅极驱动电压消失后,器件内部大量的热量来不及散发出去,会导致MOSFET结构中的P阱区/N漂移区的PN结存在着密度很高的泄漏电流,器件继续自热,并最终可能造成器件损坏.

在传统的SiC MOSFET电路模型的基础上,笔者建立了一种新颖的、计入SiC/SiO2界面陷阱的SiC MOSFET电路模型,模型引入了漏源极的PN结泄漏电流模型和栅极氧化层的泄漏电流模型.利用该模型评估了不同密度的界面陷阱对处于短路状态下SiC MOSFET特性的影响,所取得的结果对SiC MOSFET的驱动电路、故障保护电路的设计以及SiC MOS器件技术都具有一定的参考意义.

图1 考虑泄漏电流的SiC MOSFET等效电路模型

1 模型的建立

1.1 SiC MOSFET的电路模型

图1为文中所建立的新颖的SiC MOSFET等效电路模型.其中,虚线框内为不少文献所采用的SiC MOSFET等效电路模型[10-12],该模型由受控电流源ICH以及外围电路构成.ICH是基于Shichman-Hodges物理模型的三段电流表达式,分别描述MOSFET工作在截止区、线性区和饱和区; 外围电路主要是CGD、CGS和CDS这3个结电容来描述MOSFET的动态特性.一些文献在此模型的基础上增加了温控源,用于补偿温控静态特性[10-11].笔者在虚线框所示的电路模型基础上,增加了两个受控电流源IG=LK和IDS=LK,分别来描述SiC MOSFET的栅极氧化层泄漏电流和漏源极PN结的泄漏电流.

1.2 泄漏电路模型

1.2.1 栅极氧化层泄漏电流模型

对于SiC/SiO2结构的泄漏电流,以往观点认为只有Fowler-Nordheim遂穿起决定作用[7, 13-14].然而,随着温度升高,N沟道MOSFET氧化层中电子的遂穿加剧,因而表明还存在热激励的陷阱辅助遂穿形式的导通机制,而Poole-Frenkel (PF)发射模型可以很好地拟合栅极氧化层泄漏电流(JG=LK)与FN电流(JFN)的差值[13-14],即JG=LK=JFN+JPF.文中所使用的FN与PF电流模型及其参数[13-15]如下:

其中,msc=0.29me,mox=0.42me,φB= 2.68- 0.007(T- 300),Eox= (VGS-Vfb)tox,φt= 1.2 eV,εox= 5.14.

1.2.2 PN结泄漏电流模型

大量的实验结果表明,工作在短路状态下的SiC MOSFET,即使在栅极驱动电压消失后,器件的漏极存在着较为明显的拖尾电流[4-6, 8].众所周知,MOSFET是多子器件,不存在像IGBT那样的少子储存效应,因而正常关断时是不会出现拖尾电流的.这一现象说明处于短路状态下的MOSFET,在栅极驱动电压消失后,其结构中的P阱区/N漂移区构成的PN结存在着较高的泄漏电流.

一般地,半导体PN结的泄漏电流包括热产生电流(Ith)、雪崩电流(Iav)和扩散电流(Idiff),文中所用到的3种电流模型及其参数如下[6]:

其中,NA=3.5×1017cm-3,ND=7.5×1015cm-3,τg= 2 ns,S= 0.124 cm2,αn= 4.6× 105exp(-1.78× 107E),αp= (6.3× 106- 1.07× 104T) exp(-1.87× 107E),Jn=IDSS,Jp=0,εSiC= 9.7× 8.854× 10-14F·cm-1,Dn= (kTq)μn,Dp= (kTq)μp,Ln= (Dnτn)1/2,Lp= (Dpτp)1/2,ni= (NVNC)1/2exp(-Egq(kT)).

1.3 反型层迁移率模型

图1中的沟道电流ICH是基于Shichman-Hodges物理模型的标准长沟道器件模型,模型中的常数迁移率不足以描述SiC/SiO2界面陷阱对沟道自由电子的散射作用.一般地,沟道中的自由电子遭受4种散射,分别是体晶格散射、声子散射、表面粗糙度散射和库仑散射,4种散射所对应的迁移率分别用μB、μAC、μSR和μC来表示,根据Mathiessen法则,SiC MOSFET沟道中自由电子的反型层迁移率μinv可表示为[16]

在上述表达式中,T代表器件工作温度,Qinv为反型层电荷,Qtrap为界面陷阱电荷,E⊥为沟道有效电场,其余符号为常数或者经验值[16].

笔者用上述反型层迁移率μinv替换标准的长沟道器件模型中的常数迁移率,这样,沟道电流ICH集成了SiC/SiO2的界面参数即界面陷阱电荷Qtrap.

2 结果与分析

目前,最有效的减小SiC/SiO2界面陷阱密度、提高SiC MOSFET迁移率的方法是一氧化氮(NO)气氛下的高温钝化,能够将SiC/SiO2界面陷阱密度减小两个数量级.笔者选取文献[17]在 1 175℃ 的NO气氛下,分别经过 120 min、15 min、0 min 这3个不同退火时间得到的SiC/SiO2界面陷阱(interface trap)密度在能级中的分布,并分别定义为trap0、trap1、trap2.而界面陷阱电荷Qtrap则是界面陷阱密度对能级的积分[16].3个不同退火时间的Qtrap分别为 7.00× 1010cm-2、1.40× 1011cm-2和 2.57× 1011cm-2,并定义为Qtrap0、Qtrap1和Qtrap2.

2.1 栅极氧化层泄漏电流模型的验证

笔者首先对所采用的栅极氧化层的泄漏电流模型进行了验证.图2是在不同氧化层电场强度(Eox)和宽温度范围内,模型的泄漏电流和文献[13]实测数据的对比,图中同时画出了常规的、没有栅极泄漏电流模型的仿真结果.由图可见,文中所采用的模型能准确反映出不同温度下SiC MOSFET栅极氧化层的泄漏电流随电场强度的变化,而传统的模型因没有集成栅极氧化层泄漏电流及温度参数,则不能反映出这种变化.

基于所建立的模型,笔者讨论了SiC MOSFET栅极氧化层在硬开关短路状态下的退化.由于电子的隧穿作用,沟道中的电子往MOS器件氧化层中注入,并形成泄漏电流,在短路状态下,这种注入变得更加强烈,因而器件特性的退化也变得更加明显.MOSFET栅极氧化层的退化,一个重要的标志是当正常的驱动脉冲加在栅极时,器件的栅极驱动电压(VGS)在脉冲的后期出现了下降[3, 5, 7].图3示出了直流母线电压为 500 V 的短路状态下SiC MOSFET栅极驱动电压的波形.图3中的小插图对比了3种界面陷阱分布对VGS退化的影响.由图3可见,界面陷阱密度对SiC MOSFET的栅极氧化层的退化并没有多大的影响,这是因为在短路状态下MOS器件内部产生了大量的热量,增加了电子往氧化层中注入的几率,尽管界面陷阱能够降低FN隧穿的势垒高度,但是此时与温度相关的PF热发射在氧化层的电子注入机制中占据了主导作用[13-14].

图2 SiC/SiO2结构JGLK-Eox特性实验与模型对比图3 界面陷阱密度引起的FN势垒降低对VGS的影响

2.2 PN结泄漏电流模型的验证

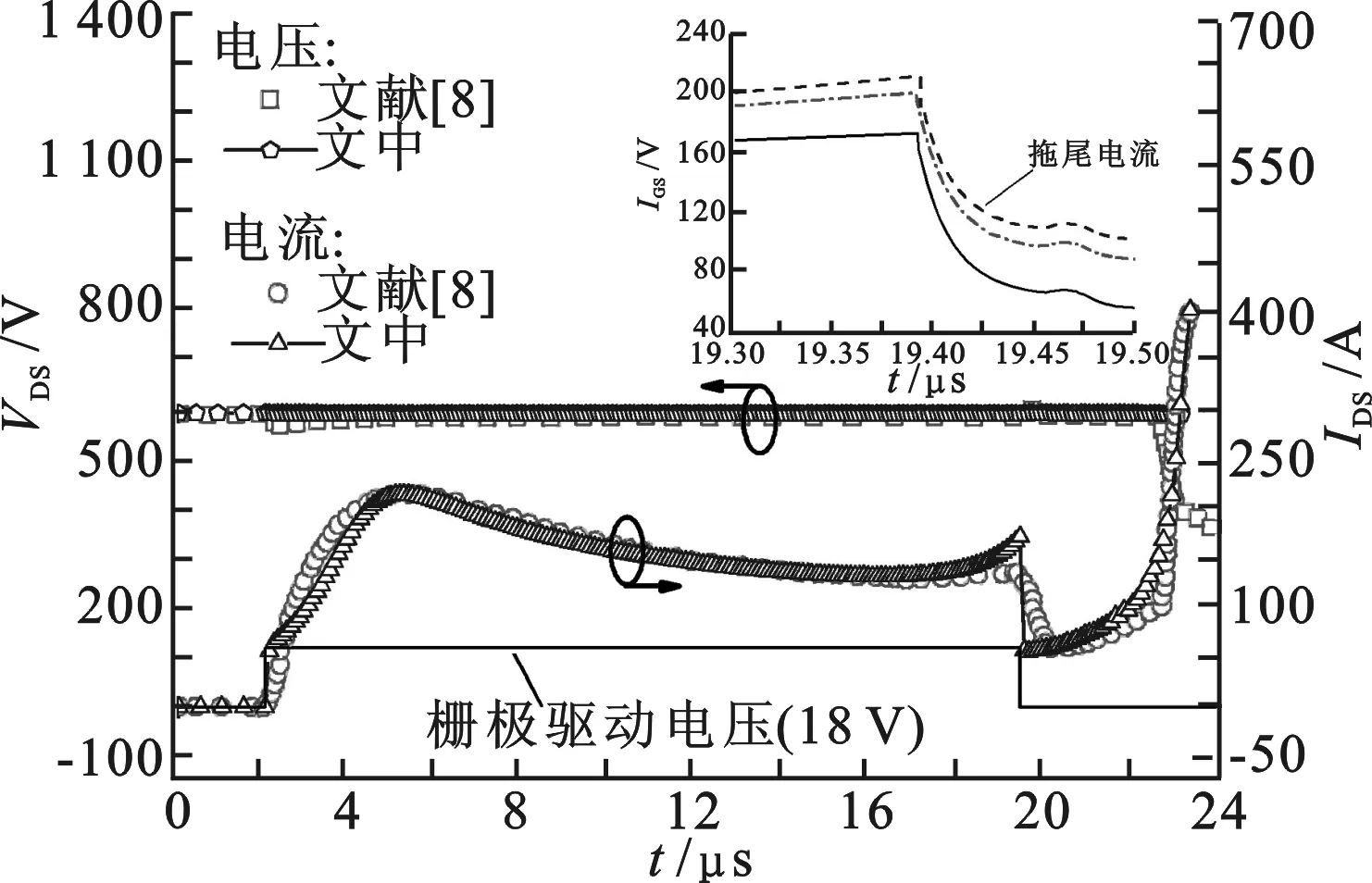

为了验证PN结泄漏电流模型的准确性,笔者先将模型的仿真数据与文献[8]的实验结果进行对比,其中硬开关短路电路结构和参数与该文献的保持一致.图4为短路状态下SiC MOSFET漏源电流(IDS)和漏源电压(VDS)实验数据和仿真的对比.可以看到,模型的仿真结果和文献的实验数据取得较好的吻合度.

图4 短路状态下SiC MOSFET模型与实测VDS、IDS波形对比图5 短路状态下不同界面陷阱密度对应的SiC MOS-FET短路电流IDS与器件温度Tj

进一步地,笔者对3种不同的SiC/SiO2界面陷阱密度所对应的短路电流与器件结温的动态波形进行了对比,结果如图5所示.由图5可见,在器件出现失效时,器件的结温达到 1 000 K 左右,文献[5-6]的实验结果也与此数据相近;同时,还可以看到,界面陷阱电荷Qtrap越高,器件出现失效的时间反而延长,也就是说,器件能够承受短路电流应力的能力反而增加.这是由于Qtrap越高,MOSFET反型层的电子数量越少,其通态电阻越高,因而在相同的直流母线电压下短路电流应力变小,器件失效的时间出现了延迟.

图6 延缓失效的VDS、IDS波形对比

图5所对应的失效,本质上是由于短路状态下的电流密度大、器件温升快所导致的热损坏,此时驱动电压仍施加在栅极上,实际短路测试中,SiC MOSFET还会表现出前文所述的另外一种失效模式即延缓失效.这种失效是在栅极驱动电压消失后,由于器件内部热量没有及时散发、温度仍很高,MOSFET结构中P阱区/N漂移区的PN结存在很高的泄漏电流,导致器件也出现了失效.图6示出了SiC MOSFET“延缓失效”时的VDS、IDS与文献[8]的对比,所对应的栅极驱动电压也在图中示出,3种界面电荷所对应的器件在栅极驱动电压消失时刻的拖尾电流也以小插图的形式在图中示出.从图6中可以看出,栅极驱动电压在t= 19.4 μs 消失后,器件的拖尾电流仍保持较高的水平,文献[4-6]也验证了这一点.

表1 不同密度界面陷阱的SiC MOS的短路耐受能力

衡量功率半导体器件短路特性的两个重要参数,一个是一次短路测试过程中不致器件失效的临界能量(Ecr),一个是短路耐受时间(tscwt).这两个参数的值越高,意味着器件能够抵御短路电应力的能力越强.表1列出了3种界面陷阱所对应的Ecr和tscwt,可见随着SiC/SiO2界面陷阱密度的增加,Ecr和tscwt均呈现上升的趋势,表明器件抵御短路电应力的能力增加,从而为短路故障保护装置可靠动作赢取更多时间,有利于功率变换系统安全运行.

3 结 束 语

文中建立了包含SiC/SiO2界面陷阱效应的SiC MOSFET的电路模型,引入了栅极氧化层的泄漏电流模型和PN结的泄漏电流模型.验证了所建立的SiC MOSFET模型的准确性,评估了工作在短路状态下的SiC MOSFET的性能退化或者失效机制.结果表明,在短路状态下,高密度的界面陷阱能够减缓SiC MOSFET的热应力,延长器件的短路故障耐受时间;短路引起的栅极驱动脉冲的退化主要是电子的Poole-Frenkel (PF)发射引起的,而界面陷阱引起的FN遂穿势垒的降低带来的影响并不明显.

[1] 汤晓燕, 张玉明, 张义门. 4H-SiC n-MOSFET新型反型层迁移率模型[J]. 西安电子科技大学学报, 2011, 38(1): 42-46.

TANG Xiaoyan, ZHANG Yuming, ZHANG Yimen. New Inversion Channel Electron Mobility Model of the 4H-SiC n-MOSFET [J]. Journal of Xidian University, 2011, 38(1): 42-46.

[2] 韩茹, 杨银堂. 6H-SiC NMOS与PMOS温度特性分析[J]. 西安电子科技大学学报, 2007, 34(1): 16-20.

HAN Ru, YANG Yintang. Analyses of the Temperature Properties of the 6H-SiC NMOS and PMOS[J]. Journal of Xidian University, 2007, 34(1): 16-20.

[3] KAMPITSIS G, PAPATHANASSIOU S, MANIAS S. Comparative Evaluation of the Short-circuit Withstand Capability of 1. 2 kV Silicon Carbide(SiC) Power Transistors in Real Life Applications[J]. Microelectronics Reliability, 2015, 55(12): 2640-2646.

[4] OTHMAN D, BERKANI M, LEFEBVRE S, et al. Comparison Study on Performances and Robustness between SiC MOSFET & JFET Devices-Abilities for Aeronautics Application[J]. Microelectronics Reliability, 2012, 52(9/10): 1859-1864.

[5] ROMANO G, FAYYAZ A, RICCIO M, et al. A Comprehensive Study of Short-circuit Ruggedness of Silicon Carbide Power MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 978-987.

[6] WANG Z, SHI X, TOLBERT L M, et al. Temperature-dependent Short-circuit Capability of Silicon Carbide Power MOSFETs[J]. IEEE Transactions on Power Electronics, 2016, 31(2): 1555-1566.

[7] NGUYEN T T, AHMED A, THANG T V, et al. Gate Oxide Reliability Issues of SiC MOSFETs under Short-circuit Operation[J]. IEEE Transactions on Power Electronics, 2015, 30(5): 2445-2455.

[8] CHEN C, LABROUSSE D, LEFEBVRE S, et al. Study of Short-circuit Robustness of SiC MOSFETs, Analysis of the Failure Modes and Comparison with BJTs[J]. Microelectronics Reliability, 2015, 55(9/10): 1708-1713.

[9] YOSHIOKA H, SENZAKI J, SHIMOZATO A, et al. Effects of Interface State Density on 4H-SiC n-channel Field-effect Mobility[J]. Applied Physics Letters, 2014, 104(8): 83516.

[10] WANG J, ZHAO T, LI J, et al. Characterization, Modeling, and Application of 10-kV SiC MOSFET[J]. IEEE Transactions on Electron Devices, 2008, 55(8): 1798-1806.

[11] SUN K, WU H, LU J, et al. Improved Modeling of Medium Voltage SiC MOSFET within Wide Temperature Range[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2229-2237.

[12] CHEN K, ZHAO Z, YUAN L, et al. The Impact of Nonlinear Junction Capacitance on Switching Transient and Its Modeling for SiC MOSFET[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 333-338.

[13] SOMETANI M, OKAMOTO D, HARADA S, et al. Temperature-dependent Analysis of Conduction Mechanism of Leakage Current in Thermally Grown Oxide on 4H-SiC[J]. Journal of Applied Physics, 2015, 117(2): 024505.

[14] SAMANTA P, MANDAL K C. Leakage Current Conduction, Hole Injection, and Time-dependent Dielectric Breakdown of n-4H-SiC MOS Capacitors during Positive Bias Temperature Stress [J]. Journal of Applied Physics, 2017, 121(3): 034501.

[15] OUENNOUGHI Z, STRENGER C, BOUROUBA F, et al. Conduction Mechanisms in Thermal Nitride and Dry Gate Oxides Grown on 4H-SiC[J]. Microelectronics Reliability, 2013, 53(12): 1841-1847.

[17] ROZEN J, DHAR S, ZVANUT M E, et al. Density of Interface States, Electron Traps, and Hole Traps as a Function of the Nitrogen Density in SiO2on SiC[J]. Journal of Applied Physics, 2009, 105(12): 124506.