一种基于改进的tri-level电容阵列结构的SAR ADC

2018-05-30北方工业大学电子信息工程学院王立煌

北方工业大学电子信息工程学院 戴 澜 王立煌

模数转换器就是把模拟信号转换为数字信号的一种器件。在所有的模数转换器当中,逐次逼近寄存器型模数转换器(SAR ADC)以其低功耗,面积小,中等速度,中高精度的优点而广泛应用于便携式,可穿戴式,植入式电子设备当中。进一步降低SAR ADC的功耗可以延长电子设备当中电池的寿命,增加其使用的周期。SAR ADC主要包括DAC电容阵列,比较器和数字控制逻辑部分。在传统的SAR ADC当中,DAC电容阵列在工作过程当中的电荷重分配是SAR ADC主要的功耗来源。因此,降低SAR ADC的功耗便从降低DAC电容阵列功耗下手。过去已经有很多研究人员提出了许多DAC电容阵列的改进方案,以降低其能耗。文献[1]、[2]、[3]、[4]、[5]分别提出了降低DAC电容阵列转换算法的方案,相对于传统的电容阵列分别降低了92.2%、96.9%、98.4%、98.8%、99.2%的能耗。其中的许多方案看似降低了转换能耗,却在复位阶段不可避免地引入复位能量。本文基于tri-level的DAC电容阵列转换算法设计了一种10bit、1MS/s的SAR ADC。tri-level结构的DAC电容阵列可以降低整体的转换能量,而且在每个周期结束后的复位阶段没有消耗电源。但是文献[3]中的tri-level结构依然消耗很大的转换能量,本文通过改进这种方案,使其能效进一步提高。围绕着电容阵列为核心设计了比较器以及相关的电数字控制电路(见图1)。

本文的剩下的部分有以下几个方面构成,第1部分介绍整体的电路结构以及核心的电容阵列方案;第2部分描述比较器的工作原理;第3部分描述数字控制电路的结构;第4部分给出整体电路的仿真结果;文章的总结与展望将在第5部分说明。

1 整体电路和DAC电容阵列方案

本文提出的SAR ADC整体电路结构如图1所示。如上文所述,电路主要包括DAC电容阵列、比较器、数字控制逻辑电路。输入信号通过栅压自举采样开关Spc和Snc被采样到电容阵列的上极板(电容阵列当中接入到比较器输入端的极板)。上极板电平可以直接输入比较器当中,比较器比较两端电平的大小得出数字码。这些数字码存入移位寄存器当中,同时又作为控制信号,通过数字逻辑电路控制电容阵列的下极板转换到GND、Vcm、Vref三种电平,其中Vref是参考电平,Vcm=Vref/2,导致上极板电压发生相应的变化,变化之后的上极板电平又再次输入到比较器当中,如此循环直到第10位的数字码得出。对于10bit的SAR ADC需要13个时钟周期完成转换。其中有1个是复位周期,1个是采样周期,另外10个是转换周期。整体的过程也主要分为复位阶段、采样阶段和正式的转换阶段。

图1 所提出的10bit SAR ADC整体电路框架示意图

复位阶段结束后上下两端电容阵列的下极板都被初始化为GND,也就是这些下极板被连接到地。接着采样开关闭合,差分输入信号被采样到电容阵列的上极板。正式转换过程开始时采样开关断开,输入的差分信号Vip和Vin直接比较得出最高位的数字码D[1]。由于D[1]在没有发生任何电平转换时得出,电容阵列不发生电荷转移,因而最高位的转换不消耗电源的能量。当D[1]=1时,N端的电容阵列所有下极板电平转换到Vcm,由于电容阵列的上极板的两头分别接到比较器的输入端和断开的采样开关中,没有电荷流通的通路,所以上极板的电荷保持不变,因而上下极板的电压差保持不变,N端的上极板电平被抬高了Vref/2,接着用Vip和Vin+Vref/2比较得出D[2]的值。如果是D[1]=0,则P端的电容阵列所有下极板电平转换到Vcm,方式与N端的相同。从第3步之后的转换过程,文献[3]中的tri-level方案中,电容阵列下极板已转换到Vcm的电容阵列的值为2N-iC(C为单位电容值)的电容的下极板从Vcm转换到Vref或者GND,导致上极板电平发生Vref/2i-1变化,而另一端端的电容阵列一直保持不变,比较器比较这两个电平的大小便可得出第i位的数字码。在本文的N bit DAC电容阵列方案中,假设D[1]=1,且D[i]=1时,N端的电容阵列的大小为2N-iC的电容下极板从Vcm转换到Vref,导致N端上极板电平上升Vref/2i-1;若D[i]=0,P端的电容阵列的大小为2N-iC的电容下极板从GND转换到Vcm,同样导致P端上极板电平上升Vref/2i-1。D[1]=0的情况与上述D[i]=1的情况相对称。作为例子,这种改进的DAC电容阵列方案应用于4bit的DAC电容阵列如图2所示。

采用matlab对这种方案的功耗行为建模,对比其与文献[3]中的tri-level方案,横坐标代表输出的数字码(0到1023),纵坐标代表转换的能量,单位是。可以从matlab的模拟仿真图中看到,改进之后的电容阵列转换能量明显小于文献[3]中的结果(见图3)。

图2 改进的4bit tri-level电容阵列方案

图3 被提出的改进方案与文献[3]中的tri-level方案能耗对比

对于N bit的DAC电容阵列文献[3]中的tri-level电容阵列的转换能量为:

而本文当中改进的N bit的DAC电容阵列方案的转换能量为:

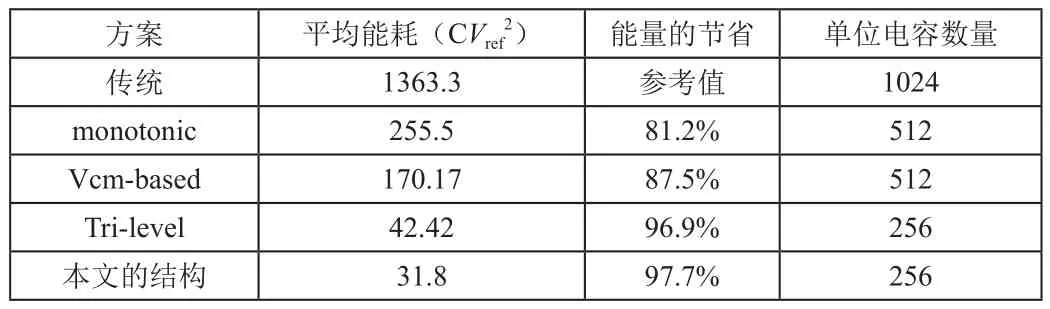

可以从以上的(1)(2)两式中推出对于10bit的SAR ADC两种方案的转换能量分别为42.42和31.8,这与matlab建模的结果相一致。表1列举了几种主要的10bit SAR ADC的电容阵列的功耗以及单位电容数量。

2 比较器

比较器是SAR ADC中另外一个重要的模块,它的精度、速度影响了整个SAR ADC的位数以及采样速率。因此,一个比较精度高,同时速度快的比较便很重要。本文中比较器应用于的低功耗SAR ADC,所以采用的是动态比较器以降低功耗。

本文采用带前置动态预放大器的两级的比较器,如图4所示,第一级为预放大器,第二级是具有锁存功能的latch比较器。这种两级的动态比较器可以同时满足低功耗低失调的功能。第二级的锁存比较器也可以单独完成比较的功能,但是由于采用了正反馈锁存的结构,它们的输入差分对管子的阈值电压失调会在引起较大的比较误差。所以采用了前置预放大器把输入信号预先放大再送入锁存比较器当中,而预放大器的失调电压较小,这便可以减小电路的失调。动态比较器只在时钟信号的边沿到来时才会工作,之前和之后都是只有泄露电流从电源流到地,所以没有静态功耗,因而大大降低了功耗。

表1 几种10bit的DAC 电容阵列方案的对比

图4 本文所采用的两级动态比较器

比较器的工作过程分为两个过程:复位阶段和采样阶段。复位阶段时,时钟信号CLK处于低电平,时钟信号CLKN是CLK经过反相器产生,因而在复位阶段除于高电平。此时M3和M4导通,M5截止,锁存器的两个输入端Dp和Dn被预充电至高电平VDD,M6截止,M13和M14导通,两个输出端被放电到地。当时钟信号的上升沿到来时M3、M4截止,M5导通,锁存器的两个输入节点Dn和Dp的电平开始下降,假设Vip>Vin,此时Dn节点电平下降的速度快于Dp节点。同时CLKN是高电平,M13、M14截止,M6导通,锁存比较器开始工作,电源通过M7、M8通路对输出节点Outp和Outn充电。由于Dn节点电平下降快,M7通路的电流将大于M8通路,所以节点Outp的上升速度快于阶段Outn,当Outp的电平上升到M12的阈值电压时,M12导通,降低了Outn的上升速度,这又反过来加快了Outp的上升速度,如此的正反馈循环最终导致Outp被拉至高电平,此时M10截止M12导通,Outn下降到了低电平。前置预放大器在开始工作前M5截止,Dn和Dp除于高电平,开始工作后M3、M4又截止了,所以电源到地的通路。不存在锁存比较器完成比较过程的时间较短,而且完成比较后Outp和Outn分别被拉到高低电平,同样不存在电源到地的通路。因此,这种比较器没有静态功耗。

3 数字控制逻辑电路

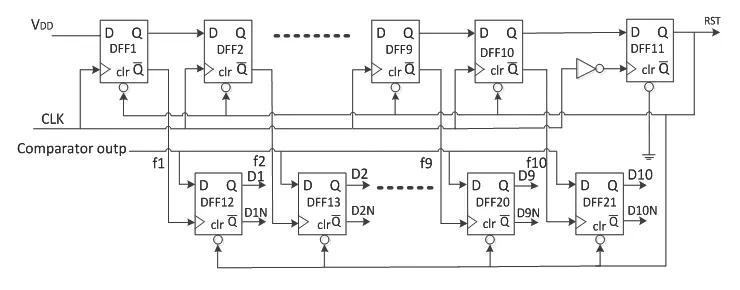

本文所设计的数字控制逻辑电路如图5所示。

图5 本文设计的移位寄存器与数字控制逻辑

如图5中所示,上面一列的D触发器由于控制时序信号,下面一列D触发器用于寄存转换出来的数字码,并且把这些数字码反馈回去控制电容阵列的下极板开关。

上面的D触发器的D与Q依次相连,下面的D触发器的D输入端全部连接到比较器的正输出端。在开始复位时,所有D触发器的Q端都被置零,复位信号结束且正常转换开始后,上面D触发器DFF1开始接收高电平信号,每隔一个周期,高电平便会向右移一位,对应的每个周期上面都有一个D触发器的反相输出端产生一个下降沿。例如,第1个转换周期时,只有DFF1的反相输出端产下降沿,这个下降沿信号作为下面的D触发器阵列DFF12的触发信号,比较器正输出端的信号只输入DFF12当中,而其他的D触发器因没有触发信号而保持原本的状态.到了第二个周期时,高电平信号被传输到DFF2中,于是DFF2的反相输出端产生下降沿,而上面的其他D触发器不发生状态的改变。这个下降沿同时触发了DFF13,比较器的正输出端的结果因而能够只存入DFF13当中。

4 电路整体仿真结果

本文所设计的10bit低功耗SAR ADC采用SMIC 40nM的工艺,电源电压为1.1V,采样率为1MS/s,整体电路在Cadence中仿真,输入信号采用两个相位相反,中间电平是0.5V,而且幅度也是0.5V的正弦模拟信号,信号的频率是16.7KHz。图5显示了ADC转换的数字码的频域图。从频域图中可以看出,输出信号的信噪失真比(SNDR)是60.8dB,无杂散动态范围(SFDR)是75.7dB,有效位数(ENOB)是9.8位。测得电路的平均电流为2.2μA,所以其整体功耗为2.43μW,FOM值表示ADC的效率值,它可以有以下公式得出:

其中Ptotal代表电路整体的功耗,fs代表采样率。由(3)可得本文所设计的电路在1MS/s的采样率下的FOM值为2.72fJ/conversion-step。

图6 输出数字码的各种频率成分的相对幅度

5 总结

本文基于对文献[2]中所提出的tri-level电容阵列的改进的基础上设计了一款10bit 1MS/s的低功耗SAR ADC。改进的tri-level电容阵列的转换能耗进一步地降低,文献[2]中的tri-level电容阵列应用于10bitSAR ADC时消耗的平均能量是42.42,但是本文所改进的方案仅仅消耗31.8的能量,能量利用率提高了25%。而且这种方案同样不消耗复位能量。

本文采用了无静态功耗的动态比较器,数字控制逻辑电路采用两列D触发器构成,所设计的SAR ADC的SNDR为60.8dB,SFDR是75.7dB,ENOB是9.8位,整体功耗仅仅2.43μW,FOM值为2.72fJ/conversion-step。

优化电容阵列算法是降低整体SAR ADC功耗的主要途径,近年来国内外也有不少研究人员将精力投入到这方面的研究,取得了不错的成果。本文所提出的电容阵列方案也可以进一步优化以使功耗降低。

[1]Zhang,H.,Zhang,R.,et al.“A Energy efficient higher side reset and set switching scheme for SAR ADC”.IEEE Electron.Lett.,vol.53,no.18,pp.1238-1240,Aug.2017.

[2]C.Yuan,Y.Lam.“Low-energy and area-efficient tri-level switching scheme for SAR ADC”.IEEE Electron.Lett.,vol.48,no.9,pp.482-483,Apr.2012.

[3]Sanyal,A.,and Sun,N.“SAR ADC architecture with 98%reduction in switching energy over conventional scheme”.IEEE Electron.Lett.,vol.49,no.4,pp.248-250,Feb.2013.

[4]Xie,L.,Wen,G.,Liu,J.“Energy efficient hybrid capacitor switching scheme for SAR ADC”.IEEE Electron.Lett.,vol.50,no.1,pp.22-23,Jan.2014.

[5]S.R.Srinivasan,P.T.Balsara.“Energy-efficient sub-DAC merging scheme for variable resolution SAR ADC”.IEEE Electron.Lett.,vol.50,no.20,pp.1421-1423,Sept.2015.

[6]Liu,C.C.,Chang,S.J.,Huang,G.Y.,et al.“A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure”.IEEE Solid-State Circuits,vol.45,no.4,pp.731-740,Apr.2010.