一种片上电压转换器电容调制方法设计

2018-05-11商德佳

商德佳

(1.中国科学院上海微系统与信息技术研究所上海200050;2.上海科技大学信息科学与技术学院,上海201210;3.中国科学院大学北京100049)

近年来,随着集成电路工艺尺寸从32 nm降到28 nm甚至更低,设计高性能低功耗多核处理器已变得迫切而又艰难。由于多核处理器片上供电网络(on-chip power delivery network,PDN)直接负责为各个内核负载配电[1],其设计在总体上决定了芯片功耗。因而,使用合理的片上配电方案、设计最优的电网降压部件已成为学术界和工业界在低功耗设计领域的研究热点[2-6]。开关电容电压转换器(switched-capacitor voltage regulator,SCVR)由于具有整体供电效率高、输出电压摆幅大的优点[7],已被Intel、IBM等厂商用于最新一代的处理器PDN系统设计中[8-9]。文献[8,10-11]中也分别提出具有频率调节功能的SCVR,虽然供电效率得到提高,但是并没有对SCVR内部电容更精细粒度的调节做更多研究。本文通过拓展SCVR在电容调制方面的优势,可以使其更好地支持动态电压调节技术,达到降低功耗的目的。

1 多核处理器PDN简介

片上供电网络设计是高速芯片电路设计和物理集成中很重要的一部分。随着VLSI设计中电源电压不断降低,为芯片设计最优的供电网络成为一个挑战。一般,片上电网由全局电网(global power grid)和局部电网(local power grid)两个层次构成,如图1所示[12-13]。全局电网从片下获取电能,经过各个DC-DC SCVR降压后,为整片芯片的所有电压域(voltage domain)供电;而某一局部电网负责为该电压域内的负载模块供电。因此,内核是全局网络的负载。为负载稳定供电,减少传输损耗,是片上电网系统应该满足的最基本要求[14]。

图1 片上供电网络模型图

2 SCVR结构及功能介绍

SCVR的主要功能是为其负载逻辑电路提供满足要求的电源电压,其将全局网络中较高的恒定VDD电压作为输入,输出相应幅度的低电压。一般SCVR由多种输出电压档位可以选择,用以满足不同的负载需求。传统SCVR主要由时序发生模块和开关电容拓扑两部分组成[15],如图2所示。本文在此基础上提出具有电容调制功能的电路与算法,能够保证SCVR以更高的效率转换电压,并将输出电压纹波控制在一定限度内。下面分别介绍这三部分。

2.1 时序发生模块

时序发生电路的功能是产生与并联排列的开关电容拓扑相同数目的时序控制信号,各个控制信号之间相移固定但占空比均为50%,用于控制开关电容拓扑的工作节奏。

图2 传统SCVR的主要组成部件[8]

本模块主要由模式选择逻辑、DAC、比较器和电平移位器(level shifter)等组成。SCVR的输出电压与参考电压的差值经过DAC和电压比较器,被转为由4个D触发器组成的循环移位器的时钟信号。经过分频且移位的4个时钟信号会与模式控制信号分别融合,再经过反相器扩充,被用来控制8个并联排列的开关电容拓扑。其中,模式控制模块根据预先设定的电压转换比率(1:1,5:4,3:2和2:1中的一种),产生相应的控制信号的逻辑,实现比率选择。

当输出电压高于参考电压时,信号会被反馈至比较器,进而使输出的时序信号频率减小,开关电容拓扑的转换速率减慢,输出电压进而会降低,达到负反馈的目的;当输出电压低于参考电压时,原理类似。通过频率调节,输出电压会被钳制在负载确定的幅度。

本文考虑频率调制易造成切换噪声(switching noise)[16],使用固定的时钟频率控制,因而并不采用比较器模块。

2.2 开关电容拓扑

开关电容拓扑由8个完全相同的开关电容电路组成,这种多片并联结构在8个相移时钟的控制下,可以交错充放电,以达到减小输出电压纹波的目的。

每片开关电容电路由NMOS+PMOS组成的开关以及MIM电容构成。MIM电容处于金属线高层区域的两层金属中间,被分成若干个标准单元供整个SCVR使用。以2:1转换比率为例的电容拓扑如图3所示,时钟信号的高低电平控制晶体管开关的开或关,进而将电容的工作节奏分为充电与放电两个阶段以一定频率交替进行。应注意,输出电压档位的选择在模式选择逻辑中已经确定,所以时钟信号对晶体管控制的同时其实也进行了档位选择。

由于固定转换电容时,同一时刻输出电压只能在较粗粒度上进行选择,即选择给定档位中的一种。为进行更精细的调节,本文提出了可变电容拓扑结构,使得电路可以有更精细的输出电压选择。图3中电容C实际上由多片电容C0并联排列而成,每条电容支路由开关控制联通到电路中的电容的个数,控制信号由控制模块生成,受负载需求决定。

图3 2:1开关电容拓扑结构

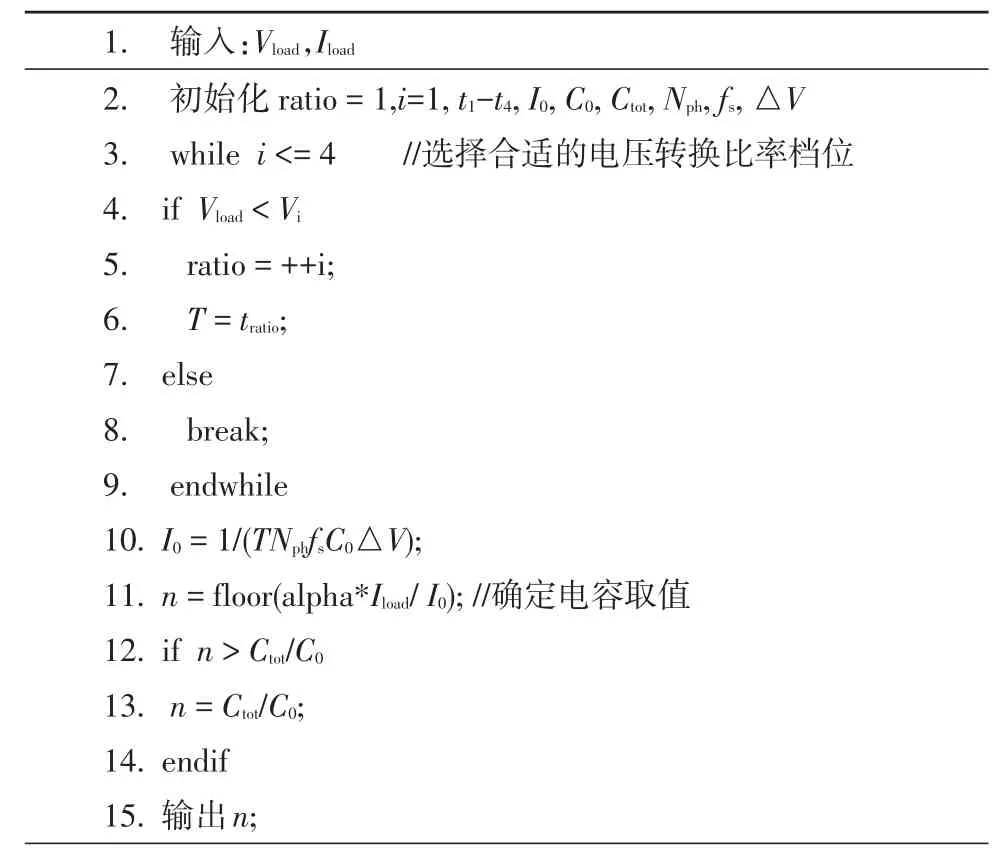

2.3 开关电容控制算法

SCVR给负载提供的电压和电流依靠转换电容交替充放电,将电源处的电荷转移到负载处。理论分析推导可以发现,输出电压固定时,电容的取值增加时,输出电阻将减少,输出电流将增大[17]。因而,可以根据负载需求,调制电容取值以满足特定需求。由于电容取值选择更加精细,输出电压与负载需求可以匹配更好,减少能量浪费,提高效率。

本文提出的电容调制算法如表1。其中Vload和Iload作为输入,是负载电压和电流需求的预测值,这里假定在电路设计阶段可以获取。第一个while循环根据负载电压需求,选择合适的电压转换比率档位。一般SCVR有至少4个以上档位可以选择,Vi为第i个档位所对应的输出电压标称值(nominal voltage)。I0是只使用一个基本电容单元C0时对应的基本输出电流,SCVR每个拓扑对应的电容总值为Ctot,是C0的整数倍,排列方式如2.2所述。根据负载电流需求Iload与基本电流I0的倍数关系,可以计算出应该使用的基本电容C0的个数n。实际电路根据计算值可以为开关电容拓扑配置相应数目的电容。

3 实验及分析

由于流片成本高昂,片上网络在实际中难以验证,本文采用HSPICE仿真平台进行电路模块的验证。实验对SCVR的基本参数配置如表2和表3所示,各种拓扑转换比所对应的标称电压值与拓扑相关参数如表4所示。

表2 SCVR基本电路参数配置

表3 其他参数配置

表4 拓扑相关参数(电压单位-V)

此外,晶体管模型使用PTM 32nm工艺模型。

根据文献[12]与系统理论分析,本文采用负载实际获得的平均功耗占从电源所获取的总平均功耗来表示供电效率,即

所有电流电压均为仿真测得,总功率中忽略了时钟控制单元的较少功耗,仅考虑SCVR拓扑开关单元本身的功耗。

为验证电容调制对提高效率的有效性,本文分别探讨在负载低功耗需求时和高功耗需求时两种情况,以求兼顾。由于不同种拓扑转换比率下,电路原理相同,因而仅需验证一种拓扑结构下的情况即可,本文选择验证2:1情况;另外本文中SCVR在验证中未采用多片并联交错(multiphase interleave)技术,因而电压纹波结果稍大,但并不影响验证基本电路单元的功耗与转换电容之间的关系。为抵消对纹波的影响,输出端采用了1 000 pF的去耦电容以稳定输出电压。

表1 电容调制算法

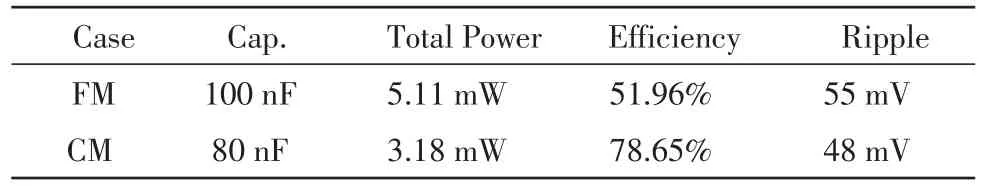

3.1 低负载功耗情况

由于实际处理器内核作为负载时,特性与电流源相近,因而本实验中将SCVR的内核负载用电流源来近似模拟。低负载功耗时的电压电流需求设置为Vload=0.6 V,Iload=4 mA。根据电容调制算法(Capacitance Modulation,CM),可以得到应该选取的电容值,与固定(Fixed Capacitance,FM)情况下做对比实验,仿真得到的输出电压波形如图4。其中,方波为200 MHz时钟信号;第二栏为FM情况下输出电压波形;最上面一栏为CM情况下输出电压波形。

图4 SPICE Explorer仿真波形

根据HSPICE报告的功率结果,做如表5对比。

表5 低负载情况下结果对比

通过对比实验结果可以发现,电容调制情况下的效率相比固定容值情况,提升可达26.69%,FM情况下的总功耗更多。分析原因是转换电容的值与SCVR输出电阻相关,因而会影响输出电压的值。固定电容时,SCVR的输出电压只能在较低精度下进行调节,如图仿真波形所示,高出所需电压造成能量浪费。

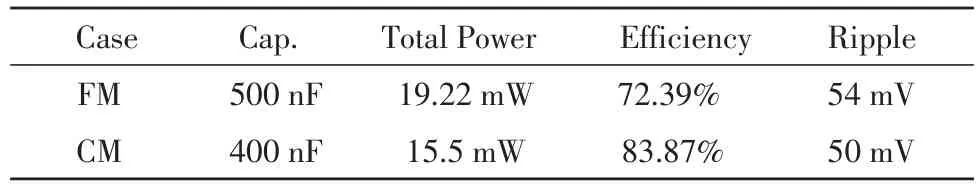

3.2 高负载功耗情况

低负载功耗时的电压电流需求设置为Vload=0.6 V,Iload=25 mA。与固定情况下做对比实验,两者均选择2:1比率下的拓扑,实验结果如表6所示。

仿真结果显示,在高负载情况下,效率提升有12%。因为在设计阶段,如固定电容,FM情况只能取最大允许情况下的电容值,以保证能满足处理器的极端需求,所以为了正确性而牺牲了效率。而CM情况则可以按需分配,在满足负载需求的情况下减少从电源获取的总功耗。

表6 高负载情况下结果对比

4 结论

文中提出了基于SCVR的电容调制方法,经过实验验证,能有效提高原转换器的供电效率达12%~27%,并能保证输出电压纹波被控制在50 mV及以下。今后研究中可考虑将调制方法扩展到多种拓扑结构,并设计相应的电容调制控制逻辑电路,实现更完整的系统设计。

参考文献:

[1]Inna Vaisband,Eby G.Friedman.Heterogeneous methodology for energy efficient distribution of onchip power supplies[J].IEEE Transactions on Power Electronics,2013,28(9):4267-4280.

[2]Inna Vaisband,Eby G.Friedman.Energy efficient adaptive clustering of on-chip power delivery systems[J].Integration,the VLSI Journal,2015(48):1-9.

[3]Toke M.Andersen,et al.A 10W on-chip switched capacitor voltage regulator with feedforward regulation capability for granular microprocessor power delivery[J].IEEE Transactions on Power Electronics,2017,32(1):378-393.

[4]Stephen T.Kim,Yi-chuns,Kazumdar,et al.Enabling wide autonomous DVFS in a 22nm graphics execution core using a digitally controlled fully integrated voltage regulator[J].IEEE Journal of Solid-State Circuits,2016,51(1):18-30.

[5]Xiaoyang Mi,et al.Fully-integrated switched-capacitor voltage regulator with on-chip currentsensing and workload optimization in 32nm SOI CMOS[C]//IEEE.IEEE/ACM International Symposium on Low Power Electronics and Design,2015:140-145.

[6]MoatazAbdelfattah,etal.Afullyintegratedswitched capacitor voltage regulator for near-threshold applications[C]//IEEE.IEEE International SymposiumonCircuitsandSystems,2015:201-204.

[7]Thomas Souvignet,et al.Sampled-data modeling of switched-capacitor voltage regulator with frequency-modulation control[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2015,62(4):957-966.

[8]Rinkle Jain,et al.A 0.45-1V fully-integrated distributed switched capacitor DC-DC converter with high density MIM capacitor in 22nm tri-gate CMOS[J].IEEE Journal of Solid-State Circuits,2014,49(4):917-927.

[9]T.M.Andersen et al.A sub-ns response on-chip switched-capacitor DC-DC voltage regulator delivering 3.7 W/mm at 90%efficiency using deeptrench capacitors in 32 nm SOI CMOS[C]//IEEE.IEEE Int.Solid-State Circuits Conf.(ISSCC)Dig.Tech.Papers,2014:90-91.

[10]Jarno Salomaa,et al.A switched-capacitor voltage regulator for ultra-low power energy harvesting systems[C]//IEEE.IEEE 57th International Midwest Symposium on Circuits and Systems,2014:45-48.

[11]Inna Vaisband,Mahmoud S.,Boris M.A closedloop reconfigurable switched-capacitor DC-DC converter for sub-mW energy harvesting applications[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2015,62(2):385-394.

[12]PingqiangZ.,etal.Distributedon-chipswitched-capacitorDC-DCconverterssupportingDVFSinmulticore systems[J].TVLSI,2014,22(9):1954-1967.

[13]Zhiyu Zeng,Suming Lai,and Peng Li.IC power delivery:voltage regulation and conversion,system-level cooptimization and technology implications[J].ACM Transactions on Design Automation of Electronic Systems,2013,18(2):29:1-29:21.

[14]Qing K.ZHU.Power distribution network design for VLSI[M].Hoboken,New Jersey:John Wiley&Sons,Inc.,2004.

[15]R.Jain,B.Geuskens.A 0.45-1V fully integrated reconfigurable switched capacitor step-down DCDC converter with high density MIM capacitor in 22 nm tri-gate CMOS[C]//IEEE.Proc.IEEE Int.Symp.VLSI Circuits.2013:174-175.

[16]Yogesh K.Ramadass.A fully integrated switched capacitor step-down DC-DC converter with digital capacitance modulation in 45nm CMOS[J].IEEE Journal of Solid-State Circuits,2010,45(12):2557-2565.

[17]Mahesh Zanwar,Subhajit Sen.Switch selection&sizing in CMOS implementation of variable output switched capacitor step-down DC-DC converter[C]//IEEE.IEEE International Conference on Electronics,Circuits,and Systems,2015:412-415.