某型号测温模块电路输入引脚漏电流超差失效分析

2018-05-09王笑怡

肖 薇,王笑怡

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

为不断适应新时期武器装备质量建设的新要求,更好落实装备质量提升工程,各单位相继开展了质量问题整改工作[1]。失效分析定位作为质量问题整改的第一步,显得尤为重要,在提高产品质量、技术开发、改进等方面有很强的实际意义[2-3]。

2 失效模式

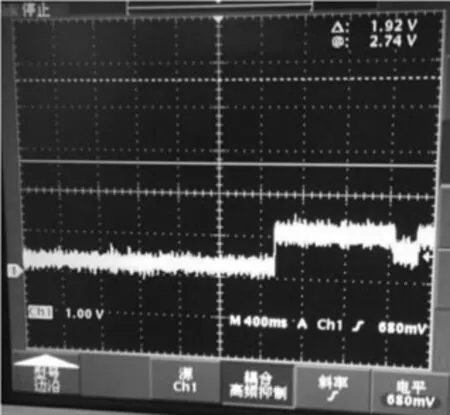

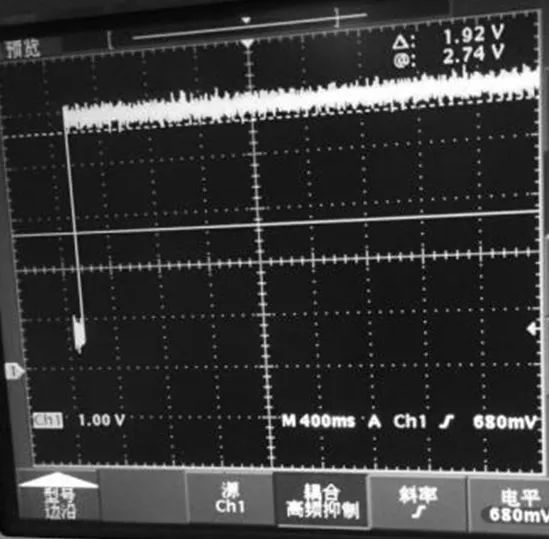

某型号测温器模块电路(以下简称模块电路)在使用过程中发现其温度修正常数读取异常,后经测量发现故障电路A1、A5引脚输入高电平为1.2V,如图1所示;正常电路输入的高电平为4.8V,如图2所示。由于故障电路A1、A5引脚输入为高时被电路拉低,造成电路温度修正常数读取时逻辑异常。

在对该模块电路进行静态电阻测量时发现,A1、A5引脚对VDD1上拉电阻值为0.615kΩ(正常电阻为1kΩ),不满足上拉电阻精度±10%的要求。对故障模块电路进行高电平漏电流IIH测试,A1、A5引脚漏电流分别为23mA和33mA,远远大于数字电路输入引脚漏电流≤500μA的标准。

图1 故障电路A1、A5引脚输入波形图

图2 正常电路引脚输入波形图

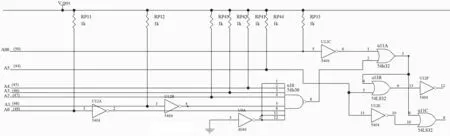

图3 模块电路温度修正常数读取部分电路原理图

3 故障定位

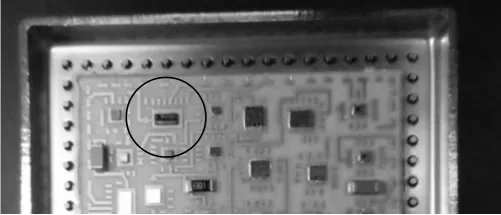

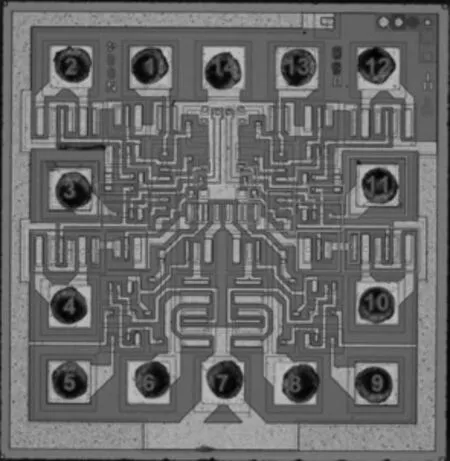

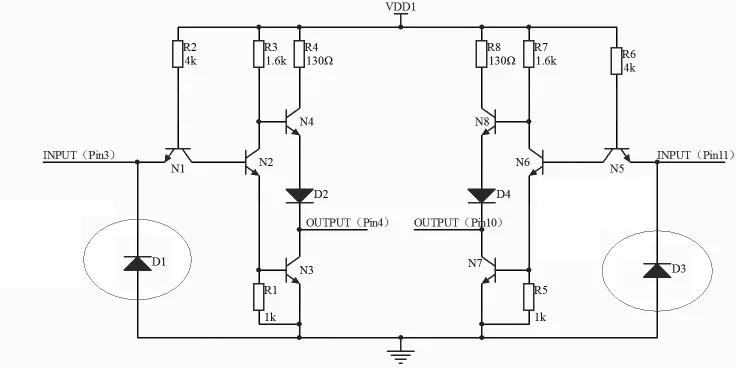

A1、A5引脚是模块电路地址输入引脚,经由内部1k电阻上拉至电源VDD1,同时经5404(U12),54LS32(U11)内部逻辑组合后产生控制信号,用于控制温度修正常数读取操作。该部分电路原理图如图3所示,模块电路产品如图4所示。

图4 故障电路温度修正常数部分产品图

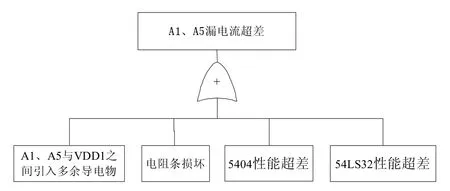

对“A1、A5输入漏电流超差”故障现象建立故障树,采用排除法进行故障定位[4]。故障树如图5。

图5 “A1、A5输入漏电流超差”故障树

按照图5的故障树,对各部分进行排查,过程如下:

(1)对“A1、A5与VDD1之间引入多余导电物”进行排查。

若A1、A5与VDD1之间存在多余导电物,且呈电阻特性,可能会导致A1、A5上拉电阻值变小的故障现象。对故障电路进行了PIND试验,结果为合格。故排除此分支。

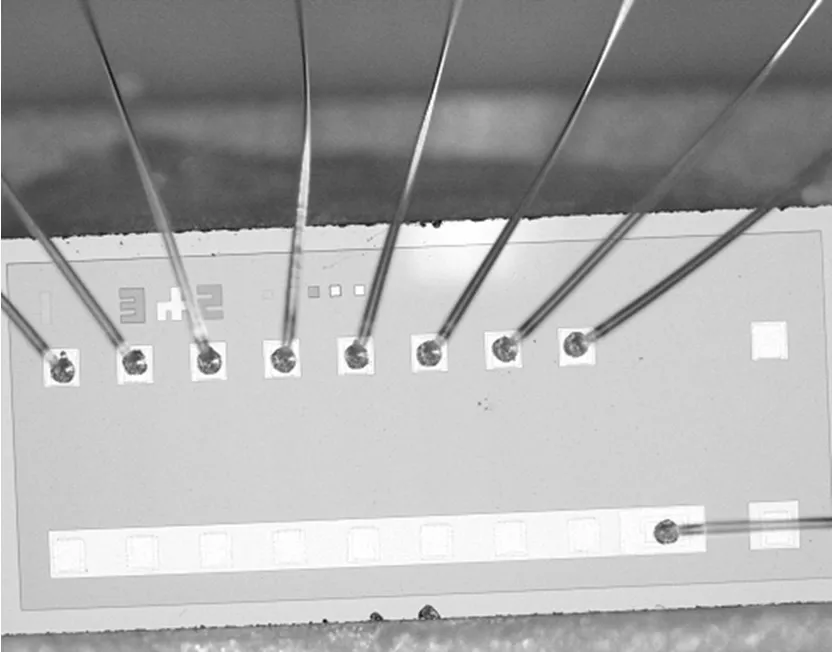

(2)对“电阻条损坏”进行排查。

对1k电阻条显微镜下目检,没有发现异常,如图6所示。故排除此分支。

图6 1k电阻条显微镜下镜检照片

(3)对“5404(U12)性能超差”进行排查。

5404输入对电源和地均有反相保护二极管,因此可以通过测量此反相二极管来判断5404(U12)是否性能超差。A1、A5引脚所对应的 5404(U12B)、5404(U12E)输入对地保护二极管测量结果分别为0.359V和0.29V。正常电路测量结果为0.65V和0.55V。

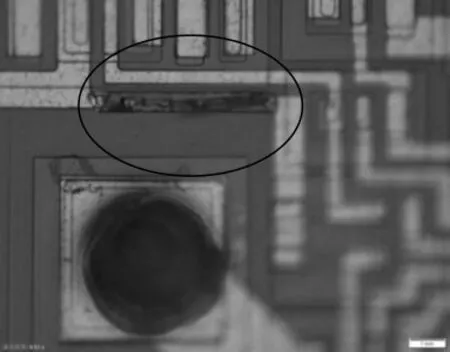

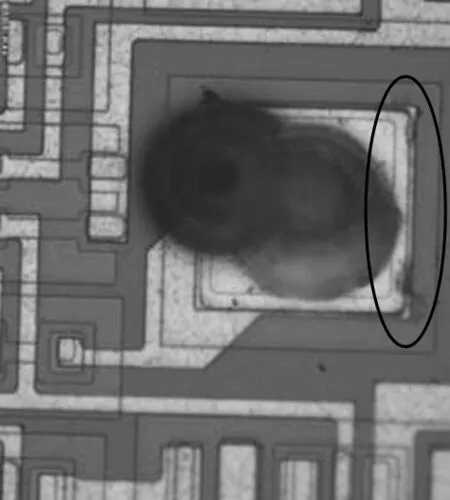

对5404(U12)进行目检过程中发现,该芯片3脚附近一根铝条烧黑,3脚(对应模块电路A1引脚)、11脚(对应模块电路A5引脚)周围有烧伤痕迹,现象如图7、图8和图9所示。怀疑此分支为模块电路故障的主要原因[5-6]。

图7 5404全貌

图8 3脚烧黑部位形貌图

图9 11脚烧黑部位形貌

(4)对“54LS32(U11)性能超差”进行排查。

对54LS32在显微镜下目检,没有发现异常,如图10所示。故初步排除此分支。

图10 54LS32显微镜下镜检照片

对模块电路内部进行目检,其余芯片无划伤、破损、烧毁等异常现象;基板无碎裂、污染等异常现象;键合丝无断裂、弯曲等异常现象,符合工艺规范要求。通过以上排查,推断“A1、A5输入漏电流超差”的故障现象是由于5404(U12)性能超差所致。

4 机理分析

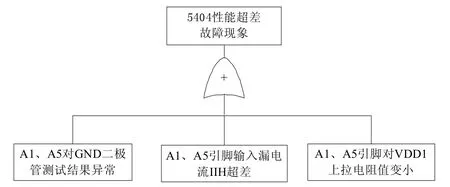

对5404性能超差的故障现象建立故障树并展开机理分析,证明5404损坏是导致模块电路“A1、A5引脚二极管异常,漏电流超差、上拉电阻阻值变小”的主要原因。故障树如图11所示。

图11 5404性能超差故障现象故障树

(1)对“A1、A5对GND二极管测试结果异常”这一分支进行分析。

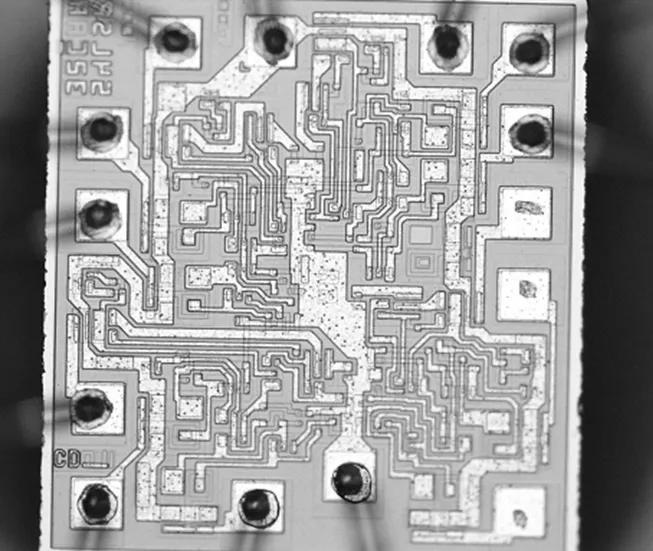

性能超差5404裸芯片图如图12所示,故障区域电路原理图如图13所示,画圈区域为图8、图9中芯片表面可见明显烧毁的部位。

图12 性能超差5404裸芯片图

图13 故障区域电路原理图

经分析,烧黑此区域为输入引脚A1(3脚)、A5(11脚)对GND的二极管D1、D3,因此外部测量二极管特性时,D1、D3性能超差导致A1、A5二极管测试结果异常。

(2)对“A1、A5引脚输入漏电流IIH超差”这一分支进行分析。

由分支(2)可知,A1、A5引脚对GND二极管性能超差,即A1、A5引脚对GND二极管存在反向漏电流,因此在进行输入漏电流IIH测试时,会出现漏电流超差的故障现象。

(3)对“A1、A5引脚对VDD1上拉电阻值变小”这一分支进行分析。

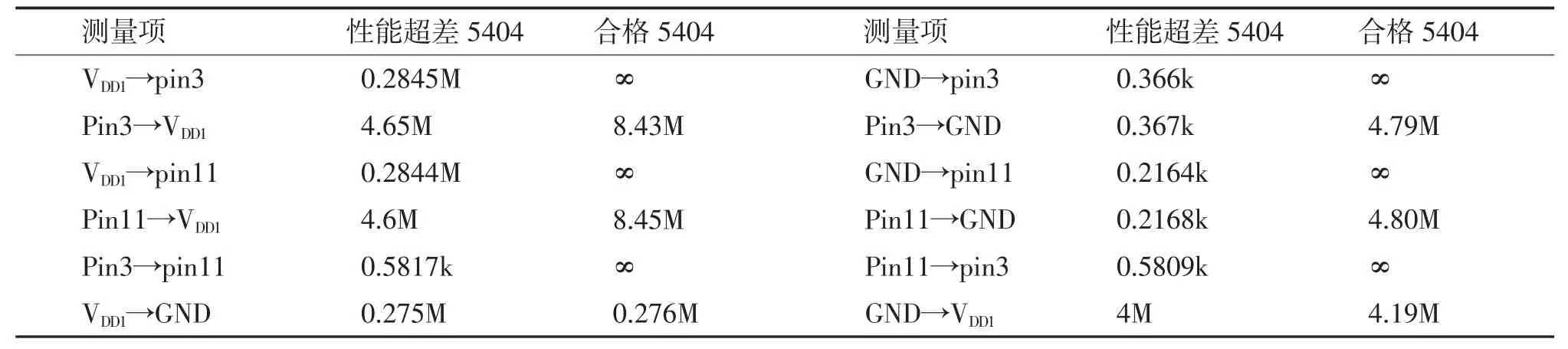

将性能超差5404裸芯片取下单独封装,与合格5404 的 Pin3(A1)与 Pin11(A5)引脚各个关键电阻值进行对比,如表1所示。

表1 5404各个引脚对VDD1、GND电阻值

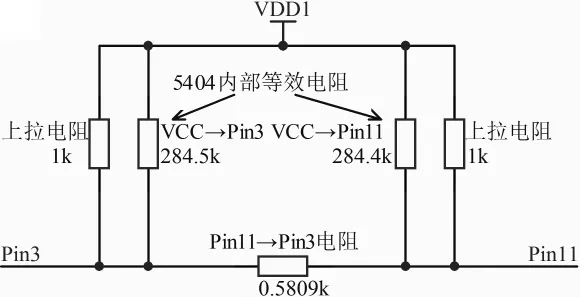

由表中可以看出,性能超差的5404电路Pin3(A1)与 Pin11(A5)脚之间存在通路,阻值为 0.58k,因此在测量模块电路外部VDD1与Pin3(A1)上拉电阻时,电流从VDD1经由Pin11到Pin3与VDD1到Pin3的电阻并联,如图14所示:

图14 性能超差5404内部等效电阻图

公式及计算结果如下:

与模块电路外部上拉电阻阻值测试结果0.61kΩ 相符。同理进行 VDD1→Pin11(A5),Pin3(A1)→VDD1与 Pin11(A5)→VDD1计算,结果均与实际测量值相符。

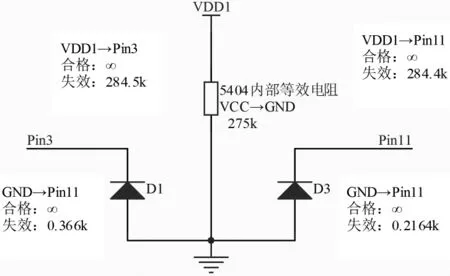

同时,由(1)(2)两分支表明,Pin3(A1)与 Pin11(A5)的D1、D3两个二极管性能超差,且对GND之间存在漏电流。在进行GND→Pin3(GND→Pin11)电阻测试时,合格5404测量结果为∞,而性能超差的5404测量结果为0.366kΩ(0.2164kΩ)。而表1中VDD1→pin3电阻变小是由于5404芯片VDD1→GND之间存在约275kΩ的电阻特性,在进行VDD1→Pin3电阻测试时,性能超差的5404中此电阻等效于经由VDD1→GND(275kΩ)再流经D1二极管到Pin3输出,理论值为275kΩ+0.366kΩ=275.366kΩ与实际测量结果284.5kΩ相近。如图15所示。

图15 5404内部等效电阻图

因此5404内部D1、D3二极管性能超差是导致模块电路“A1、A5引脚二极管异常,漏电流超差、上拉电阻阻值变小”的主要原因。

5 故障复现

将故障模块电路中性能超差的5404取下,更换新提取的5404芯片进行高电平漏电流IIH和上拉电阻测试,测试结果合格。故障现象消失。

将性能超差的5404封装在合格的模块电路中进行测试,A1、A5引脚漏电流分别为23.2mA和33.1mA。对A1、A5引脚对VDD1上拉电阻值进行测量,测量结果为0.613kΩ,与故障电路测量结果一致,故障现象复现。因此,确定“5404(U12)性能超差”是产生“A1、A5输入漏电流超差”的原因,进一步验证了“故障定位和机理分析”中的推断。

6 纠正与预防措施

6.1 模块电路设计方面

在进行数字电路设计时,输入引脚通常会采用电阻接高电平或者接地的方法,使输入端悬空时有确定的状态,减弱外部信号对芯片产生的干扰。此模块电路数字部分设计时通过1kΩ上拉电阻接VDD1对输入端进行保护,如图3所示。而模块电路输入保护二极管是由5404芯片内部实现的。由于该裸芯片尺寸较小,其二极管耐压值也较小。当输入瞬间高压尖峰超过5404内部保护二极管耐压值时,该二极管击穿进而导致5404性能超差,造成模块电路输入级功能不正常。在这部分模块电路设计时,可将输入引脚外接一耐压值较大的保护二极管,以抑制尖峰电压从而保护模块电路性能。

6.2 使用环境方面

通过对失效模块电路使用环境进行审查,该模块电路实际使用时,由于供电总线上电顺序不同,存在信号线带电插拔问题。同时输入地址总线信号与模块电路不共地,易产生电位差,因此在A1、A5信号输入及掉电时,可能会产生瞬时负电压,造成模块内部5404(U12)输入引脚对地二极管正向导通,大电流将D1、D3二极管烧毁,在引脚附近留下过流烧毁痕迹[7-8]。

因此在实际使用端增加保护措施,将输入信号地与模块电路地共地。同时在软件方面进行掉电顺序修改,确保模块电路总电源先上电,后进行信号线高低电平输入。同时结束使用时,信号线即模块电路输入引脚先于模块电路电源掉电,确保使用安全。

7 结束语

通过对某模块电路“A1、A5引脚漏电流超差”的故障现象进行故障定位及机理分析,确定该模块电路失效是由于其内部5404(U12)D1、D3二极管性能超差所致,并通过交叉试验的方式使得故障现象复现,同时在模块电路设计和使用环境方面提出了整改措施。此失效分析可作为理论基础,为此类含有输入保护二极管的模块电路设计及使用提供参考。

参考文献:

[1]孙家坤.军用集成电路失效分析[J].电子测试,2017,(06):46-47 54.SUN Jiakun.Failure analysis of military integrated circuit[J].Electronic test,2017,(06):46-47 54.

[2]王自力.分析电子元器件质量及其可靠性管理 [J].通讯世界,2016(21):216-217.WANG Zili.Analysis of the quality and reliability management of electronic components[J].Communication word,2016(21):216-217.

[3]王德权.浅析电子元器件的失效分析技术 [J].科技与企业,2013(7):308.WANG Dequan.Analysis of failure analysis technology of electronic components[J].Science and technology and enterprises,2013(07):308.

[4]王创国,贾洁,周舟,等.EMMI故障定位和基于故障树的GaAs MMIC失效分析 [J].固体电子学研究与进展,2017(5):333-338.WANG Chuangguo,JIA Jie,ZHOU Zhou,et al.EMMI fault location and GaAs MMIC failure analysis based on fault tree[J].Progress of solid state electronics,2017,37(05):333-338.

[5]谢凯翔.SRAM失效分析 [J].中国集成电路,2017,26(10):70-73.XIE Kaixiang.SRAM failure analysis[J].Chinese integrated circuit,2017,26(10):70-73.

[6]席善斌,裴选,刘玮,等.多模计数器静电放电损伤的失效分析[J].半导体技术,2017(10):784-789.XI Shanbin,PEI Xuan,LIU Wei.et al.Failure analysis of electrostatic discharge damage of multimode counter[J].Semiconductor technology,2017,42(10):784-789.

[7]王媛,白璐,詹勇,等.某A/D转换器老化过程中端口异常失效分析[J].环境技术,2017,35(04):39-43 48.WANG Yuan,BAI Lu,ZHAN Yong,et al.Analysis of abnormal port failure in the aging process of a AD converter[J].Environment Technology,2017,35(04):39-43 48.

[8]马香柏.CMOS电路中的漏电失效分析 [J].集成电路应用,2017,34(4):53-57.MA Xiangbai.Analysis on leakage current failure in CMOS circuit[J].Iapplication,2017,34(04):53-57.