基于Verilog-A的流水线型ADC数字校正技术仿真平台

2018-05-09宫月红张少君王明雨刘冰冰

宫月红,张少君,罗 敏,王明雨,刘冰冰

(1.山东交通学院船舶与轮机工程学院,威海264209;2.哈尔滨工业大学(威海)微电子中心,威海 264209)

1 引言

随着信息技术的进一步发展,微电子芯片集成度不断提高,芯片尺寸越来越小。工艺尺寸的缩小意味着特征线宽不断降低。在这一背景下:一方面,器件速度进一步提高,功耗进一步降低;另一方面,晶体管本征增益降低,工作电源电压降低。此时,数字电路的速度更快,功耗更低,所以数字电路会持续受益;而对于模拟电路来说,电源电压、本征增益的降低意味着高增益的放大器设计越来越困难。所以,工艺的演进对于模拟电路来说是一种挑战。在很多的应用场合,模拟电路趋向于用更多的数字电路来代替。模数转换器(ADC)作为将模拟信号转换为数字信号的装置,起着连接模拟世界与数字世界桥梁的作用。模拟电路可能会消失,但是模数转换器永远不会消失。这样一来,模数转换器成为了限制数字信号处理技术发展的瓶颈,因此,进一步提高模数转换器性能的显得更加重要。

为了在深亚微米条件下降低模拟电路的设计难度,同时保持较低的功耗,采用数字辅助技术增强模拟电路性能成为一种必然选择。当前流行的应用于ADC的数字增强技术大体可分为两大类。第一类是基于统计的数字校正技术[1]。这种校正技术一般需要在信号传输通路中注入伪随机码,利用伪随机码出现“0”和“1”概率相同的特性来估计非线性误差,对后级数据进行补偿。这类校正技术校正算法的收敛要依赖统计规律,收敛时间较长。第二类是确定性的校正技术,这类校正技术算法收敛不依赖统计规律,收敛时间较短。按照收敛的方式的不同,这一类校正技术又有两种。第一种通过加入测试信号来建立传输函数模型,实现对后台转化数据进行传输函数建模[2]。由于测试信号的加入会打断正常的转换流程,所以转换速度会受到一定的影响。第二种在主ADC外专门设计一个参考ADC[3],通过参考ADC与主ADC转换结果的差别来建立传输函数模型。这种校正技术不会打断正常的模数转换流程,收敛速度也比较快,但是参考ADC的存在会增加额外的模拟电路开销,并且电路设计也比较复杂。在实际应用中,需要结合不同的应用场合,选用不同的数字校正技术。

为了对数字增强技术进行研究,确保设计的正确性及适用性,需要对校正技术进行多种层次的验证。其中,在芯片电路设计之前,需要对系统的模块和参数建立模型,并进行仿真、模拟,以验证方案的可行性及选择合适的参数。这就需要对系统中的各种非理想因素、电路中各个模块工作细节以及校正算法进行模拟并仿真,此时建立高层次行为级仿真平台就变得非常重要[4]。

因此,采用Verilog-A硬件描述语言搭建了一个流水线型ADC数字校正技术仿真平台。该平台采用Verilog-A来描述流水线型ADC模拟部分电路模块,同时采用Verilog来描述数字校正算法。Verilog-A作为一种应用于模拟电路以及混合信号电路仿真的标准化模型语言,既可以对模拟电路中各个模块的功能及连接关系进行结构描述,又可以对电路中各种器件(小至电阻、电容、电感等基本器件,大到滤波器,锁相环等模拟模块)进行行为描述。并且,Verilog-A语言无缝集成在Cadence的集成电路设计环境Design Framework II(DFII)中,可直接应用于Spectre电路仿真器进行仿真[5]。

在DFII环境下,Verilog-A的默认库中包括了大量采用Verilog-A语言描述的各种硬件单元模型。这些模型中既包括像ADC这种大的完整功能模块,又包括像电阻、电容、晶体管这种底层元件。按照实际应用需要,设计者可以很方便地对库里的硬件单元模型进行修改,也可以自己创建全新的硬件模型。

在模拟部分和数字部分的建模分别完成之后,将两部分合并,采用Spectre-Verilog混合电路仿真器进行仿真。采用Verilog-A和Verilog语言建立行为级仿真平台,可以将高层次行为级建模、仿真与实际电路设计、仿真统一在同一个EDA(Electronic Design Automation)设计平台下,从而为数字提高技术的研究奠定基础。

2 误差建模

在流水线型ADC信号传输通路中,由于各种非理想因素的存在(比如子ADC中的比较器失调等),造成了ADC的转换结果不理想。为了对数字校正技术进行研究,需要对这些非理想因素进行准确的模拟。在建立的仿真平台中,采用Verilog-A语言对这些非理想因素进行建模,并结合校正算法进行仿真验证。

在诸多非理想因素中,失调误差的建模可以通过向参考电平中引入偏移量来实现;流水线型ADC数字校正技术主要对流水线型ADC中非线性误差进行校正,此时,就需要对流水线型ADC系统中的非线性误差进行建模。一般来说,线性或非线性通信系统的输入输出关系都可以用Volterra级数来表示。采用Volterra级数对传输函数进行描述,既适用于时不变系统,又适用于时变系统[6-7]。式(1)给出了一般通信系统的连续时间传输函数表达式:

式中,x(t)和y(t)分别表示通信系统的输入和输出,yk(x(t))的具体表达式如式(2)所示:

在有些场合下,不需要考虑模拟电路中的时变因素。以级间余量放大器为例,式(1)中的时变因素对应放大器的记忆效应。一般情况下,对数字校正技术的研究只考虑了放大器不带有记忆效应的情况,所以可以对输入输出特性进行简化,此时的输入输出关系可以用泰勒级数来表示。将泰勒级数表达式进行化简,可以得到多项式形式的放大器传输函数表达式如式(3)所示:

此表达式中只考虑了放大器的增益非线性误差,而没有考虑增益误差,增益误差可以用失调误差的形式表示。

在建立的仿真平台中,通过给相应模块的传输函数表达式人为引入非理想因素来实现对非线性误差的模拟。以建立的仿真平台中采用的开环结构的级间余量放大器为例。对于开环放大器非理想因素的模拟通过在放大器模型中加入非线性误差来实现。在该模型中,用三次多项式来对放大器的传输函数进行近似,可以加入一阶误差、三阶误差或者同时引入两种误差来对放大器的非线性误差进行建模。图1给出了加入误差前后的放大器传输函数曲线。

图1 加入误差前后开环放大器传输函数曲线

3 校正算法建模

对于同一种模拟电路,可以采用不同的数字校正算法进行误差校正。在建立的行为级仿真平台中,采用Verilog语言对数字校正算法进行描述。在这一部分,数字校正部分被做成一个功能模块,如果采用不同的数字校正技术进行校正,则只需要对校正算法部分进行修改,也就是直接对算法模块进行修改即可。

图2中给出了一种确定性校正技术的原理框图[2,8]。该校正技术通过对级间运算放大器的非线性误差进行校正来提高ADC的转换精度。为了降低流水线型ADC的系统功耗,采用开环放大器作为级间余量放大器来代替传统的闭环放大结构,并且选用最接近实际传输函数的三次多项式来对开环放大器的传输函数进行近似,提高校正精度。在校正过程中,通过加入测试信号的方式,建立第一级级间放大器传输函数模型,通过该模型结合后级的输出码值来估计理想的运算放大器输入码值。

图2 一种应用确定性校正算法的校正系统结构图

4 系统仿真平台

采用Verilog-A语言结合Verilog语言,搭建了一个12位流水线型ADC数字增强技术仿真平台。整个仿真平台大体由以下几部分构成。

4.1 主ADC模块

图3给出了12位流水线型ADC主体结构图。该ADC整体有效位数为12位,由10个1.5位/级输出的子级,以及最后的一个2位/级输出子级组合而成。除最后一级外,每个子级都是由子ADC和MDAC构成,最后一级仅由子ADC构成。各子级的数字输出码经过时钟对齐后送入全加器阵列进行错位相加得到最终输出码。

图3 主ADC流水线型模型

4.2 子ADC模块

图3的主ADC模块中包括10级子级,子级中包括子ADC和MDAC、减法电路和级间余量放大器等。其中子ADC包括两个比较器,比较器的比较电平分别为±1/4Vref。用Verilog-A语言将单个子级描述为一个模块,并通过文本编辑的方式直接修改各项参数。

4.3 数字校正模块

对于相同的模拟电路结构,可以设计不同的数字校正技术来对误差进行校正。在芯片设计开发阶段,为了节约成本,可以把数字校正部分放在芯片外,通过片外处理器来实现数字部分的功能,或者将数字校正算法写在FPGA中来对数字校正技术进行验证。这一做法在系统建阶段也可以灵活应用。在该阶段,校正算法部分可以通过Verilog语言描述来完成。在这一部分,数字校正部分被做成一个功能模块,不同的校正算法对应不同的Verilog代码,当校正算法需要修改时,直接修改校正算法模块即可。

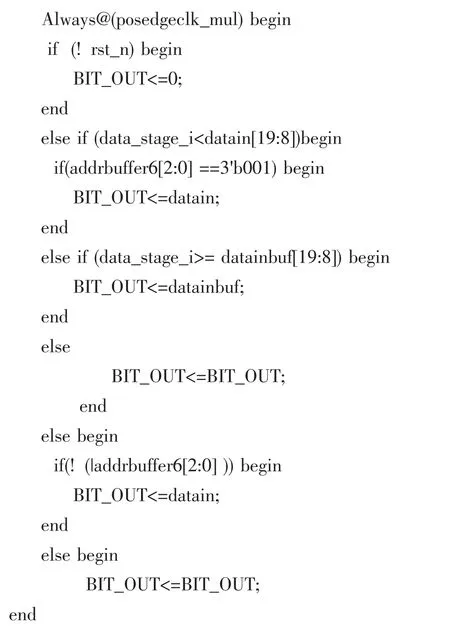

下面给出了一种确定性的数字校正技术校正算法模块对应的部分Verilog代码:

5 系统仿真结果

由于Verilog-A语言可以无缝集成在集成电路设计环境中,所以使用建立的仿真平台不但可以对流水线型ADC的结构和模数转换功能进行模拟,还可以分别对应用校正算法前后ADC的静态特性(积分非线性INL、差分非线性DNL)和动态特性(无杂散动态范围SFDR、信噪失真比SNDR等)进行测量,并可以计算得到其有效位数ENOB等参数。

下面给出了用于测量INL的功能模块的部分Verilog-A代码:

图4给出了给主ADC加40 MHz采样时钟,9 MHz正弦输入信号时的输入输出波形图。

图4 ADC输入输出仿真波形

6 结束语

在工艺线宽进一步缩小的背景下,采用数字提高技术来增强数模混合电路系统的性能已成为一种必然趋势。文中提出的基于Verilog-A的流水线型ADC数字提高技术仿真平台能够对流水线型ADC进行系统建模,并能够对流水线型ADC中非理想因素进行精确模拟,同时可以结合采用Verilog语言描述的数字校正算法模块进行数模混合仿真,为数字校正技术的研究提供了一种高效、便捷的途径。在流水线型ADC的研究中应用此平台,可以缩短数字校正技术研究时间,并且提高设计灵活性,从而大大缩短芯片开发周期,降低开发成本。这一点在高性能、低功耗流水线型ADC的研究中具有非常重要的意义,从而可以对信息产业的发展起到重要的促进作用。

[1]MURMANN B,BOSER B E.A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification[J].IEEE J.of Solid-State Circuits,2003,38(12):2040-2050.

[2]KIM K R,MURMANN B.A 12-b,30-MS/s,2.95-mW pipelined ADC using single-stage class-AB amplifiers and deterministic background calibration[J].IEEE Journal of Solid-State Circuits,2012,47(9):2141-2151.

[3]YUAN J,FUNG S W,CHAN K Y,et al.An Interpolation-Based Calibration Architecture for Pipeline ADC With Nonlinear Error[J].IEEE Transactions on Instrumentation&Measurement,2011,61(1):17-25.

[4]HSIEH M.Single chip high-speed serial link communicationsformulti-channel and multi-standard Applications[D].America:Doctoral Thesis,University of Minnesota,2008:8-93.

[5]周裕康.基于Verilog-A的LDMOS器件建模方法的研究[D].成都:电子科技大学,2015.ZHOUYukang.ResearchonLDMOSdevicemodelingmethod based on Verilog-A[D].Chengdu:University of Electronic Science and Technology of China,2015.

[6]DU T,YU C,GAO J,et al.A new accurate Volterra-based model for behavioral modeling and digital predistortion of RF power amplifiers[J].29,(2012),2012,29:205-218.

[7]LIMA E G,CUNHA T R,TEIXEIRA H M,et al.Basebandderived volterra series for power amplifier modeling[C]//Microwave Symposium Digest,2009.MTT'09.IEEE MTTS International.IEEE,2009:1361-1364.

[8]DAITO M,MATSUI H,UEDA M,et al.A 14-bit 20-MS/s pipelined ADC with digital distortion calibration[J].IEEE Journal of Solid-State Circuits,2006,41(11):2417-2423.