基于FPGA的千兆以太网接口应用研究与实现

2018-05-05吴长瑞徐建清蒋景红

吴长瑞 徐建清 蒋景红

摘 要: 为解决嵌入式领域中数据量大、速度高、实时性强等传输问题,提出FPGA和PHY芯片相结合的设计方案,用于实现UDP/IP协议。通过深入研究TCP/IP协议栈体系结构和工作原理,按照以太网的帧格式封包和解包,在FPGA中实现UDP/IP数据的正确发送和接收。在自主研发的硬件平台上验证了该方案的正确性和可靠性。由于使用FPGA实现UDP/IP协议,系统具有移植性高和易于集成等优点。

关键词: UDP/IP; 协议栈; 千兆以太网; 现场可编程门阵列; 帧格式; 系统集成

中图分类号: TN913?34 文献标识码: A 文章编号: 1004?373X(2018)09?0001?05

Abstract: In order to solve the transmission problems of large data amount, high speed and strong real?time performance of the embedded field, a design scheme combining FPGA and PHY chip is proposed to implement the UDP/IP protocol. The system architecture and working principle of TCP/IP protocol stack are studied deeply. According to the packed and unpacked frame format of Ethernet, the UDP/IP data is sent and received correctly in FPGA. The correctness and reliability of the scheme are verified on the autonomously?developed hardware platform. The system using FPGA to implement the UDP/IP protocol has the advantages of high portability and easy integration.

Keywords: UDP/IP; protocol stack; Gigabit Ethernet; FPGA; frame format; system integration

0 引 言

千兆以太网在视频和音频等大数据量和高实时性的领域存在广泛的应用。在点对点通信中,数据传输的实时性是通信双方非常关心的问题。针对此类应用,UDP(User Data Protocol)提供了一种高效、低延迟的称为数据报的传输协议,采用UDP这种面向非连接的传输协议,可以有效解决数据实时传输的问题。目前业界常用的嵌入式以太网解决方案有微控制器内移植TCP/IP协议栈和ASIC内置协议栈,上述方案都不能同时兼顾传输效率、可集成化和可移植性[1?2]。

本文提出一种基于FPGA的UDP/IP协议,实现千兆以太网传输方案兼顾传输效率、易于集成和便于移植等特点,该方案已在实际工程中得到广泛应用。

1 TCP/IP协议栈结构及工作原理

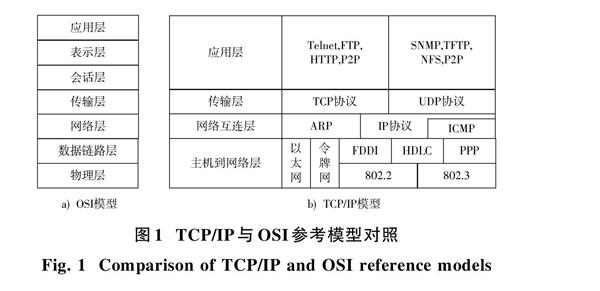

OSI参考模型(Open System Interconnection Reference Model)是国际互联网标准化组织提出的网络结构标准模型。该模型的目的是使各种硬件在相同的层次上相互通信。实际应用中,OSI模型因为实现太过复杂而很少被采用,TCP/IP模型因简洁而被广泛使用。TCP/IP协议栈并不是TCP和IP这两个协议的合称,而是指因特网整个TCP/IP协议族[3?5]。TCP/IP参考模型的分层结构与OSI模型的参照图如图1所示。

第一层:主机到网络层,主要包括物理层PHY和介质访问控制层MAC。TCP/IP参考模型中没有描述这一层的具体实现方式,只规定其为上一层提供IP数据包的接口,以太网是其中一种实现方式。

第二层:网络互连层,是TCP/IP协议栈的核心。该层定义了分组格式和协议类型,具有路由、网际互连和拥塞控制等。

第三层:传输层,包含传输控制协议(Transmission Control Protocol,TCP)以及用户数据报协议(User Datagram Protocol,UDP)两种协议。TCP协议是一种面向连接、可靠、基于字节流的传输协议。它利用IP层的机制,在不可靠的连接基础上实现可靠的连接,通过发送窗口控制、超时重发、分包等一系列方法,将字节流从一台主机发送到其他主机。UDP协议是一种无连接协议,是不可靠的,主要应用于不需要对数据报进行排序以及流量控制的场景。

第四层:应用层,它面向用户,可实现很多用户应用协议。

UDP协议是TCP/IP传输层协议的一部分。UDP是面向报文的传输协议,由于其只负责把报文发送出去,接收方也不会提供反馈机制,所以它是不可靠的。但正是因为UDP没有建立连接、撤销连接、确认报文等开销,因而相对于TCP协议,它的执行速度更快,实时性更强,具有很高的传输效率而且它对系统造成的负载低[6]。本文从具体的实际应用出发,系统传输层中采用UDP 传输协议提供点对点的数据报传输服务,网络层为IP协议,数据链路层为ARP协议和MAC协议,物理层采用自适应千兆网1000Base?T的连接通道。

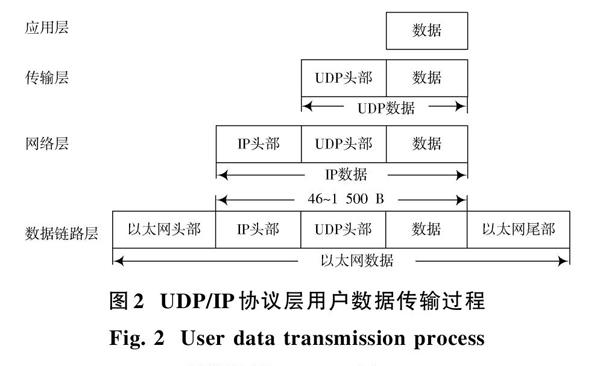

UDP/IP协议的工作原理可以看作是两个简单的处理过程:从上层到下层的封包过程和由下层至上层的解包过程,每个过程都是依照每层采用的传输协议传输数据。当通信主机向从机发送数据时,应用层的数据首先被送入协议栈中,然后逐层通过协议栈的每一层直至送到网络。每一层对收到的数据都要增加一些首部信息(有些还要增加尾部信息),整个过程称作是封包过程。当通信主机接收从机传过来的以太网数据帧时,帧数据就开始从协议栈的物理层开始传输,通过相应层时,检验是否匹配当前层的协议帧首部信息,如果不满足就丢弃该帧,这个过程称作解包。封包和解包过程如图2所示。

在实际传输应用过程中遵照协议透明的原理,在各自的层中按照标准封包和解包数据后交付下一层。精简后的协议栈具备以下功能:实现基于UDP传输协议的数据传输;按需求可以对目的IP地址和源IP地址进行灵活配置;支持ARP地址解析;支持checksum帧校验;支持数据流控制。

2 以太网的帧格式

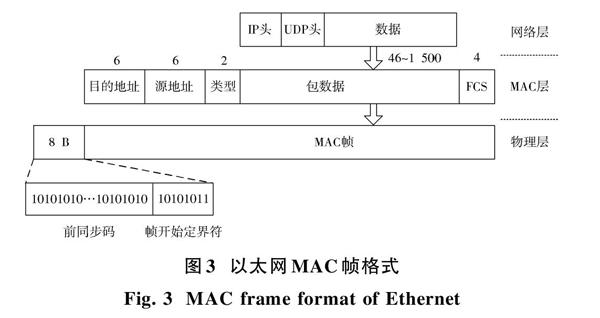

以太网帧包含6个域:前导码,8 B;目的地址,6 B;源地址,6 B;类型域,2 B;数据,46~1 500 B;帧校验序列FCS,4 B。前导码是MAC数据到物理层添加的,目的是实现比特同步。前7个字节是1和0交替的序列,称为前同步码,这种序列可以使接收端快速实现比特同步。最后一个字节是帧开始的定界符,规定为10101011,接收端在接收到该字节后,就知道后面的数据是MAC帧了。

以太网MAC层主要实现数据帧的构建与差错检查、传输控制、接口转换等功能。常用的以太网MAC帧格式有DIX Ethernet V2和IEEE 802.3两种。

图3给出了最常用的以太网MAC V2帧格式,共包含5个字段。开始的两个字段分别为6 B的目的地址和源地址,即通常所说的MAC地址或者物理地址,它们是固化在网卡中并且是唯一的。第3个字段是用来标记上层协议的类型字段,共2 B,根据该类型就可以把收到的MAC帧数据交给上一层的对应协议。如该类型字段的值是0x0800时,表示上层使用的是IP数据报。第4个字段是数据字段,长度在46~1 500 B之间。最后1个字段是4 B的帧检验序列FCS,作为整个数据包的校验字节[7?8]。

以太网协议规定的最短帧长为64 B,这就要求数据填充至少为46 B。当数据字段的长度小于46 B时,为了保证以太网的MAC帧长不小于64 B,MAC子层就会在数据字段的后面添加若干字节的填充字段[9]。

3 FPGA实现千兆以太网协议的硬件设计

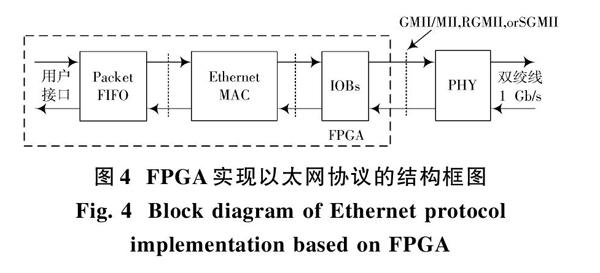

常见FPGA实现以太网协议的结构图如图4所示。利用Xilinx公司提供的MAC IP核和IOB以MII(Media Independent Interface),GMII,RGMII或者SGMII形式与PHY芯片连接,PHY芯片以1000Base?T 形式接到RJ45上。其中MII又称介质无关接口,收发各有4位数据线,工作在2.5 MHz或者25 MHz时钟下,理论传输速率为10 Mb/s或100 Mb/s。不能满足千兆以太网的要求,IEEE 208.3工作组又引入了GMII,即千兆介质无关接口,收发数据线各8位,收发时钟为125 MHz,理论速度为1 000 Mb/s。RGMII(Reduced MII)是简化的GMII接口。收发数据各有4位,与GMII相比,信号线减半,但收发时钟还是125 MHz,为了达到1 Gb/s,TXD和RXD信号线上在时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。

MII,GMII和RGMII使用FPGA的GPIO实现,SGMII 使用FPGA的MGT实现。本文给出两种实现方式的设计方案。

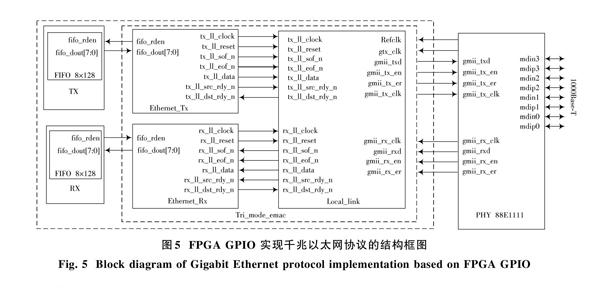

3.1 FPGA GPIO实现以太网协议

本节描述FPGA使用GPIO以GMII或RGMII接口的形式接入PHY 88E1111,通过PHY 88E1111转换为1000Base?T;这种情况下不占用MGT资源。

FPGA和PHY连接及PHY的配置设计成GMII或者RGMII是可以选择的。这样逻辑设计时可以灵活选择是生成RGMII接口的IP核还是生成GMII接口的IP核。无论是RGMII还是GMII接口,用户接口都是locallink形式。所以对于逻辑开发者来说都是一样的。FPGA GPIO实现千兆以及网协议的结构框图见图5。

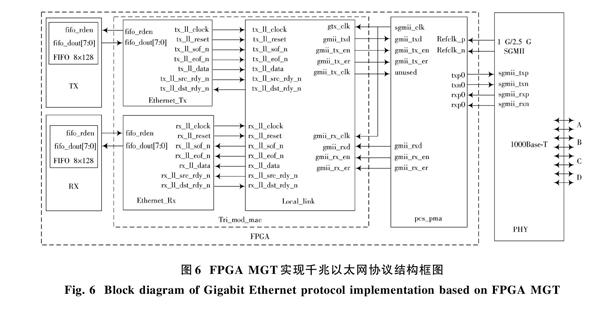

3.2 FPGA MGT实现以太网协议

在GPIO资源不足的情况下,还可以采用FPGA的MGT实现千兆以太網。图6给出FPGA MGT实现千兆以太网协议的结构框图。MGT连接的是SGMII信号形式。如果要通过SGMII实现1000Base?T就需要2个IP核级联,即Tri?mod?eth_mac和 Ethernet 1000Base?x PCS/PMA or SGMII 级联。其中,Tri?mod?eth?mac IP用户接口是Local link接口,另一端是GMII接口;而PCS/PMA or SGMII IP core一端是GMII接口和Tri?mod?eth?mac相连;另一端是使用FPGA的MGT实现的SGMII接口,SGMII通过PHY 88E1111转换成1000Base?T;由于PCS/PMA or SGMII core 支持1G和2.5G,故本设计以太网传输协议可以工作在1 Gb/s或者2.5 Gb/s两种速率下。PCS/PMA or SGMII core工作在SGMII模式下[10?12]。

4 UDP/IP协议逻辑实现

根据UDP/IP的工作原理和以太网MAC帧格式,设计发送和接收模块对数据进行封包和解包。图7给出了UDP/IP发送模块的封包状态跳转图。从状态转移图中idle状态跳转的三个分支可以看出,这个发送模块可以发送ARP包,UDP/IP数据包和用户自定义的包。这里着重介绍UDP/IP数据包的发送过程。状态 send_mac_ dstaddr_sof 是发送以太网MAC帧的起始状态,在send_mac_dst_addr状态发送6 B的MAC帧的目的地址,在send_mac_src_addr状态发送6 B的MAC帧的源地址。

send_mac_dst_addr状态发送协议类型,如果类型是0x0800就是IP包,用户还可以定义别的类型,如图7中0x5160发送自定义的数据包格式。

在IP數据包的发送中,按照IP头长度(send_ip_header_ length)、服务器类型(send_ip_server_type)、IP总长度(send_ip_total_length)、IP ID(send_ip_id),IP偏移地址(send_ip_fragandoffset)、生成周期(send_ip_ttl),IP协议(send_ip_protocol)、校验和(send_ip_headchecksum)、IP的源地址(send_ip_srcaddr)、IP目的地址(send_ip_dstaddr)等顺序跳转状态机。

最后跳入UDP的封包状态机,按照UDP的源端口号(send_udp_srcport)、UDP的目的端口号(send_ udp_dstport)、UDP长度(send_udp_dstport)、校验和(send_udp_checksum)、数据头(send_ack_data_head)和数据(send_ack_data)的顺序发送MAC数据帧。

本设计除了能发送UDP/IP数据包,同时还能传输用户自定义的数据包格式。接收模块按照同样的MAC数据帧格式接收数据包。这里不再给其状态机。

5 测试平台与结果分析

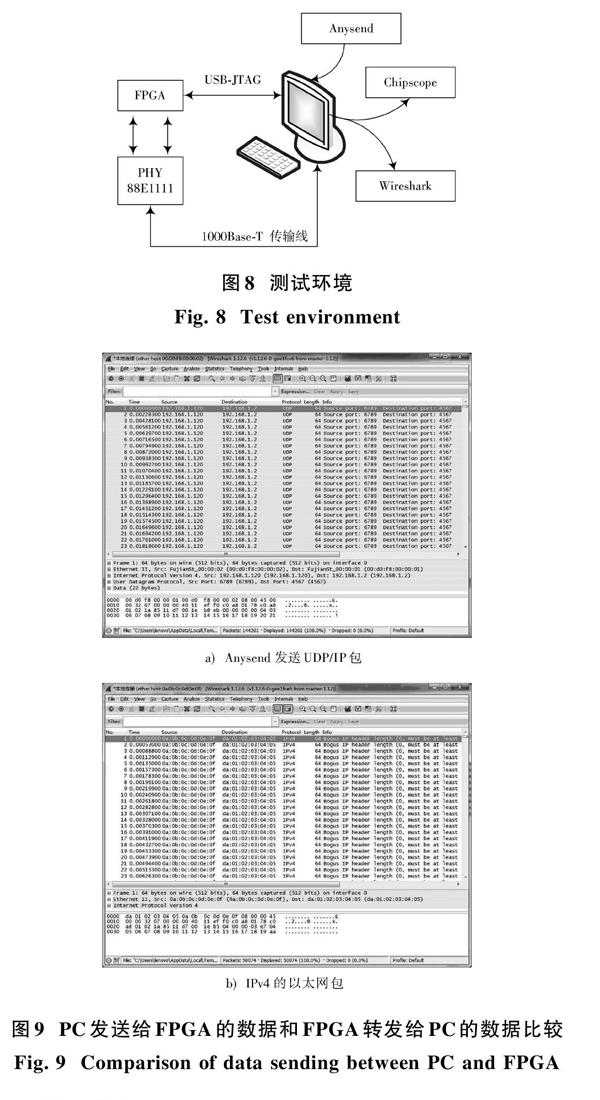

在自主研发的以SP6LX45T?CSG484 FPGA为主芯片的板卡上实现UDP/IP协议栈,外部配置物理层收发芯片88E1111,通过RJ45连接搭建千兆以太网传输通路。按照图8搭建测试环境进行系统测试。

通过网线将自研板卡与PC相连,在PC上使用Anysend软件发送UDP/IP包,在FPGA内部接收该UDP/IP包,然后通过FPGA转发给PC。使用Wireshark分别抓取PC发给FPGA的以太网数据和FPGA发送给PC的以太网数据如图9所示。图9a)所示为Anysend发送是标准UDP/IP包,该包被FPGA接收后重新定义了MAC的源地址和目的地址,然后发送给PC,所以图9b)是IPv4的以太网包。通过数据分析,本文设计的协议栈功能正确,逻辑端能够正确发送和接收以太网数据。并且通过长时间测试(大于24 h),平均丢包率为百万分之一的量级。

6 结 语

本文介绍了两种在FPGA实现UDP/IP协议栈的实现方法。无论是利用FPGA GPIO资源还是利用FPGA MGT资源实现千兆以太网通信,逻辑端的收发模块设计都是一样的。因此,这种方法可移植性高,实现简单,利于系统集成,在实时性要求比较高的点对点通信领域有着广泛的应用。

参考文献

[1] 崔鹤,刘云清,盛家进.基于FPGA的UDP/IP协议栈的研究与实现[J].长春理工大学学报(自然科学版),2014,37(2):133?137.

CUI He, LIU Yunqing, SHENG Jiajin. Research and implementation of UDP/IP protocol stack based on FPGA [J]. Journal of Changchun University of Science and Technology (natural science edition), 2014, 37(2): 133?137.

[2] 史鹏腾.基于千兆网的FPGA多通道数据采集系统设计[J].电子科技,2015,28(2):123?126.

SHI Pengteng. Design of multi?channel FPGA?based data acquisition system based on Gigabit Ethernet [J]. Electronic technology, 2015, 28(2): 123?126.

[3] 谢希仁.计算机网络[M].5版.北京:电子工业出版社,2005.

XIE Xiren. Computer network [M]. 5th ed. Beijing: Electronic Industry Press, 2005.

[4] 卡萨德·威尔斯. TCP/IP 24学时教程[M].王建华,译.北京:机械工业出版社,1999.

WALES J C. TCP/IP 24 hours tutorial [M]. WANG Jianhua, Translation. Beijing: Mechanical Industry Press, 1999.

[5] KOZIEROK C M.TCP/IP指南(卷一):底层核心协议[M].陈鸣,贾永兴,宋丽华,译.北京:人民邮电出版社,2008.

KOZIEROK C M. TCP/IP guide (volume I): the underlying core protocol [M]. CHEN Ming, JIA Yongxing, SONG Lihua, Translation. Beijing: People′s Posts and Telecommunications Press, 2008.

[6] 徐鑫,曹奇英.基于LwIP協议栈的UDP协议分析与优化[J].计算机应用与软件,2011,28(3):246?249.

XU Xin, CAO Qiying. UDP protocol analysis and optimization based on LwIP protocol stack [J]. Computer applications and software, 2011, 28(3): 246?249.

[7] 黄维超,刘桥,黄初华.基于FPGA的循环冗余校验并行实现[J].信息技术,2009,33(6):181?183.

HUANG Weichao, LIU Qiao, HUANG Chuhua. Parallel implementation of cyclic redundancy checks based on FPGA [J]. Information technology, 2009, 33(6): 181?183.

[8] 叶懋,刘宇红,刘桥.CRC码的FPGA实现[J].重庆工学院学报(自然科学版),2007,21(3):85?87.

YE Mao, LIU Yuhong, LIU Qiao. Implementation of CRC code based on FPGA [J]. Journal of Chongqing Institute of Technology (natural science edition), 2007, 21(3): 85?87.

[9] 严力.基于FPGA的以太网MAC协议的设计与实现[D].武汉:华中科技大学,2011.

YAN Li. FPGA?based Ethernet MAC protocol design and implementation [D]. Wuhan: Huazhong University of Science and Technology, 2011.

[10] Xilinx. Tri?mode Ethernet MAC v9.0 [EB/OL]. [2015?09?30]. http://china.xilinx.com/support/documentation/ip_documentation/ru/tri?mode?ethernet?mac.html.

[11] Xilinx. 1 G/2.5 G Ethernet PCS/PMA or SGMII v15.1 [EB/OL]. [2015?11?18]. http://www.xilinx.com/support/answers/54667.html.

[12] Xilinx. LogiCORE IP tri?mode Ethernet MAC V5.1 user guide [EB/OL]. [2015?07?28]. http://www.xilinx.com/support/answers/33111.html.