基于DLIS2K的高帧频线阵成像系统设计∗

2018-04-26陈文艺朱红雷

陈文艺 朱红雷 杨 辉

(1.西安邮电大学物联网与两化融合研究院 西安 710061)(2.西安邮电大学电子工程学院 西安 710121)

1 引言

随着CMOS性能的不断提升,CMOS线阵成像系统可以实现CCD线阵成像系统相同的成像质量[1~2],且系统具有低功耗、高集成度、高精度、高帧频等优势而被广泛应用到机器视觉、边沿检测、条码编码定位、非接触尺寸检测等光电检测领域[3~4]。目前国内工业设备上使用的CMOS线阵成像系统一般只有像机功能,不能进行实时图像处理,因此开展高帧频的CMOS线阵工业成像系统研究,并结合FPGA实现一体化的实时图像传感和处理系统具有较高实用价值[5~7]。

高帧频线阵成像系统的设计采用线阵CMOS图像传感器DLIS2K做光电转换,Altera公司的Cy⁃clone IV系列中的EP4CE10E22N8型现场可编程门阵列(Field Programmable Gate Arrays,FPGA)作为成像系统控制器和实时信号处理器,其中可编程片上系统(System on a Programmable Chip,SOPC)与上位机联合完成图像传感器的在线驱动配置,避免了通过设计硬核或硬件描述语言驱动传感器[8~9]。结合绝对位置检测的需要,通过对DLIS2K相机系统的数模转换(Analog to Digital Converter,DAC),预加载值等的在线优化配置,Binning模式配置和中值滤波改进了系统成像质量。

2 图像传感器

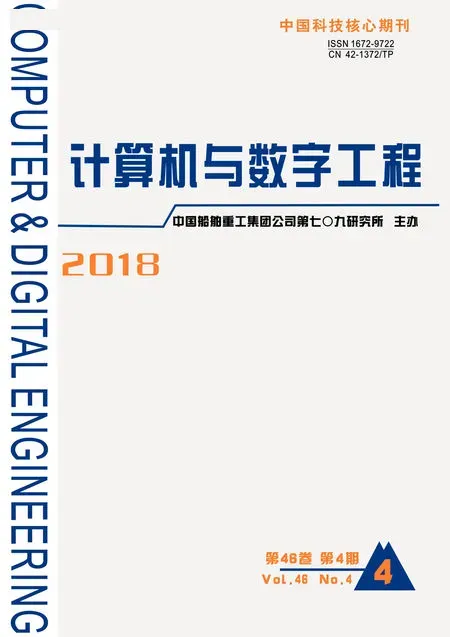

DLIS2K线阵图像传感器的内部功能框图,如图1所示,主要有六部分构成:成像核心模块、串口通信模块、时序及寄存器控制模块、DAC转换模块、11位锁存模块、视频处理模块[10]。

图1 图像传感器功能框图

DLIS2K线阵图像传感器的成像单元有效像元为4×2048,每行由2048个有效像元和48个暗像元组成,完成将光信号转换成模拟电信号。串口通信模块通过SENB,SDATA,SCLK完成图像传感器的工作时序和寄存器配置。同列的像元共用一个DAC,像元采集的模拟信号与DAC生成的斜坡对比,进行模拟信号的数字化。每一像元都有一个对应的11位的锁存器,锁存数字信号值。11位锁存值做移位运算移出10位数字信号,在视频处理模块做相关双采样后输出数字视频信号。

传感器内有42个寄存器,每个寄存器都为32位,前15位地址位,第16位为读写控制位,后16位为数据位。可以通过串口通信模块(SENB,SCLK,SDATA)完成对传感器的参数和工作时序控制。

3 成像系统优化配置

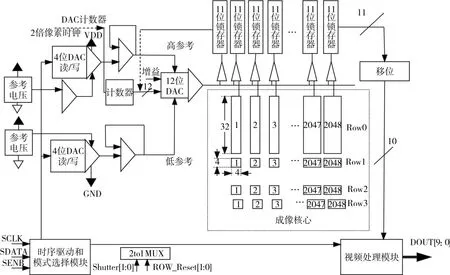

3.1 成像系统结构

成像系统由控制单元部分和传感单元部分组成,控制单元部分包括FPGA硬件控制系统和Nios软件控制系统,传感单元为线阵CMOS图像传感器器DLIS2K,系统结构框图如图2所示。硬件控制系统按照自顶向下的设计思想,结合图像传感器的正常工作时序要求,完成配置接口及驱动采集单元的控制逻辑设计。FPGA实时处理后信号通过RS232或USB接口输出到上位机。

图2 成像系统结构框图

3.2 成像系统的优化配置

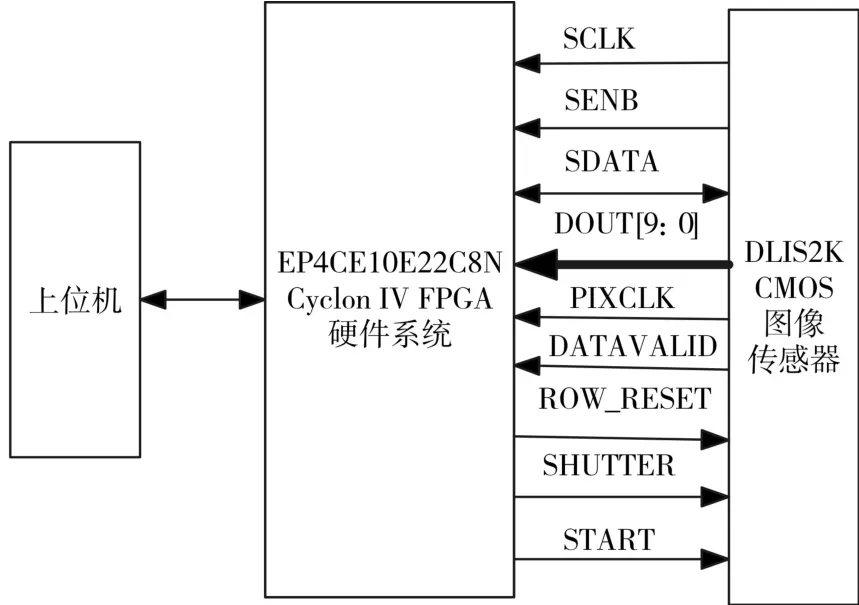

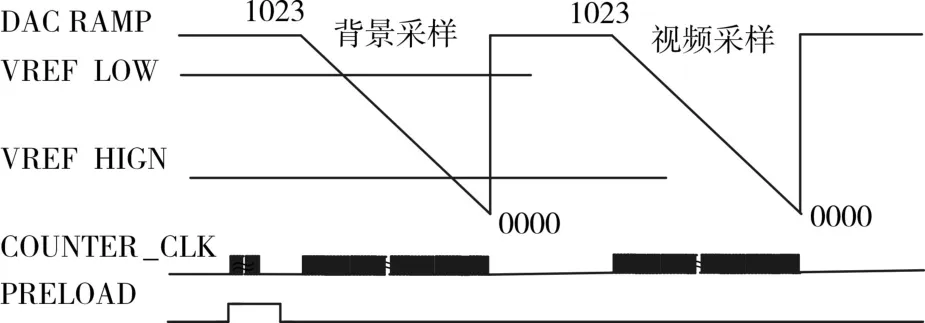

线阵图像传感器DLIS2K的A/D转换与一般器件不同,基本原理如图3所示,将每个像元光电转换的模拟信号s与位计数时钟(BIN_CNT_CLK)驱动产生的模数转换斜坡(DAC Ramp)信号一起并行送到每像元的比较器,根据编码表进行量化,同时计数时钟(COUNTER_CLK)驱动11bit锁存器锁存模数转换值。

DLIS2K像素DAC量化深度可选为8bit到12bit,以10bit DAC为例,相关双采样模式下,传感器上电后进行行选,DAC和锁存器都被复位,DAC计数在每一行背景斜坡前都有一个预加载,该预加载(PRELOAD)值默认是128,用于产生数字暗电压值,实际预加载设置可以由COUNTER_CLK和正向计数信号(PLUS_CNT)。A/D转换时,BIN_CNT_CLK进行二进制计数,依次驱动DAC Ramp信号产生背景斜坡和视频斜坡,量化区间从暗到亮为0000~1023,如图3(b)所示。成像单元光电转化的模拟电信号s与DAC斜坡信号一起送到列比较器,模拟信号根据DAC斜坡量化区间进行数字化,11位锁存器锁存被数字化的像素值。10bit DAC量化对应的8421编码如表1。

图3 线阵图传感器DLIS2K A/D转换基本原理

表1 10bitDAC转换为8421码量化表

通过配置传感器的DAC_CON寄存器调整DAC量化的参考低电平(VREF LOW)和参考高电平(VREF HIGH),DAC_CON的[7:4]位值控制低参考偏移,其值越小VREF LOW上移,值越大VREF LOW下移;DAC_CON的[11:8]位值控制高参考偏移,其值越小VREF HIGH上移,其值越大VREF HIGH下移。高参考与低参考之间为量化区间,如图4所示。预加载值PRELOAD为数字暗电平值,通过配置COUNTER_CLK寄存器实现对PRELAOD的设置;根据传感成像单元光电转化的模拟电信号s特点,合理设置参考电平和数字暗电压值可优化A/D转换后数字信号。

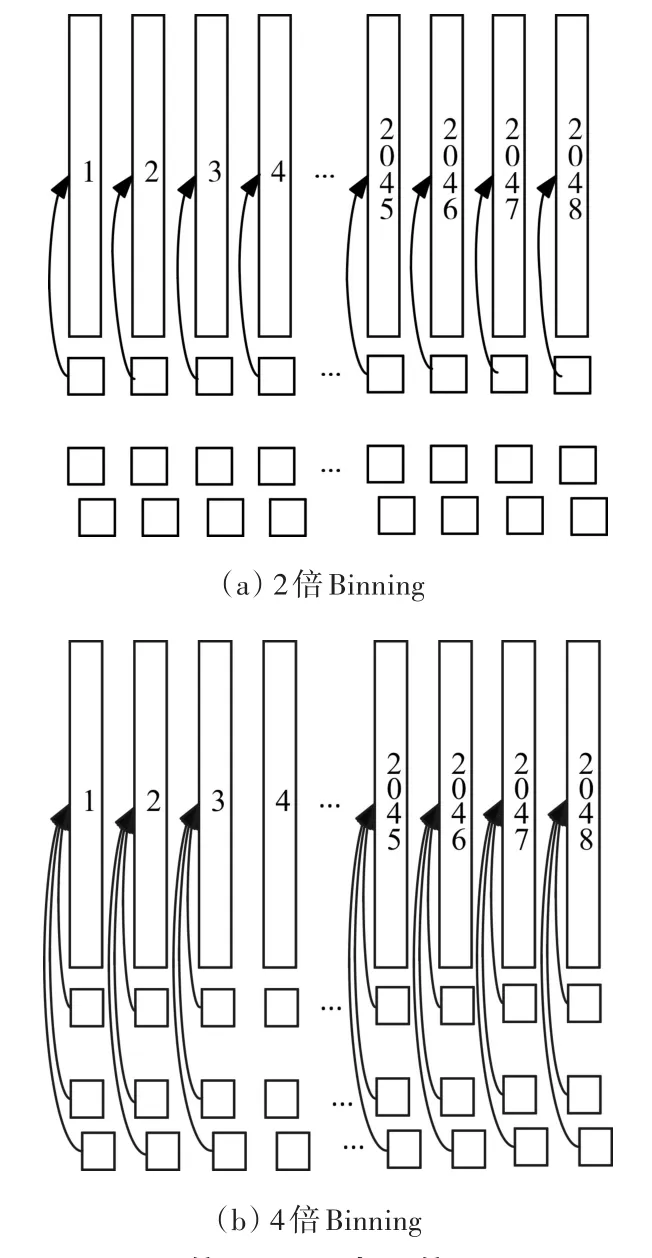

行Binning操作是将同列不同行的像元,通过2个或更多SHUTTER信号配置行并,即将不同行像元光电转换值传递到同一个传感器节点,增大像元有效感光为面积,从而增加灵敏度。2倍行Bin⁃ning,4倍行Binning,如图5(a),图5(b)所示。

图4 DAC配置调整参考电平

图5 2倍Binning与4倍Binning

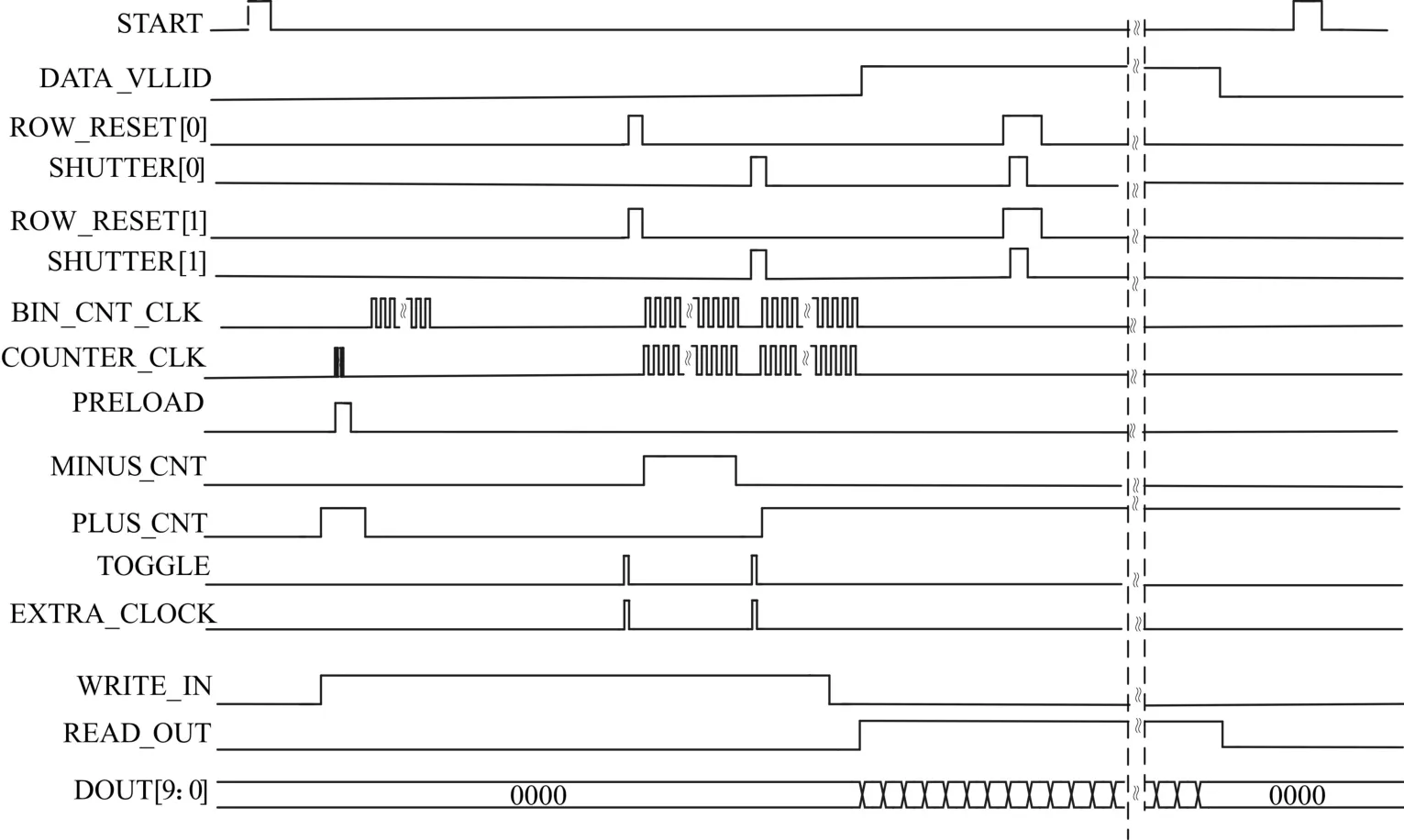

Binning操作是在同一个时间根据需要同时选用不止一个ROW_RESET[3:0]和SHUTTER[3:0]来完成的。通过(外部ROW_RESET和SHUTTER)重复时序和寄存器值对不同行进行Binning操作。2倍行Binning工作时序,如图6所示。

系统上电,首先通过内部寄存器ROW_RE⁃SET0,ROW_RESET1,SHUTTER0,SHUTTER1一起完成相机的行选及行复位,TOGGLE(置高电平)、EXTRA_CLOCK(置高电平),完成初始计数模式的设置,FPGA产生的START信号对相机采样进行时序同步及行初始化;然后PRELOAD(置高电平)、COUNTER_CLK、PLUS_CNT信号一起完成预加载值的设置,WRITE_IN被置高电平,准备背景噪声采样和视频采样;此后ROW_RESET0、ROW_RE⁃SET1脉冲复位传感节点电路,MINUS_CNT(置高电平)与BIN_CNT_CLK、COUNTER_CLK一起驱动完成背景噪声数字化;再后SHUTTER0,SHUTTER1脉冲将光电二极管转换视频电信号值传输到传感器节点,视频曝光结束,由BIN_CNT_CLK,COUN⁃TER_CLK一起驱动完成视频数字化,最终得到相关双采样输出的A/D信号值为视频信号值减去背景信号值。当采样结束ROW_RESET与SHUTTER同时置高,像元和传感器节点复位,然后SHUTTER和ROW_RESET置为逻辑低电平开始下一次视频曝光。

图6 2倍行Binning时序

成像系统完成一帧采样需要8500个像素时钟周期,可以通过提高系统像素时钟实现提高采样帧频。成像系统硬件控制系统晶振提供100MHz驱动时钟,通过FPGA内的锁相环PLL倍频,分频操作后,可以为系统提供不同的像素时钟。

4 实验与分析

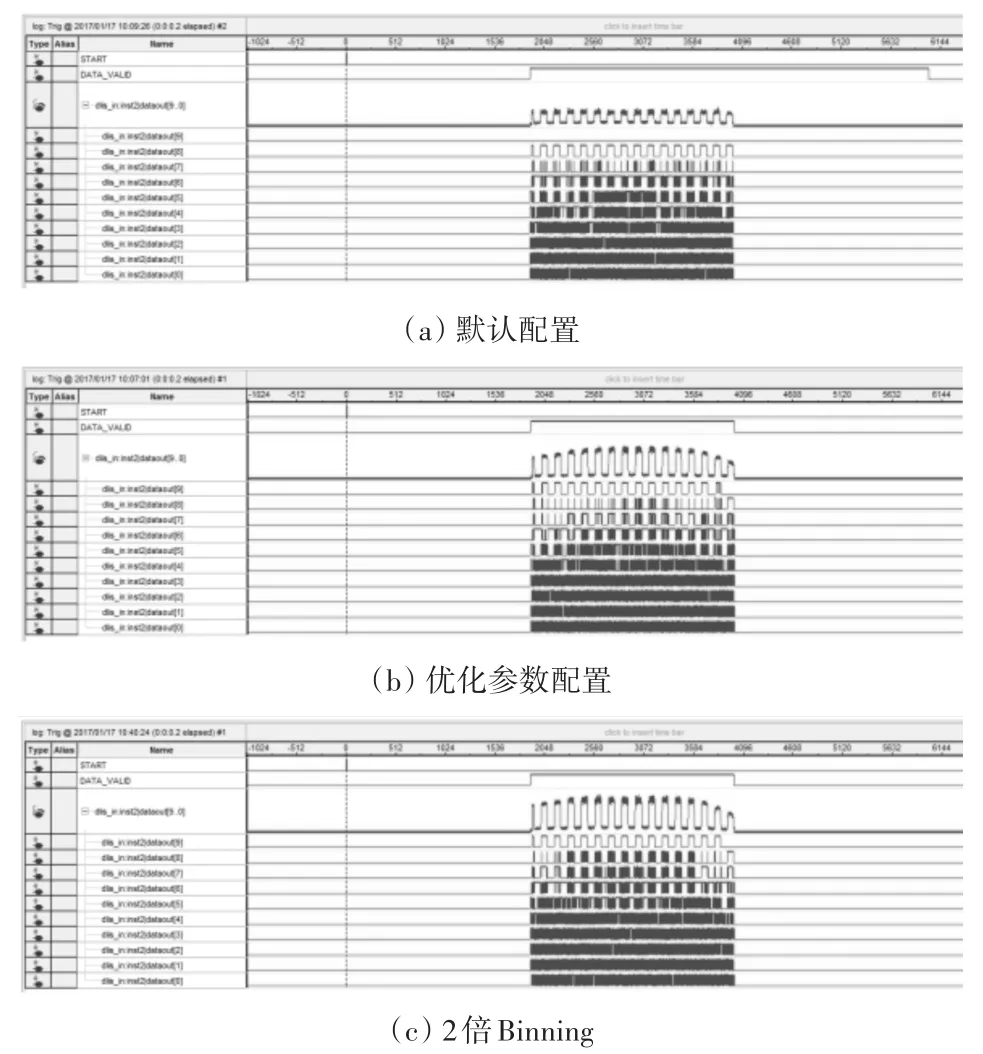

线阵成像系统工作时,一次采样只用一行像元,一行即是一帧图像,VGA不能很好的观察显示,而采用Altera FPGA开发工具Quartus II内置逻辑分析仪Signaltap II,对线阵成像系统系统采集的图像进行观察分析。在相同的实验条件下,成像系统系统工作在默认配置,优化参数配置,2倍Bin⁃ning模式下,用Signaltap II各采集一帧视频图像用波形显示,如图7(a),7(b),7(c)所示。

由图7(a),图7(b)优化配置前后输出一帧测试图像,可以证明通过优化配置参数系统很好的提高成像质量。图7(c)为配置到2倍行Binning模式时,系统灵敏度得到提升。成像系统由于读出噪声与光学系统因素,难免会引入一些噪声,用Matlab将上述三种配置下的一帧图像输出显示,如图8(a),8(b),8(c)所示。

从实验中发现输出信号具有较大的开关噪声,分别对默认配置,优化参数配置,2倍Binning模式采集到的数据做一维中值滤波[11~12],一维中值滤波窗口为1*7,滤波后输出显示如图9(a),9(b),9(c)所示。

图7 波形显示对比图

系统的信噪比(Signal Noise Ratio,SNR),可表示为其中S为相机输出有效视频信号,N为相机系统噪声信号。

图8 三种配置下一帧图像输出显示

图9 一维中值滤波后输出显示

分别对图 8(a),图 8(b),图 8(c),图 9(a),图9(b),图9(c)数据计算信噪比如表2所示。

表2 中值滤波前后三种工作模式信噪比

为了便于直观地观察线阵成像系统的实成成像性能,将多帧图像信息合成,在Matlab中一起输出显示。在相同的条件下,对光栅尺进行实际成像测试,将默认配置和优化配置、2倍Binning模式,三种配置时各采集100帧图像合成后,用Matlab显示如图10(a),10(b),10(c)所示。

通过对图10(a),10(b),10(c)对比分析可得,通过优化配置系统参数,成像系统系统的成像质量有很大的提高。通过行Binning操作,系统灵敏度得到较大提升。

系统采样一帧需要8500个像素时钟,通过FP⁃GA内锁相环PLL改变像素时钟,提高系统采样帧频。DAC量化10bit输出,成像系统分辨率2048,默认配置下,像素时钟为12MHz时,对应的帧频约为1412fps;配置到像素时钟为60MHz时,对应帧频约为7059fps;配置到像素时钟为80MHz时,对应帧频约为9412fps。成像系统的稳定性和可行性经过多次实验得到充分验证。

图10 光栅尺实际成像测试

5 结语

将DLIS2K线阵CMOS图像传感器应用到高帧频线阵成像系统中,FPGA为成像系统控制和处理核心芯片,上位机联合SOPC系统完成成像系统在线配置,支持在不改变原设计硬件电路基础上,通过上位机实现对成像系统的在线控制。实验结果表明,成像系统在高速采集、灵敏度、在线可配置等方面都有很大改进。成像系统工作在2倍Binning模式,像素时钟80MHz,分辨率为2048时,实时采样帧频可达9412fps/s,信噪比为42.3dB,具有良好的成像效果和系统稳定性,满足高帧频线阵成像设计要求。

[1]樊红星,张小超,刘磊,等.基于FPGA的CMOS线阵图像传感器数据采集系统设计[J].现代电子技术,2015,(14):129-132.FAN Hongxing,ZHANG Xiaochao,LIU Lei,et al.Design of data acquisition system of CMOS linear array image sen⁃sor based on FPGA[J].Modern Electronics Technique,2015,(14):129-132.

[2]王旭东,叶玉堂.CMOS与CCD图像传感器的比较研究和发展趋势[J].电子设计工程,2010,18(11):178-181.WANG Xudong,YE Yutang.Comparative Research and Future Tendency between CMOS and CCD Image Sensor[J].Electronic Design Engineering,2010,18(11):178-181.

[3]吴晓军,白韶红,啜丙强,等.基于CMOS线阵相机地铁隧道裂缝快速检测系统[J].路基工程,2015(3):185-190.WU Xiaojun,BAI Shaohong,SI Piqiang,et al.The Line Array Camera Subway Tunnel Crack Detection System Based on FPGA[J].Subgrade Engineering,2015(3):185-190.

[4]江志东,高太长,孙海洋,等.线阵CMOS图像采集及编码传输的实现[J].传感技术学报,2011,24(4):554-558.JIANG Zhidong,GAO Taichang,SUN Haiyang,et al.Im⁃plementation of Linear CMOS Image Data Acquisition and Data Encode Compression[J].Chinese Journal of Sensors and Actuators,2011,24(4):554-558.

[5]周中雨.工业相机在发动机装配线的应用分析[J].装备制造技术,2015(6):146-148,168.ZHOU Zhongyu.Application of Industrial Camera in En⁃gine Assembly Line[J].Equipment Manufacturing Tech⁃nology,2015(6):146-148,168.

[6]陈必威,梁志毅,王延新,等.基于FPGA的高帧速CMOS成像系统设计[J].计算机测量与控制,2012,20(5):1397-1400.CHEN Biwei,LIANG Zhiyi,WANG Yanxin,et al.Design of a High Speed CMOS Imaging System Based on FPGA[J].Computer Measurement&Control,2012,20(5):1397-1400.

[7]李方宁,王延杰,张涛,等.基于AM41V4传感器的高清高速CMOS相机系统设计[J].液晶与显示,2015,(3):492-498.LI Fangning,WANG Yanjie,ZHANG Tao,et al.Design of Hign-speed High-resolution CMOS Camera Acquisition System Based on AM41V4 Sensor[J].Chinese Journal of Liquid Crystals and Displays,2015,(3):492-498.

[8]Cheng K W,Yin C,Hsieh C C,et al.Time-delay integra⁃tion readout with adjacent pixel signal transfer for CMOS image sensor[C]//International Symposium on Vlsi De⁃sign,Automation,and Test.IEEE,2012:1-4.

[9]Yasutomi K,Itoh S,Kawahito S.A Two-Stage Charge Transfer Active PixelCMOS Image Sensor With Low-Noise Global Shuttering and a Dual-Shuttering Mode[J].Electron Devices IEEE Transactions on,2011,58(3):740-747.

[10]陈文艺,雷武亮,杨辉.基于Nios II的线阵图像传感器驱动系统设计[J].西安邮电大学学报,2016,21(1):84-88.CHEN Wenyi,LEI Wuliang,YANG Hui.Driving Design of Linear Image Sensor Based on Nios II[J].Journal of Xi'an University Of Posts And Telecommuntications,2016,21(1):84-88.

[11]普拉特,威廉克.数字图像处理[M].第4版新泽西州霍博肯市:约翰·威利父子,2007.Pratt,William K.Digital Image Processing[M].4th Ed.Hoboken,NJ:John Wiley&Sons,2007.

[12]牛敏,邬战军,牛燕雄,等.一种基于排序统计理论的快速图像中值滤波法[J].电子测量技术,2015(6):60-63.NIU Min,WU Zhanjun,NIU Yanxiong,et al.Fast Im⁃age Median Filtering Method Baded on Statistical theory[J].Electronic Measurement Technology,2015(6):60-63.