差分信号在印制线路板上的实现

2018-04-25李小亮

李小亮,陈 真

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 前言

差分信号(VDS,Voltage Differential Signal)是用一个数值来表示两个物理量之间的差异。差分信号又称差模信号,是相对于共模信号而言的。差分传输是一种信号传输技术,区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号振幅相等,相位相反。低电压差分信号(LVDS,Low-Voltage Differential Signaling)是美国国家半导体公司提出的一种信号传输模式。目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的研究,对于生产工艺、传输介质和供电电压等则没有明确规定。LVDS可采用CMOS、GaAs或其他技术实现,传输电压可以从5 V到3.3 V甚至更低;传输介质可以是PCB连线,也可以是特制的电缆。标准推荐的最高数据传输速率是655 Mbps,而理论上最高速率可以达到1.923 Gbps。本文主要研究如何在印制板上实现差分信号的传输,并且可以在125℃的高温环境下使用,这对集成电路高温加电有重大意义。

2 差分信号的实现方法

目前行业内一般的信号函数发生器只能发出单端信号,还不能够直接生成差分信号,即使目前已经有厂家能够制造差分晶体振荡器,实际使用下来发现有如下三个问题:(1)价格高昂;(2)驱动能力不够;(3)生成的差分信号干扰比较严重。所以要实现差分信号在印制板上的传输,就必须构建一个生成差分信号的电路系统。

2.1 外置驱动板

要实现差分信号在印制板上的传输,就必须先生成差分信号。我们首先想到的是设计一个能够生成差分信号的系统,通过这个系统生成差分信号再传输至印制板上。

2.1.1 通用驱动板

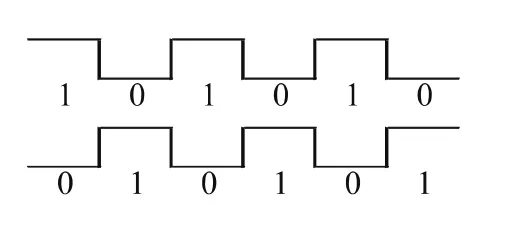

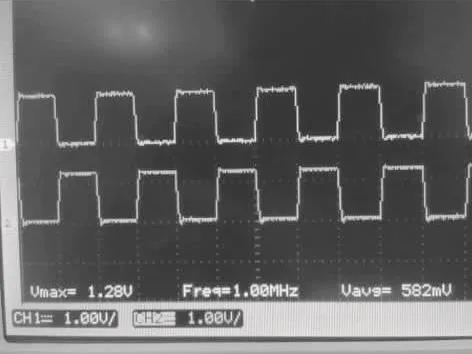

通用驱动板是目前加电过程中应用比较成熟的技术,它通过对16 MHz晶振产生的信号进行分频(一般我们选取1 MHz的频率,用10101010…表示),根据这个规则,我们可以得到1 MHz的任意二分频信号,同时也可以获得不同相位的分组信号,如频率为1MHz、相位差为180°的一组信号就可以表示为如图1所示。

图1 频率1 MHz、相位差180°的一组信号示意图

但这只是两组相位差为180°的信号,离我们需要的真正意义上的差分信号还有一些距离,所以不可以用此来代替差分信号。

2.1.2 特制驱动板

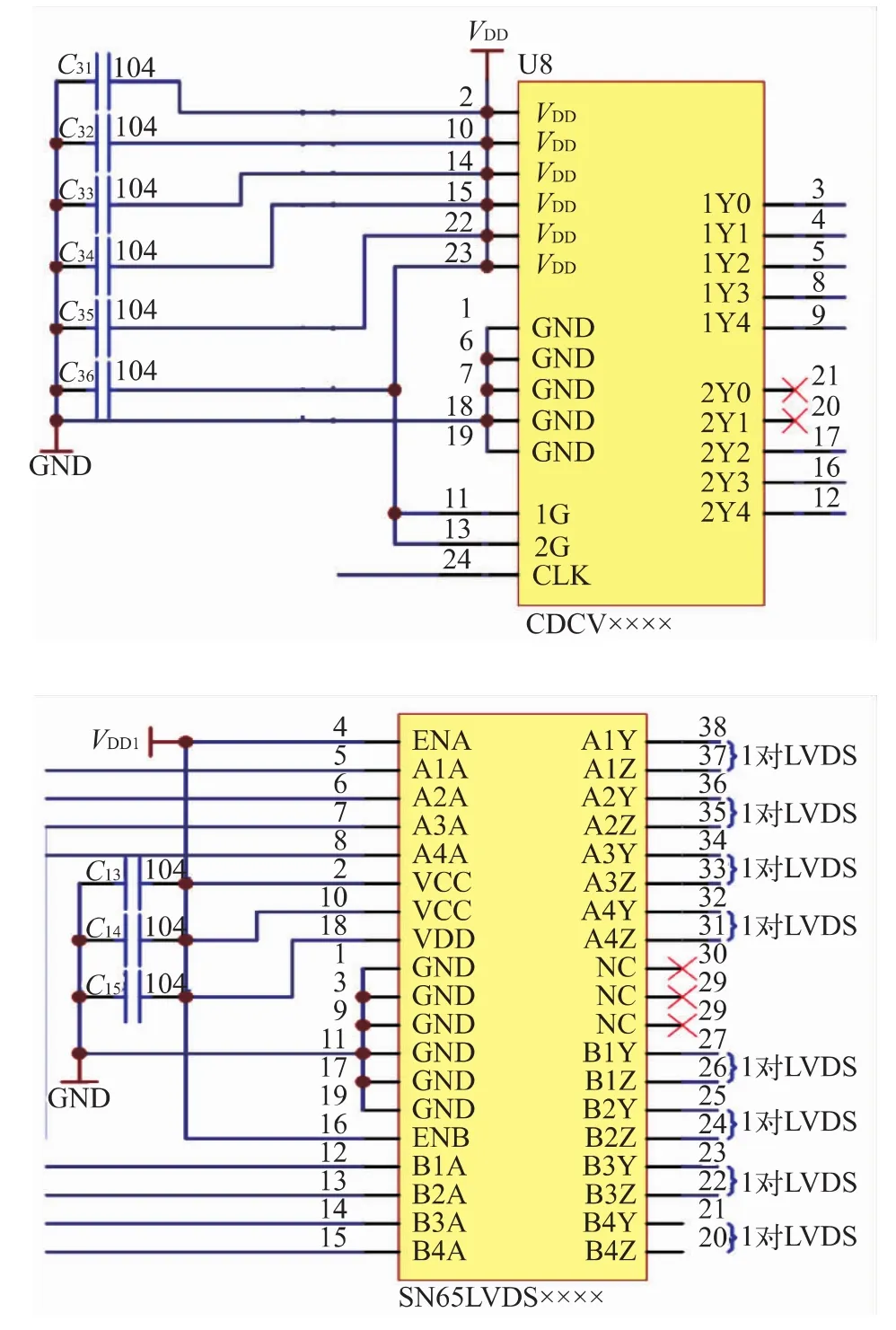

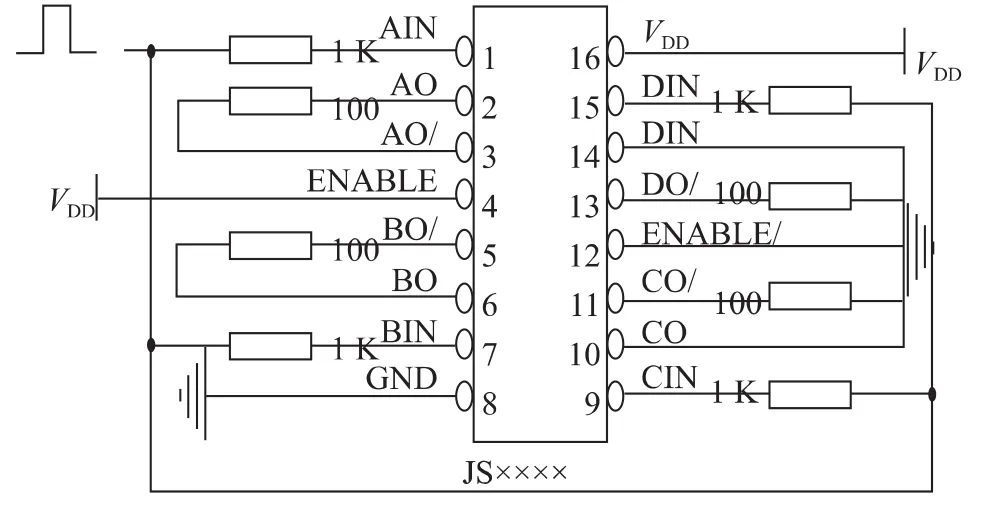

实际加电过程中,要产生所需要的差分信号,我们可以通过外接配置电路来实现,即输入单端信号,通过差分驱动电路生成所需的差分信号,市面上一般的差分驱动电路都为塑封电路,耐温不超过85℃,不能直接高温加电,驱动板只能放置于外面,且塑封电路价格便宜、易于获得。以99××驱动板SCH-32路为例,1 MHz单端信号通过CDCV××××生成多路信号,每路信号再经过SN××LVDS×××差分驱动电路形成差分信号。设计驱动板时要注意电源的滤波,以防止对差分信号的干扰,如图2所示。

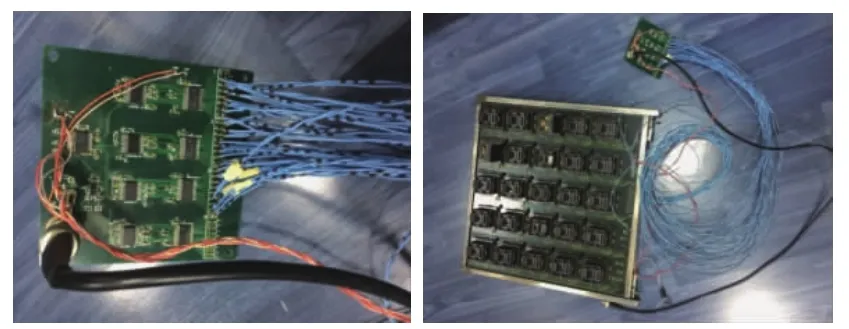

生成的差分信号传输到印制板上,如果使用普通线路会有很大的耗损,采用双绞线可以有效避免这种情况。但是实际加电过程中发现,一块标准老化板上工位数有几十个,每一个工位都需要单独的双绞线连接,连线冗杂,加电过程中容易断线,保存时也会占用很大的地方,如图3所示。

图2 99××驱动板SCH-32路示意图

图3 标准老化板双绞线连接成品图

外置驱动板的优点在于驱动板制作成本低,材料易得,制作方便,但是外置驱动板在加电时会因为人员因素或者连接本身的机械因素,造成连线脱落等问题,存放时也会挤占存储空间,不易保存。

2.2 内置驱动

外置驱动板的优缺点显而易见,且外置驱动板的不稳定性是一大隐患,在加电过程中因为连线脱落、断裂等问题引起的波动、脉冲,极易造成电路性能的损伤。要彻底根除这个问题,最好的办法就是让连线消失,即将驱动系统直接放置于印制板内部,这样就不需要外围连接线的传输,自然就排除了外置驱动板带来的隐患。

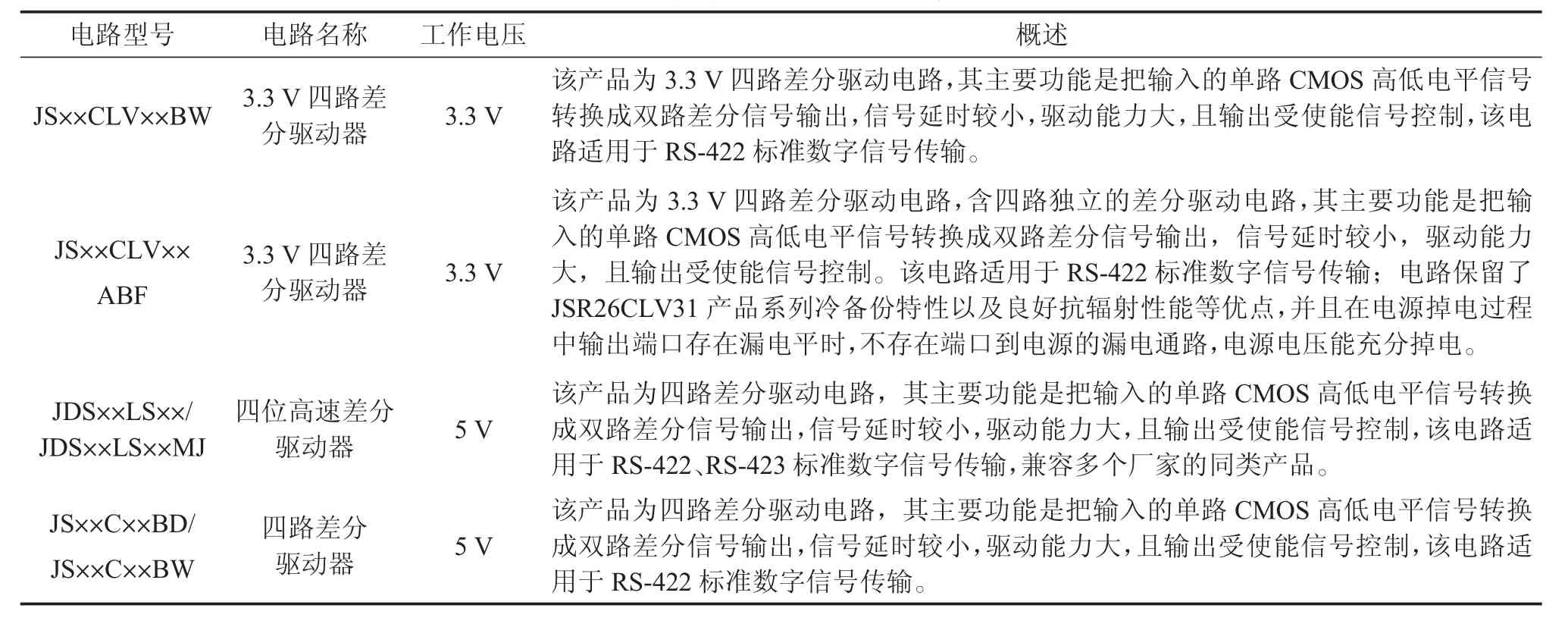

但要实现驱动系统内置并不容易,印制老化板的工作环境温度一般在125℃甚至可达150℃,而我们之前用的差分电路为塑封电路,其工作温度范围为-40~85℃,无法经受这么高的温度,所以首要任务就是寻找合适的差分驱动电路,我们根据资料寻得几款合适的差分电路,如表1所示。

表1 几款差分驱动器的比较

根据性价比及保有量,我们选取JS××CLV××BW作为研究对象,输出端 AA’、BB’、CC’、DD’接 100 Ω阻抗匹配,如图4所示。

图4 JS××CLV××BW差分信号生成系统

AIN、BIN、CIN、DIN 输入 0~3.3 V 的 1 MHz单路高低电平信号,通过使能端控制 AOAO/、BOBO/、COCO/、DODO/输出±3.3 V的差分信号。印制板示意图如图5所示。

图5 JS××CLV××BW印制板示意图

需要特别注意的是差分信号的传输需要走差分等长线,以确保差分信号传输的准确性,降低差分信号传输因受线影响而失真的概率,如图5虚线处所示。

生成的差分信号幅度为±3.3 V,但很多情况下,当我们进行LVDS传输时,信号的幅度要低于3.3 V,因此我们还需要对现有的差分信号驱动系统进行改进,以期能够适应不同幅度的LVDS信号。

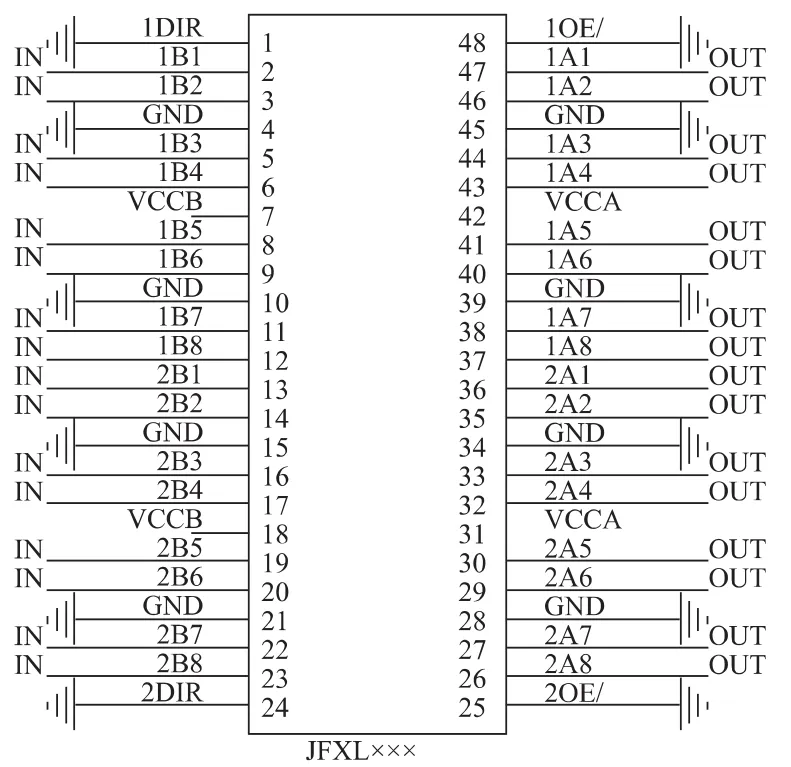

如图6所示,将生成的差分信号通过JFX×××进行电平转换(JFX×××支持1.1~3.6 V电源的任意转换),通过控制VCCA和VCCB即可以得到我们想要的幅度的差分信号。

图6 JFX×××电平转换系统

内置驱动由于需承受的温度较高,导致其对芯片、材料的要求也比较高,但输出差分信号稳定、可靠性高、幅度可控,且使用寿命长,降低了生产过程中的使用复杂性,保存时按一般保存方法处理即可,不必进行特殊处理。

3 结果与讨论

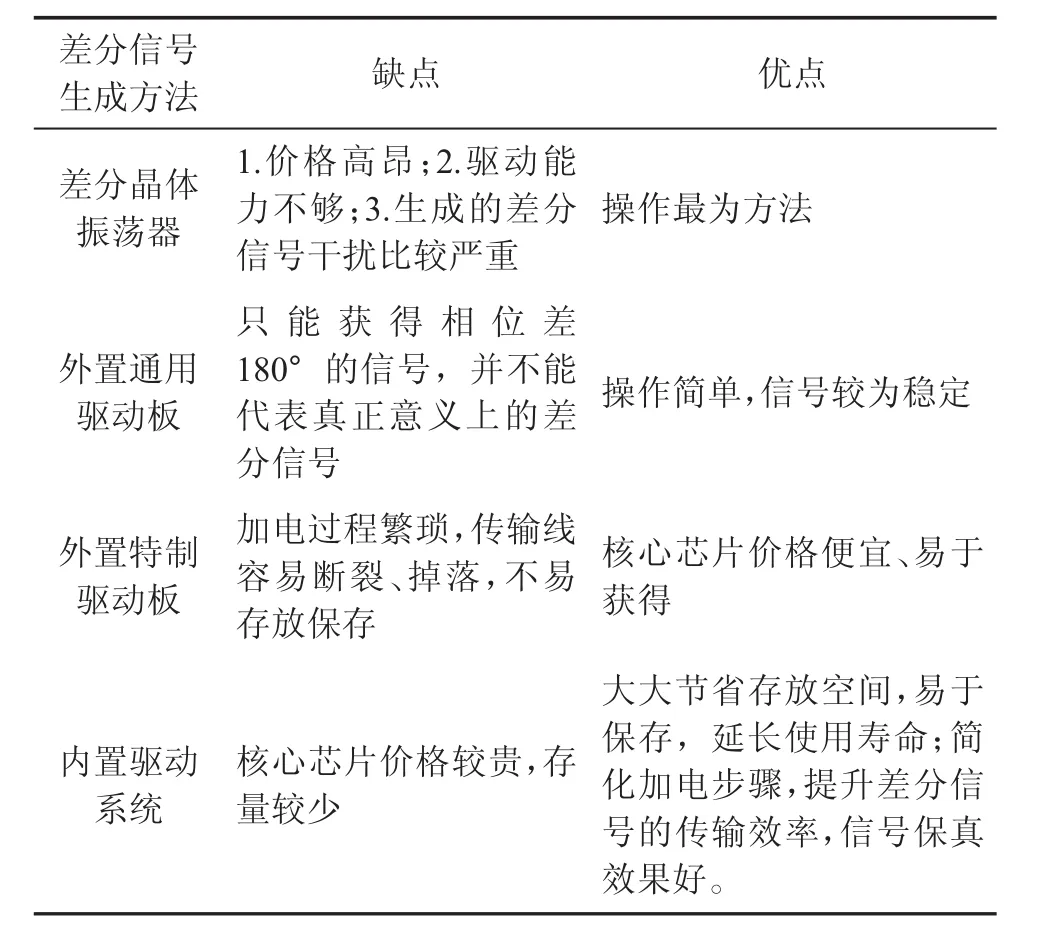

本文研究了现阶段几种差分信号实现的方法,各自的优缺点比较明显,具体使用时可以根据用户自身的需求进行选择,如表2所示。

表2 四款差分信号实现方法的比较

我们在系统的输入端输入0~3.3 V、1 MHz的单端信号,信号在经过JS××CLV××BV之后生成±3.3 V的差分信号,根据实际需要再经过JFXL×××进行电压变换,变为±1.2 V、1 MHz的差分信号,如图7所示。从图中我们可以发现内置驱动系统具有稳定的输出,生成的差分信号几乎没有毛刺,平稳光滑,且还可以根据需要灵活地对生成的差分信号进行低电压变换。

图7 差分信号输出监测系统

4 结论

综合比较下来,内置驱动系统生成的差分信号平稳光滑,提升了加电效率,不会对试验电路产生干扰,可以在125℃的高温环境下使用,且可对信号幅度灵活地进行变换。

在集成电路高速发展的今天,提供平稳光滑的差分信号输出是一个十分重要的内容。内置差分信号输出系统输出信号稳定,不仅能适应高低温环境,还能够进行低电压变换,是当前可靠性最高的差分信号生成系统。基于其优越的性能,其在老练试验领域及相关测试领域也会得到越来越广泛的应用。

参考文献:

[1]Zamarreno Ramos C,Kulkarni R,Silva Martinez J,Serrano Gotarredona T.A 1.5 ns OFF/ON Switching-Time Voltage-Mode LVDS Driver/Receiver Pair for Asynchronous AER Bit-Serial Chip Grid Links with up to 40times event-rate dependent power savings[J].TEEE transactions on biomedical circuits and systems,2013,7(5):722-731.

[2]Hazem W Mater,Khaldoon Abugharbieh,Abdel-Karim Al-Tamimi.A 1.8 V low power 5 Gbps pmo-based output driver withgood return lossperformance[J].Analog Integrated Circuits and Singal Processing,2014,79(1):1-13.

[3]黄寅,张卫杰,王秀坛,彭应宁.LVDS高速数据传输设计及其在SAR处理机中的应用[J].微计算机信息,2005(19):102-104.

[4]伊腾岳.LVDS接口I/O抗辐射加固技术研究[D].西安:西安电子科技大学,2015:1.