一种快速验证FPGA互连线连接正确性的方法

2018-04-25范继聪徐彦峰

范继聪,惠 锋,徐彦峰,胡 凯

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214072;2.无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

随着集成电路制造工艺水平的不断提高,器件特征尺寸不断缩小,FPGA规模越来越大,集成模块越来越多,可以实现更加复杂的功能。FPGA主要由可编程输入输出、可编程互连和可编程逻辑组成,其中可编程互连包括可编程互连线和可编程互连开关。相对于IO/CLB/DSP/BRAM/SWB等模块来说,FPGA的互连线验证面临很大的挑战。不同于有些ASIC芯片可以采用自动布局布线的设计,FPGA的互连需要定制设计,在设计过程中很容易出现互连线短路和开路的现象,如何检查出这类错误是非常困难的。当前普遍采用动态仿真的方法来验证互连线的正确性,这种方法不仅速度很慢,而且覆盖率很低,所以需要一种能够快速实现FPGA互连线连接正确的验证方法。本文提出一种基于互连网络比对来验证FPGA互连正确性的方法,能有效检查原理图中互连线的开路和短路情况,具有实现速度快、覆盖率高达100%的优点。

2 互连线定义及分类

互连线是FPGA中信号传递的桥梁,随着FPGA的规模越来越大,互连线在整个FPGA中所占比重也越来越大。互连线根据跨度和方向进行定义和分类,一般通过互连线的名字定义互连线类型,FPGA中互连线的名字一般由4部分组成,分别为:

(1)方向:FPGA中互连线的方向采用与地图方向一样的定义,既上北(N)下南(S),左西(W)右东(E),通常互连线名的第一部分字母代表方向。

(2)跨度:跨度指互连线所跨越可编程逻辑单元CLB的个数,一般有2、5和6,通常叫做2倍线、5倍线和6倍线。有时还有长线(跨度为18、24等),互连线名的第一部分数字代表跨度。

(3)位置:通常一根互连线包括起点(BEG)和终点(END),起点为驱动点。有些互连线还包括中间点,是在起点和终点间的一个抽头,可以更灵活,通常称为中间点(M ID),这里“中间点”并不是严格意义上的中点,对于5倍线来说,中间点一般是在离起点跨度为3的地方,通常互连线名的第二部分字母代表位置。

(4)编号:为了提高布通率,通常FPGA中一类互连线有很多根,为了区别开来对线进行编号,通常互连线名的最后数字代表编号。

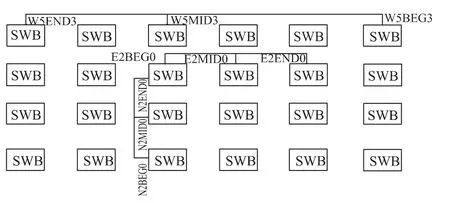

通过上述互连线名的定义,可以很清晰地通过互连线名确定互连线方向、跨度和编号等信息。图1所示为常见互连线的示意图,图中显示了5倍线和2倍线,根据互连线的名字可以很容易地得到互连规律。

图1 互连线示意图

3 互连线验证方法及实现

FPGA中互联线种类丰富、数量庞大,随着FPGA规模的不断增加,动态仿真一个用例就需要几天以上的时间,验证整个FPGA互联线连接正确需要大量的仿真用例,采用动态仿真方法来验证互连线的连接正确性逐渐变得不可行。本文基于互连网络比对提出一种快速验证FPGA互联线连接正确性的方法,通过验证FPGA的互联资源文件正确性来实现互连线的验证。

FPGA中的互连线一般由起点、中间点和终点组成,互连线按照一定规律从一个SWB出发,经过一些SWB,到达一个SWB结束。FPGA中每一个SWB都有一个绝对坐标值,可以使用XnYm代表位于第n列第m行的SWB。FPGA互联资源中的每一类互连线都会从每一个SWB出发,这样就可以根据互联规律得到所有互联线的连接信息,将这些连接信息以文本的形式展现出来,就是所谓的FPGA互联资源文件。互联资源文件包含FPGA内部所有互连线的连接关系,文件内部为多行类似X6Y6_ER2BEG0→X7Y6_ER2M ID0→X8Y6_ER2END0的信息,互联资源文件为文本文件,便于比对处理。

图2所示为本文所述互连线验证方法的整体流程图,从图中可以看出,本文所提出的快速验证FPGA互连线连接正确性的方法主要从两个方面出发,一是根据互连规律和所设计芯片的ARCH文件信息,生成互连资源文件,作为GOLDEN模型;二是对设计好的芯片网表进行解析,得到实际电路对应的互连资源文件,将得到的互连资源文件与GOLDEN模型文件进行比对,即可实现对实际设计电路互连正确性的验证。

图2 互连线验证方法流程

要想得到互连资源GOLDEN文件,需要提供ARCH文件和互连规律。ARCH文件一般提供FPGA芯片中SWB的行数和列数信息,SWB在FPGA中二维分布,提供行数和列数信息,即可得到整个FPGA芯片中所有的SWB位置信息。根据上述互连线的名字可以很容易得到互连规律。有了芯片的ARCH信息和互连规律,即可通过编程语言编写互连资源生成程序,得到理想的互连资源文件,即互连GOLDEN文件。本文采用perl语言得到互连资源生成程序,生成的互连线连接GOLDEN文件内容如图3所示。

SWB在整个FPGA芯片中均匀分布,如图4所示,每一个SWB都有唯一的名字,可以标识其所在的行和列信息。如果在设计FPGA芯片时采用展开式的设计,每一个SWB的名字都可以采用绝对坐标来进行命名,这样可以很容易地根据网表信息提取出整个芯片中的互连信息。

图3 根据互连规律生成的互连资源文件

图4 SWB分布

随着FPGA芯片规模不断增大,展开式的设计已不适用,当前主要采用层次化的电路设计,相对于展开式设计,层次化设计具有可复用性,可大大缩小电路文件的大小,同时提高设计速度,缩短设计周期。采用层次化的设计需要对电路各个层次模块采取有意义的名称,保证能够解析得到每个SWB的绝对坐标。本文提出的验证方法采用如图5所示的层次化命名,每个模块的名称中都包含坐标信息,该坐标信息是相对于本层次的相对坐标信息,根据各个相对坐标信息,代入相应的绝对坐标求解公式,即可得到每个SWB的绝对坐标信息。

图5 层次化设计命名示意图

通过Virtuoso得到整理好的FPGA整体电路网表文件,编写网表解析程序,网表解析程序可以根据整个电路网表的连接关系,从每个SWB的驱动点开始追踪连接关系,这样可以得到整个FPGA芯片中的所有互连资源,将追踪到的所有互连资源集中到一个文件,即可得到实际设计电路所对应的互连资源文件,其内容如图6所示。每个SWB的名字以SWB开头,附带坐标信息。对上述方式所生成的两个互连资源文件进行比对,即可发现设计中存在的问题。如果设计中存在互连线开路现象,则通过设计解析得到的互连资源文件中存在不完全的互连线,丢失了开路后的结点。如果设计中存在互连线短路现象,则通过设计解析得到的互连资源文件中存在加长的互连线,相对于正常的互连线,多出了结点信息。

图6 解析电路得到的互连资源文件

4 结论

本文提出的快速验证FPGA互连线连接正确性的方法已经在实际工作中应用实现,应用表明该方法可以有效地检查出电路设计过程中导致的互连线短路和开路现象。相对于传统基于动态仿真的验证方法存在仿真时间长、覆盖率低的缺点,该方法采用互联资源文件比对的方法实现互联线连接验证,因为互联资源文件包含所有的互联信息,所以可以实现100%覆盖率,采用动态仿真实现高覆盖率需要大量仿真用例,且很难实现100%覆盖。同时生成互联资源GOLDEN文件、解析实际电路得到互联资源文件和两个互联资源文件的比对都可以在很短的时间内实现,整个验证过程可以在一天时间内完成,相对于传统的动态仿真一个用例动辄需要几天时间以上,大大提高了验证效率。该方法具有速度快、覆盖率高的优点,可以快速有效地发现FPGA设计前期所导致的互连线连接错误,提高FPGA产品开发速度,缩短整个设计周期,具有重要的参考和实用价值。