一种红外仿真图像数据流播放器设计与实现

2018-04-25扬刚

,扬刚,,

(中国酒泉卫星发射中心,甘肃 酒泉 732750)

0 引言

红外图像以其独特的成像特点和复杂天气条件下的适应能力,已经成为发射场光电经纬仪最重要的目标跟踪测量、景象获取和辐射特性测量的手段。而目前光学仿真训练系统主要针对可见光测量系统,红外图像的仿真训练系统研究较少。为满足仿真训练的需求,实现不同任务目标的成像和飞行姿态仿真,以及环境背景的仿真,采用增强现实的思想,提出基于红外虚拟目标与真实背景融合的红外图像仿真方法,提升仿真训练效果,该方法采用高速实时数据流的播放技术,因此,研究高速实时数据流播放器成为实现红外图像仿真的关键。

目前,现有的大众型多媒体播放器通常是一种集成音频、视频、图片浏览于一体的多功能播放器。由于主要应用于人眼观赏,所以一般存在格式比较固定,播放的帧频较低等不足。现有的播放器技术存在的问题突出表现为以下几点:

1)通用的基于专用ASIC的播放器,以大众化视听为目的,格式固定,各种性能指标都比较低,不能满足专业领域的需求;

2)一些简单的仅使用FPGA实现的图像播放器,由于FPGA内部存储器非常小,都是播放固定格式的单帧图像,主要用来测试电路的时序关系正确性,无法满足高带宽、高帧频的需求。

3)目前的播放器都不具备实时图像与仿真图像信息合成的功能,不能实现同时输入和输出。

为了满足光电经纬仪仿真训练系统对高速实时数据流播放的需求,本文提出了一种基于FPGA和DSP技术实现的红外图像仿真高速实时数据流播放器,实现高带宽、高帧频、高分辨率的图像流数据的实时输出,用于光电经纬仪仿真训练系统的红外仿真图像的高速实时播放。

1 高速实时数据流播放器总体设计

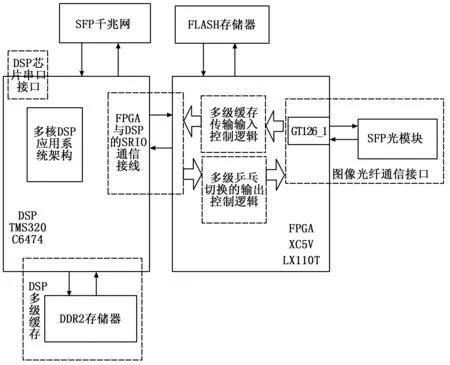

播放器主要包括了FPGA芯片(Xilinx公司的XC5VLX110T)、DSP芯片(TI公司的TMS320C6474)以及时钟芯片、FLASH存储器、DDR2存储器、SFP千兆网模块以及SFP光模块等。

播放器工作的3个过程,即图像采集、虚拟目标叠加、图像发送,3个过程并行执行。整个处理模块的输入与输出接口为图像输入光纤口和图像输出光纤口、编码器输入串口、虚拟目标输入千兆网口。DSP芯片具有3个独立的内核,每个内核具有完全对等的结构和功能。根据播放器的应用需求,播放器具有虚拟目标图像接收功能、虚拟目标与真实背景融合功能、真实背景图像输入与融合图像输出功能。每个功能赋给1个独立的DSP内核去完成。其中,DSP的第一个内核用来负责与外部主机进行千兆网络通信,DSP的第二个内核用来接收外部的串口数据输入及进行叠加算法运算,DSP的第三个内核负责与FPGA进行SRIO通信,将FPGA芯片中FIFO内的数据搬运到DSP的第三个内核的RAM中,并把RAM 中的数据传输到外部DDR2中。DSP的3个内核都可以访问外部DDR2,通过访问外部DDR2可以实现3个内核之间的数据共享。

叠加算法运算由DSP的第二个内核来完成。第二个内核在每次帧中断来时,采集实时编码器数据,把虚拟目标的指向编码器与实时编码器进行比对计算出像素偏移量,在采集好的图像合适位置叠加上虚拟目标,并进行边缘融合处理,使得虚拟目标与背景融合效果更逼真。虚拟目标图像数据通过千兆网传输,由DSP的第一个内核接收并缓存至DDR2。

经过叠加处理后的增强现实图像信息在外部DDR2上,DSP的第三个内核首先从DDR2中分批传输图像到第三个内核的L2中,再通过SRIO接口把L2的数据发送到FPGA,在FPGA中实现电光转换发送出去。

播放器总体结构如图1所示。在上电后, FLASH存储器中的代码自动加载到FPGA芯片内部开始工作,通过千兆网模块将仿真图像发送到DDR2存储器上缓存,FPGA芯片读取DDR2存储器中的叠加图像并进行电光转换,发送到光模块输出,实现整个虚拟目标叠加的功能。FLASH存储器与FPGA芯片连接,FLASH存储器用于存储FPGA代码,加载代码后驱动FPGA芯片进行数据处理;DDR2存储器与DSP芯片连接,DDR2存储器用于存储仿真图像;FPGA芯片与DSP芯片连接,用于实现从DDR2存储器中读取图像数据发送到FPGA芯片对应的FPGA内部串行口上;光模块与FPGA芯片连接,用于将FPGA串行通道上的数据通过光模块发送到外部光纤通道;千兆网模块与DSP芯片连接,用于将外部产生的仿真图像通过千兆网模块和DSP芯片传输到DDR2存储器上。

图1 播放器总体结构图

2 关键算法实现

2.1 多级缓存传输的输入控制

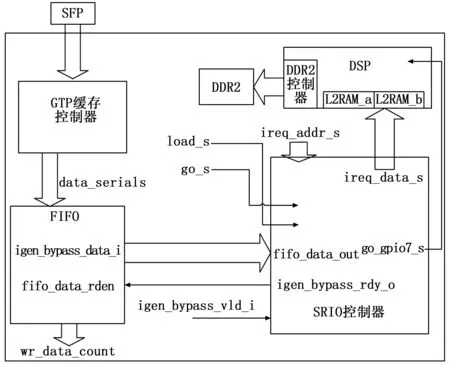

图2所示为播放器多级缓存传输的输入控制逻辑图。利用该控制逻辑,实现了外部图像数据通过光纤输入到FPGA内部的GTP缓存控制器,再由SRIO输入到DSP的DDR2存储器。该多级缓存传输的输入控制逻辑具体算法如下:

图2 播放器多级缓存传输的输入控制逻辑图

1)光纤图像接收解析模块,根据上述设计的光纤图像帧格式、包格式,解析出需要的帧首信号、帧尾信号、16位图像原始数据、原始数据有效信号。

2)在FPGA内部构建一个256 Kbit的FIFO缓冲区。解析出的帧首信号作为FIFO的复位信号,16位原始数据有效信号作为该FIFO的写使能,16位图像原始数据连接到FIFO的数据输入端口。基于这样的写逻辑,实现了外部光纤图像数据不断输入到内部FPGA的FIFO中。但是这个FIFO的容量有限,不能保存下一幅完整的图像,因此需要下面的读逻辑来读取FIFO内的数据。

3)构造一个读控制逻辑。读逻辑由FIFO的wr_data_count信号来决定是否对FIFO进行读取,设置门限为2 Kbit,即wr_data_count信号大于1023后,启动SRIO使能信号igen_bypass_vld_i信号。每启动1次后,能够以3.125 Gbps的数率传输2 Kbit到DSP端。在A步骤中,外部原始图像数据光纤传输数率为2.5 Gbps,小于读数据速率。因此,FIFO能够完整接收并完全转移一幅完整图像,而且FIFO不会产生溢出。

4)由FPGA的FIFO中读取的图像数据,通过SRIO接口输出到了DSP端的内部L2RAM中,然而可用于图像缓存的L2RAM容量只有256 Kbit,不能缓存下一幅完整图像,因此设计了两个128 Kbit的缓存用来做乒乓(PingPong)接收,在步骤3)中构建一个SRIO,每传输完128 Kbit产生一个脉冲信号go_gpio7_s,该信号通过GPIO输出到DSP中,作为DSP进行乒乓切换的中断源。

5)当Ping部分在接收SRIO数据时,通过DMA的方式将Pong中的数据从L2RAM读走输出到DDR2中。从L2RAM到DDR2的数据读走数率为3.2 Gbps,该速率大于SRIO写入L2RAM的速率。因此,可以保证传输过程中L2RAM不会发生溢出。

重复1)~5)的步骤,实现光纤图像数据不间断地送到DSP外部DDR2的缓存。从各级缓存数据传输速率可以看出,光纤速率小于SRIO速率,SRIO速率小于L2RAM搬运到DDR2速率,使用上述多级缓存输入控制逻辑算法可以实现实时背景图像的输入。

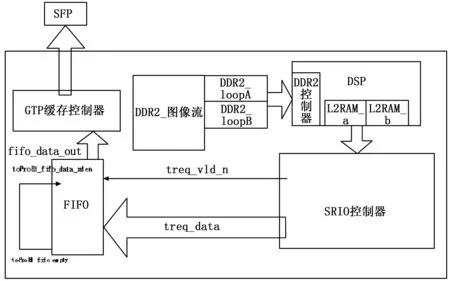

2.2 多级乒乓切换的输出控制

虚拟目标叠加功能从外部来看,每次输出一帧图像;从内部来看,输出过程首先由DSP发出图像传输开始信号,然后将图像分成很多小块,逐次将每小块数据通过SRIO发送到FPGA内部FIFO中,再将FIFO内的图像数据通过包格式转换后发送到GTP端口上。图像数据就不间断地从DDR2上的原始格式转换到光纤上的包格式数据,从而完成每帧图像的输出。因此,设计一种基于多级乒乓切换的虚拟目标叠加图像的数据输出算法。

图3所示为播放器多级乒乓切换的输出控制逻辑图。主机上虚拟目标叠加的图像数据首先通过网络发送到装置在DSP上的连续DDR2存储器中,即图中的DDR2_图像流区域,该图像流为图像的压缩格式,以便提高缓存的相对容量,图像解压缩目标区域为DDR2_LOOPA/B,启动虚拟目标叠加图像输出后,图像数据从DDR2_LOOPA或DDR2_LOOPB中不断切换输出到DSP的内部L2RAM_a或L2RAM_b上。然后SRIO控制器将L2RAM_a或L2RAM_b中的图像块数据通过treq_data的32位数据线发送到FIFO中,输出有效信号为treq_vld_n信号,GTP缓存控制器根据FIFO的状态,当FIFO内字节数到达2 kbit后,便开始往GTP端口输出FIFO中的数据。这样,通过DSP程序控制SRIO控制器,不间断地把DDR2上的图像流数据发送到外部SFP光纤上,从而实现了的叠加图像的数据输出。

图3 播放器多级乒乓切换的输出控制逻辑图

2.3 图像缓存循环队列控制

图4所示为播放器图像缓存循环队列控制图。将DSP的DDR2存储器分割成3个功能循环的区域DDR2_LOOP0、DDR2_LOOP1、DDR2_LOOP2。

图4 播放器图像缓存循环队列控制图

播放器图像缓存循环队列控制算法如下:

1)在FPGA中,通过光纤图像接收解析模块,解析出帧首信号。通过GPIO输出到DSP中作为图像帧头信号中断源。该中断用来初始化若干变量,图像帧号(FRAME_CNT)统计等。

2)光测设备实时背景图像通过光纤接口(2.5 Gbps)进来,在FPGA内部进行光电转换,通过DSP与FPGA之间的SRIO接口(3.125 Gbps)把图像数据输入到DSP的内核缓存(L2)中,接着把L2中的图像数据通过DMA方式传到DSP的外部DDR2中,一帧图像要经过多次这样的传输方式完成采集工作,即前述的多级缓存传输模式的逻辑控制。采集占用区域为DDR2_LOOP2,此时该区域的功能标记为DDR2_RECV,保存了当前正在接收到的背景图像。

3)虚拟目标图像与背景图像的叠加合成处理也在DDR2中进行,处理占用区域为DDR2_LOOP0,此时该部分DDR2的功能标记为DDR2_ADD。该DDR2_LOOP0中的背景图像是上一帧的背景图像。

4)经过叠加处理后的图像信息在外部DDR2的区域DDR2_LOOP1上,此时该区域功能标记为DDR2_SEND。此时的背景图像相对当前帧来说,已经是两帧前的背景图像。DSP首先从DDR2_LOOP1中分批传输图像到L2中,再通过SRIO接口把L2的数据发送到FPGA,在FPGA中实现电光转换发送出去。

5)上述过程是以帧中断作为同步关系,通过FRAME_CNT除以3得到的余数来实现图像缓存队列的切换。当余数为0时,DDR2_LOOP2映射成DDR2_RECV,DDR2_LOOP0映射成DDR2_ADD,DDR2_LOOP1映射成DDR2_SEND。

6)下一帧中断到来时,FRAME_CNT加1,余数为1,DDR2_LOOP2映射成DDR2_ADD, DDR2_LOOP0映射成DDR2_SEND,DDR2_LOOP1映射成DDR2_RECV。

7)又一帧中断到来时,FRAME_CNT加1,余数为2,DDR2_LOOP2映射成DDR2_SEND, DDR2_LOOP0映射成DDR2_RECV,DDR2_LOOP1映射成DDR2_ADD。

8)再一帧中断到来时,FRAME_CNT加1,余数为0,DDR2_LOOP2映射成DDR2_RECV, DDR2_LOOP0映射成DDR2_ADD,DDR2_LOOP1映射成DDR2_SEND。该步骤同步骤5)相同,这样实现从5)~7)周而复始的循环队列切换。

3 实验结果与分析

在DSP的第三个内核的L2缓存上有FPGA端口的输入和输出,还有和DSP外部DDR2的输入和输出,通过实际测试L2缓存的读写速度为4 GB/s以上,单个功能带宽可以达到1 GB/s。对于外部DDR2而言,包括采集写入DDR2、发送读取DDR2、叠加读写DDR2,DDR2的理论带宽为2.5 GB/s,通过实测大于1.5 GB/s,单个功能带宽可以达到500 MB/s。对于图像大小为0.5 MB(512*512*16 bits),帧频为100帧每秒而言需要的总的带宽为150 Mb/s。这些数据表明硬件结构满足访问L2RAM和DDR2的最大带宽要求。从DSP端来看,高效率的存储器也在物理上保证了图像采集、处理、发送的并行执行。

接收数据时,播放器将从光纤接口读取数据并传输到FPGA的GTP模块,图像数据接收控制逻辑再将GTP数据解析缓存到内部FIFO中,然后通过SRIO控制器,将FIFO内部的数据传输到DSP的内部RAM中,并在传输一定的数据量后发送中断到DSP端口通知数据到达,DSP在收到通知中断后,从内部RAM中把数据传输到外部DDR2存储器上,在一帧时序内,将每次的数据组合成一幅完整的图像并缓存在DDR2上。发送图像数据时,播放器首先从DSP的DDR2空间把数据传输到内部RAM上,再通过SRIO端口,把数据发送到FPGA的内部FIFO中,FPGA的FIFO在达到一定的数据量后自启动读取操作,从FIFO中输出数据到GTP端口,通过GTP把数据发送到光纤接口上,最终实现了图像数据的发送。

4 结束语

本文设计了一种采用FPGA和DSP技术实现的红外仿真图像高速实时数据流播放器,用于光电经纬仪红外仿真系统的虚拟目标与真实背景图像的实时融合处理,实现了高带宽、高帧频、高分辨率的图像流数据的实时输出,解决了仿真目标与真实背景融合的大数据量运算问题。在实际应用中,取得了较好的视觉效果,该技术能够广泛应用于其他光学仿真系统。

参考文献:

[1] Gonzalez R C, Woods R E,阮秋琦,等译. Digital Image Processing /数字图像处理[M]. 北京:电子工业出版社,2002.

[2] 于正林,谭 微,姜 涛.飞行目标跟踪训练视景仿真技术研究[J].计算机仿真,2011,28(4):379-383.

[3] 王习文,陈 娟,王秋平.基于视景仿真的光电经纬仪模拟训练器[J].吉林大学学报(工学版),2011,41(2):509-513.

[4] 王习文,陈 娟,王秋平.光电经纬仪跟踪飞行目标的一种仿真方法研究[J].计算机仿真,2009,26(4):38-42.

[5] 田 耕,徐文波.Xinlinx FPGA开发实用教程[M]. 北京:清华大学出版社,2010.