基于FPGA的TCP/IP网络通信系统的设计与实现

2018-04-13王文郑建生

王文 郑建生

摘 要: 针对纯软件实现网络通信时必须依赖于操作系统,且易受攻击的缺点,基于FPGA技术,通过控制W5500协议栈芯片的方式设计并实现一个TCP/IP网络通信系统。该系统加入网络断线自动重连功能,并在系统中使用CRC冗余差错检验对数据进行甄别,实现对非法数据的滤除。介绍系统的设计方案,并对系统进行了测试,系统的评价指标为丢帧率、误码率和传输速度。测试结果表明,该系统能对数据进行准确无误的传输,且数据传输速率较高。

关键词: FPGA; TCP/IP网络通信; W5500协议栈; CRC校验; USB; 误码率

中图分类号: TN915?34; TN91 文献标识码: A 文章编号: 1004?373X(2018)08?0005?05

Abstract: In allusion to the disadvantage that the pure software must rely on the operating system for network communication implementation, and is prone to attack, a TCP/IP network communication system based on FPGA technology is designed and implemented by using the pattern of controlling the W5500 protocol stack chip. In the system, the network disconnection automatic reconnection function is added, and the CRC redundancy error check is used to discern the data and achieve the filtering of illegal data. The design scheme of the system is introduced, and the system is tested with the evaluation indexes of frame loss rate, bit error rate and transmission speed. The test results show that the system can transmit data accurately and the data transmission rate is high.

Keywords: FPGA; TCP/IP network communication; W5500 protocol stack; CRC check; USB; bit error rate

目前网络通信在各个领域应用广泛。网络通信使用的协议一般有TCP/IP协议和UDP协议两种。工程运用中,实现网络通信有两种形式,一种是通过纯软件实现,一种是通过硬件实现。纯软件必须依赖于操作系统,容易受到攻击。相对而言,硬件实现直接基于状态机对数据处理,安全性能更好,并且方便从最底层对数据进行甄别。本文设计并实现了一种基于FPGA的网络通信系统[1],该系统使用协议栈芯片W5500[2]实现TCP/IP网络连接,并对数据添加CRC冗余校验以去除非法数据,系统通过USB数据线与上位机進行通信。本文详细介绍了系统的设计和测试,并对测试结果进行了分析。

1 总体设计方案

本系统由USB模块、CRC校验模块、W5500网络模块组成,各大模块之间使用FIFO[3](First Input First Output)存储数据。在发送部分,上位机通过USB发送数据到FPGA,FPGA对数据进行CRC计算,将计算得到的CRC校验码添加在数据帧后面,然后通过W5500芯片数据发送到阿里云服务器。在接收部分,W5500芯片收到数据存储到FIFO中,FPGA数据进行CRC校验以判断数据是否正确合法,将通过校验的数据通过USB发送到上位机,丢弃没有通过校验的数据。系统总体框架图如图1所示。

2 模块设计

2.1 USB模块

USB模块选用的芯片是CY7C68013,传输模式采用批量传输[4]。批量传输使用批量事务传输数据,适用于数据量很大的场合。USB模块包含固件程序和FPGA控制模块。固件程序用来与上位机进行数据传递,固件设定了USB端口的个数和大小。本系统采用两个三层缓冲的2号和6号端口。2号端口用来发送数据,6号端口用来接收数据。FPGA控制用来协调2个端口的工作模式,因芯片的数据线是16位,需要用片选使能控制2个端口。USB芯片与FPGA的连接图如图2所示。

当FLAGA信号为低电平时表示EP2中收到了上位机发送来的数据,将数据读取到存储区中,供下一个模块使用。

FLAGC信号为低时,表示USB模块此时可以向上位机发送数据。USB模块发送和接收部分使用同一组数据总线和地址总线,数据总线是双向的。通过SLOE控制其传输方向。另外CY7C68013的工作机制是当EP6缓冲区中存满512 B(该值可以根据端点缓冲重数改变)的数据时,芯片才会将数据发送到上位机[5]。实际应用中的数据往往是有一定的存储结构,需要将一帧数据完整地发送到上位机。因此使用图2中所示的PKTEND信号,将该信号拉低,便可以将EP6缓冲区中的数据以一整帧发送出去。

2.2 CRC模块

CRC校验[6](循环冗余差错编码)由于其抗干扰能力强、便于对数据校验,因此广泛用于数据差错检测中。CRC校验的基本思想是将发送端要传输的m位二进制数据,以二进制除法生成一个r位的校验码,附加在信息后面。当接收方接收到数据,以同样的方式对其进行计算校验码。将计算得到的检验码和收到的校验码进行对比,相同则数据无误,反之说明数据传输出错。

模块中使用IP核生成的只读ROM来存储生成好的查找表,使用IP核生成的双口RAM来存储一整帧数据,整个CRC校验的流程图如图3所示。

CRC校验的实现一般有逐位运算法[7]和查表法[8]。相比较而言,在FPGA中,同一个时钟下查表法速度更快,占用的时钟周期更少。原因是查表法提前根据校验多项式,将需要的数据提前计算好,在计算CRC校验码时便可以进行直接使用,以此来减少运算时间。

本系统中选用基于查表法的CRC32校验,对应的校验多项式为:

当系统发送数据时,需要对数据添加CRC校验码,首先从FIFO中读取一整帧数据,存储到双口RAM中并且记录数据帧的长度;初始化CRC寄存器,CRC高8位于数据位进行异或得到索引表地址;从ROM中读取索引表值,CRC寄存器左移8位;与索引表值进行异或运算,根据数据帧的长度确定是否运算完毕。计算完毕之后,将CRC校验码添加在数据帧后面,将数据传递给下一个模块。

在本文所述系统中,在处理发送数据时向数据帧末尾添加CRC校验码,处理接收数据时将数据帧进行CRC校验,将通过CRC校验的数据通过USB传输到上位机,没有通过校验的数据视为非法数据,直接丢弃即可。基于这种方式一定程度上保证了系统传输给上位机的数据的安全性。

2.3 W5500网络模块

2.3.1 W5500芯片

W5500是Wiznet公司生产的一款以太网协议栈芯片,支持固件TCP/IP协议。高速网络数据传输,速率可达到50 Mbit/s;支持混合网络TCP/IP协议栈;可根据端口通信数据吞吐量动态调整内部TX/RX存储器的分配;内嵌10BaseT/100BaseTX的以太网物理层;支持自动握手。W5500与外围设备采用总线连接方式[9],通过地址总线和数据总线对芯片各个寄存器进行处理,这使得使用W5500进行以太网接口的开发更加方便。

2.3.2 W5500硬件接口设计

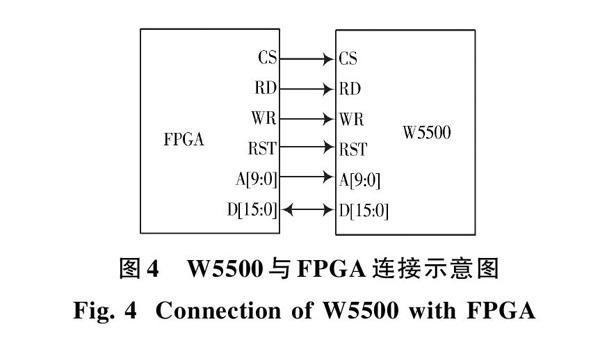

W5500芯片与FPGA的连接示意图如图4所示,发送和接收数据使用同一组地址总线和数据总线。信号线包括片选CS、读使能RD、写使能WR、复位RST、10位的地址总线以及16位的数据总线。

2.3.3 W5500模块逻辑设计

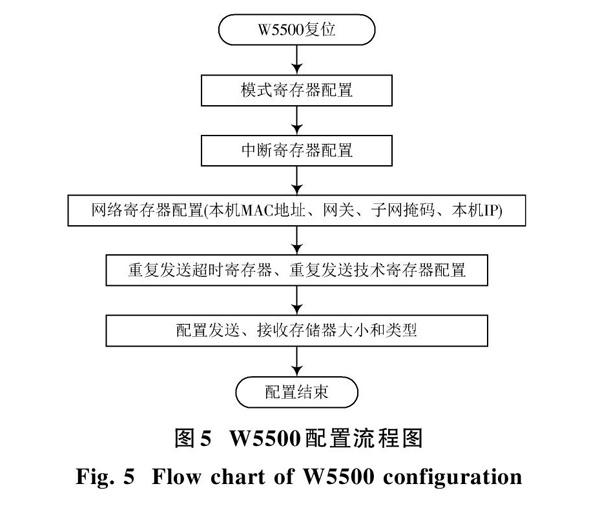

该模块从逻辑上可以划分为2个部分,即芯片配置和数据的接收和发送[10]。芯片配置主要分为芯片的初始化、模式寄存器配置、中断寄存器配置、网络寄存器配置、重复发送和超时寄存器配置、发送和接收存储器大小和类型配置,配置流程图如图5所示。

1) W5500复位

W5500由于不支持上电自动复位,因此需要手动复位。根据芯片手册,复位信号低有效且需要至少持续2 μs。本系统使用的时钟为50 MHz,根据计算复位信号需要保持低电平100个时钟周期,此外复位信号恢复高电平至少保持10 ms使锁相环逻辑稳定。

2) 模式寄存器

模式寄存器可以设置W5500芯片的工作模式,例如接口模式、存储器的地址访问模式等。

3) 中断寄存器

W5500芯片中各个事件的发生是以产生相应的中断进行标示,初始化阶段需要进行配置。

4) 网络寄存器

此部分配置包含本机MAC地址、网关地址、子网掩码和本机IP地址。

5) 重复发送计数和超时寄存器

重复发送超时时间的值决定了TCP模式下重新发送的时间周期,当系统重复发送计数寄存器的值,将产生超时中断。

6) 发送和接收存储器

设定发送和接收存储器的大小和类型。

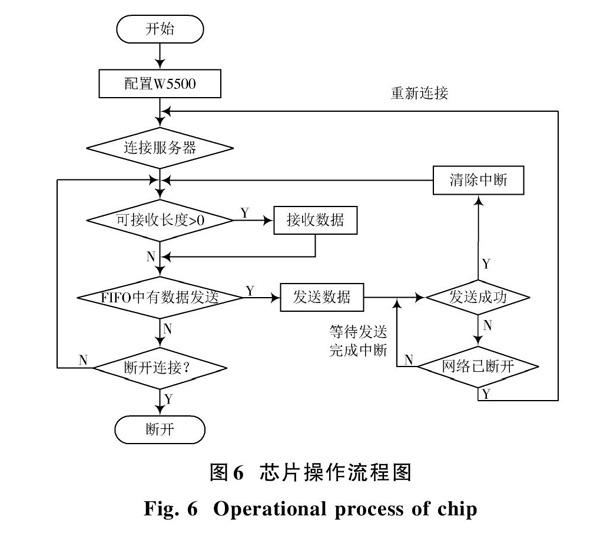

当W5500工作在发送状态,首先访问socket1的剩余空间寄存器,判断手否足够容纳一帧的数据。剩余空间大于一帧数据长度则将一帧数据写入到发送TX存储器,然后将数据帧的长度写入长度寄存器S1_TX_WRSR,最后执行发送命令。发送和接收数据逻辑流程图如图6所示。

根據芯片手册可以查询到发送命令为0x10,将其写入命令寄存器S1_CR。执行发送命令后,检测socket1的中段寄存器是否产生发送成功中断,当SEND_OK为0x10表明发送成功,则清除中断。

若没有发送成功说明此时数据发送出现了问题,检测socket1状态是否为关闭状态(CLOSED),若关闭需要进行重新连接。在实验中发现,在一些移动信号较差的地方进行测试时,发现在极少数情况下网络会断线,因此断线重连对于设备的可靠性至关重要。

当W5500工作在接收状态,接收过程相对而言操作更为简便。首先判断接收长度寄存器S1_RX_RSR,如果长度大于0,意味着接收到了数据,则读取出接收RX存储器中的数据,最后执行接收完成命令。

由于W5500芯片发送和接收共用一组数据线和地址线,因此需要不停地进行发送和接收的状态转换。

3 测 试

以上介绍了系统的设计方案和各个模块的实现。为了验证系统是否能够正常工作,对系统进行了测试。主要测试指标为:数据的传输速率;丢帧率;误码率。

测试方法为黑盒测试。首先,上位机生成固定格式的数据,每一帧数据都有计数,然后发送给FPGA,FPGA将数据发送给服务器,与此同时上位机从服务器接收数据,对收到的数据进行统计,计算出设备传输速率、丢帧率和误码率。硬件实物图如图7所示(本文描述的是硬件实物图中的一部分),测试软件截图如图8所示。

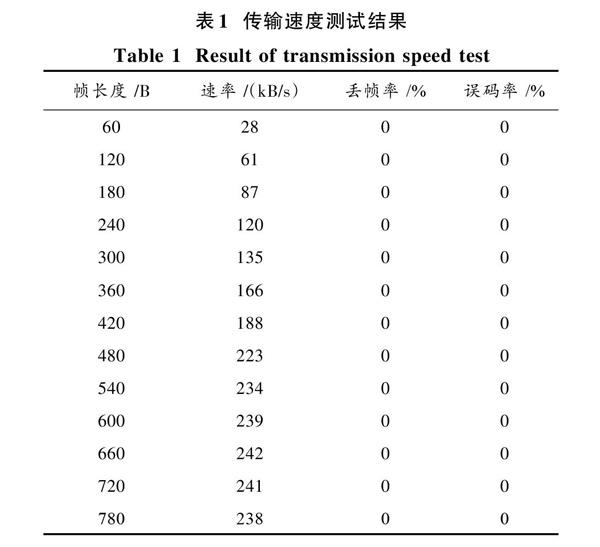

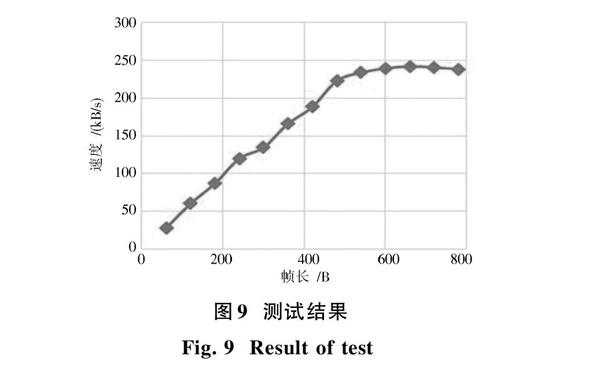

从表1中可以看出,丢帧率和误码率均为0,符合TCP传输的特性。在传输速度上,在未达到最大的传输速度之前,传输速度和帧长之间近似呈现线性关系。当达到最大速度后,速度将不再随帧长的速度变化。因此在实际工程中相同的网络环境下,设定一个合适的数据帧长度很重要,数据帧长度太小則会影响数据传输速度。

当数据帧的长度不同时,对应的速度如图9所示。

本系统服务器带宽为2 Mbit/s,因此理论的最大传输速度为256 kB/s,本次测试中最大速度为242 kB/s,比较接近理论的最大值。可见本系统基本达到理论最大传输速度。若提高服务器带宽,速度将进一步提升。

4 结 语

本文详细介绍了基于FPGA的TCP网络通信的设计方案,并在系统中添加了CRC校验对数据进行合法检测,避免了非法数据进入。在网络环境较差,网络断开时会自动检测网络连接状态实现自动重连,系统更加适应复杂的网络环境。相对纯软件网络通信,基于FPGA的网络通信在数据的安全性上更具优势,FPGA通过时序对数据进行控制,加强了通信系统的安全性。本文描述的方案在项目中达到系统要求,但是在通信速度上仍然有提高的空间,在数据安全上也可以考虑对数据进行加密传输。

参考文献

[1] 杨光阳.基于FPGA的硬件千兆网络通信设计[D].成都:电子科技大学,2015.

YANG Guangyang. FPGA?based hardware Gigabit network communications design [D]. Chengdu: University of Electronic Science and Technology of China, 2015.

[2] 曾红,党盼盼.基于W5500的嵌入式系统以太网网关设计[J].网络安全技术与应用,2015(2):36?37.

ZENG Hong, DANG Panpan. Design of embedded system Ethernet gateway based on W5500 [J]. Network security technology and application, 2015(2): 36?37.

[3] 黄凡.一种基于FPGA的异步FIFO设计方法[J].微处理机,2017,38(1):23?26.

HUANG Fan. A design method of asynchronous FIFO based on FPGA [J]. Microprocessors, 2017, 38(1): 23?26.

[4] 刘志华,郭付才,彭新伟,等.基于CY7C68013A的FPGA配置和通信接口设计[J].电子技术应用,2013,39(2):18?21.

LIU Zhihua, GUO Fucai, PENG Xinwei, et al. FPGA configuration and communication interface design based on CY7C68013A [J]. Application of electronic technique, 2013, 39(2): 18?21.

[5] 赵静,马尚昌.基于CY7C68013的USB 2.0通信接口的设计[J].微型机与应用,2015,34(22):61?63.

ZHAO Jing, MA Shangchang. Design of USB2.0 communication interface based on CY7C68013 [J]. Microcomputer and its applications, 2015, 34(22): 61?63.

[6] 常天海,胡鉴.基于FPGA的CRC并行算法研究与实现[J].微处理机,2010,31(2):45?48.

CHANG Tianhai, HU Jian. Research and implementation of CRC parallel algorithm based on FPGA [J]. Microprocessors, 2010, 31(2): 45?48.

[7] 周亮,余小平.基于FPGA的循环冗余校验码设计[J].电子世界,2015(14):154?155.

ZHOU Liang, YU Xiaoping. Design of cyclic redundancy check code based on FPGA [J]. Electronics world, 2015(14): 154?155.

[8] 张焱,任勇峰,齐蕾,等.基于FPGA的CRC校验算法的实现[J].电子器件,2015(1):222?226.

ZHANG Yan, REN Yongfeng, QI Lei, et al. Realization of CRC checking algorithm based on FPGA [J]. Chinese journal of electron devices, 2015(1): 222?226.

[9] 夏忠海,任勇峰,贾兴中,等.基于FPGA的CRC查表法设计及优化[J].电测与仪表,2017,54(3):54?59.

XIA Zhonghai, REN Yongfeng, JIA Xingzhong, et al. Design and optimization of CRC look?up table method based on FPGA [J]. Electrical measurement and instrumentation, 2017, 54(3): 54?59.

[10] 白佳俊,孟祥勇,张德平,等.基于W5500和FPGA的实时数据采集系统设计[J].电子技术应用,2013,39(4):19?21.

BAI Jiajun, MENG Xiangyong, ZHANG Deping, et al. Design of real?time data acquisition system based on W5500 and FPGA [J]. Application of electronic technique, 2013, 39(4): 19?21.