基于FPGA的星载一体化高速数据复接器设计

2018-04-07许志宏董振兴安军社

许志宏 ,董振兴 ,安军社

(1.中国科学院国家空间科学中心北京100190;2.中国科学院大学北京100190)

随着我国先导科学卫星任务的展开,空间科学已由最初的实验阶段逐步迈入应用阶段,一方面,单个科学卫星的空间任务越来越复杂多样,与任务需求对应的有效载荷的数量也随之增多,载荷数据量和速率大幅攀升;另一方面,科学卫星发射密度逐年增加,星上产品需求量也随之加大,卫星建造成本和研发周期的不断被压缩。如何在短时间内完成具有高可靠性,低成本和复杂功能的卫星设计和建造任务,成为了目前我国航天领域科研单位急需解决的难题。

针对这个难题,文中提出一种基于FPGA的高速数字复接器设计,应用在一体化星载高速数传系统上,相比传统复接器速度偏低、应对任务类型单一,通用性较差等缺点,该方案实现了载荷数据接收合路器、NAND flash大容量存储控制器、数据复接器和信道LDPC编码器一体化的集成设计,外部通用高速接口采用LVDS接口,控制总线协议采用1553B总线协议,数据传输格式协议采用CCSDS AOS的网络层协议,标准协议的使用和功能的高度集成化能够使该设计应对多类型任务,并大幅降低星载数传系统开发周期和成本。

1 系统总体设计

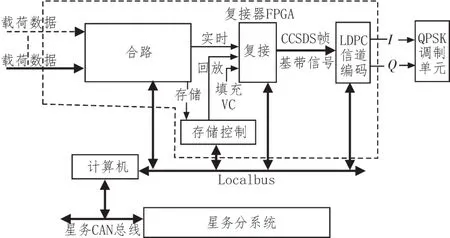

1.1 一体化高速数据处理系统

高速数据复接器系统应用在星载高速一体化数据处理平台中,该数据处理平台接收来自载荷的科学图像数据、遥测数据以及工程参数数据,并将接收到的数据按照实时和延时数据分类,延时下传数据由合路器进行预先处理后存入大容量固态存储中。卫星在轨运行过程中,复接器等待计算机回放指令,收到回放指令后,进行数据回放,经复接器组成符合CCSDS AOS格式的传输帧,作为基带信号经过LDPC信道编码和加扰处理,处理后数据通过X波段QPSK调制单元调制后输出至功放器[2-4]。系统结构见图1。

图中虚线框内为本文提出的基于FPGA的高速数据复接器。整个数据处理系统由计算机控制单元、合路复接与存储控制单元、LDPC信道编码单元及QPSK调制单元等部分组成。复接调制器上电时接收载荷数据。载荷的主备通讯接口与复接调制器的主备机实现主备交叉通讯。

图1 一体化数据处理平台总体结构图

1.2 高速数据复接器系统

通用复接器主要包括通用数据合路与预处理模块、大容量存储控制模块、数据复接模块和信道编码模块组成,系统结构图见图2。目前该复接器入口包括16路LVDS、8路RS-422、8路UART和4路OC门,都为常用卫星数据传输系统接口,数据输入理论带宽为1 Gbps,入口各路数据速率能够做到可预先配置,可按照具体工程需求分配各路输入数据的速率,具有较高的灵活性。在外部控制总线通讯接口上该系统支持MIL-STD-1553B总线协议。

系统工作流程:外部数据接收接口主要包用来接收载荷数据。当数据进入合路单元后进行数据的打包处理预处理,将多路数据进行合路,处理后数据经过NAND flash存储控制器进入存储,形成延时数据,待星务计算机发送数据回放指令后,将延时数据读出存储区进入数据复接器,按照CCSDS AOS传输帧格式进行组织传输帧操作,帧数据经LDPC(8192,7154)编码后分为I和Q两路串行输出到下级调制器。整个系统设计指标为:入口瞬时速率为1 Gbps,存储容量为512G位,下行编码速率为400 Mbps[6]。

图2 复接器系统结构图

2 关键技术

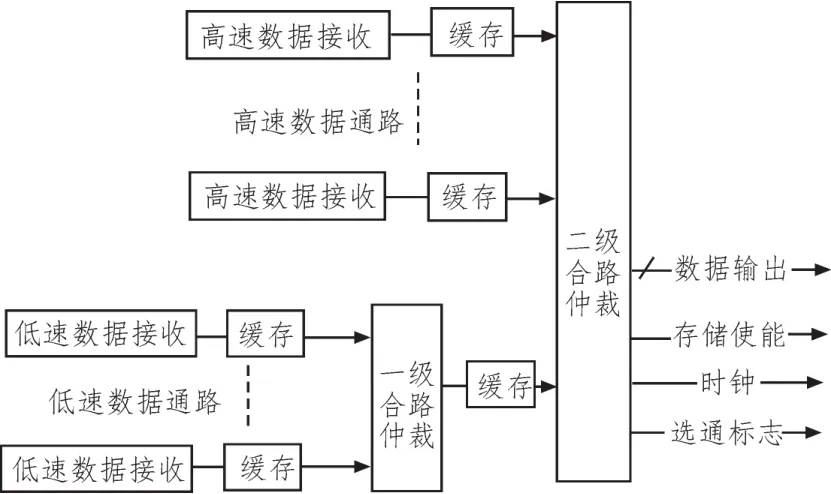

2.1 数据接收与分级合路

数据合路和预处理控制模块主要完成载荷数据的接收功能和遥测源包打包功能,并且按照载荷的数据速率将载荷数据分为快速通路和慢速通路,实现分级缓存和分级合路总裁,低速通路按照252字节的长度进行遥测源包打包,高速通道按照1 008字节的长度进行遥测源包打包,低速通道数据满4个短包后组合成一长包对二级仲裁器发出占用数据通路请求,采用这种方式关键在于合理地分配高速与低速数据流占用物理信道的比率,必须根据数据源

个数以及数据流总数据率之比来确定。使用混合多路复用的方法,既能满足等时数据的固定时隙要求,又适应各数据源数据量的调整,以防止慢速通道过度占用数据通道,降低数据传输效率,具体原理与模块结构[5]见图3。

图3 分组合路调度原理图

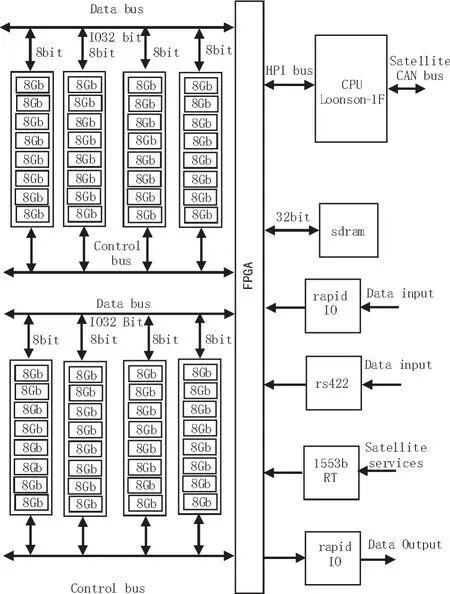

2.2 大容量NAND flash存储控制

星载大容量固态存储控制器与存储控制CPU运行基于VxWorks操作系统的嵌入式存储管理应用软件进行软硬件协同工作,对固态存储空间完成动态拟文件化管理,工作方式为中断方式,应用软件根据存储控制器中断状态向FPGA发送相应操作指令。FPGA完成对存储器件的控制功能,通过对CPU应用软件的指令解析,完成对存储介质的读写操作、擦除操作和存储坏块维护等功能。

存储系统所使用的存储介质为3DPLUS公司的64 Gb(8×8 Gbits)宇航级NAND flash叠装器件,该器件由8片8 G位(1G×8 bits)的NAND flash芯片叠装而成,采用 SIP(System In a Package)封装方式。Flash芯片最大工作时钟频率为40 MHz,根据在空间应用中的不同环境温度条件下信号满足芯片的建立保持时间的要求以及80%的设计降额要求,存储系统工作时钟频率设定为32 MHz,存储介质数据总线采用32位(4芯片)并行扩展,数据写入采用4级流水方式,以提高写入效率,吞吐率理论峰值速率为1 Gbps,实测平均有效速率为700 Mbps。容量为512 G位。整个存储硬件系统在6U的PCB单板上集成,单板对外低速控制接口采用通用1553B总线接口,作为载荷单机总线网络的远程终端,并能与星务分系统进行通信。高速数据输入和输出接口采用rapid IO协议,物理层使用 LVDS(Low-Voltage Differential Signaling)接口[7-8,10]。

图4 容量固态存储控制系统结构

2.3 复接模块虚拟信道调度机制

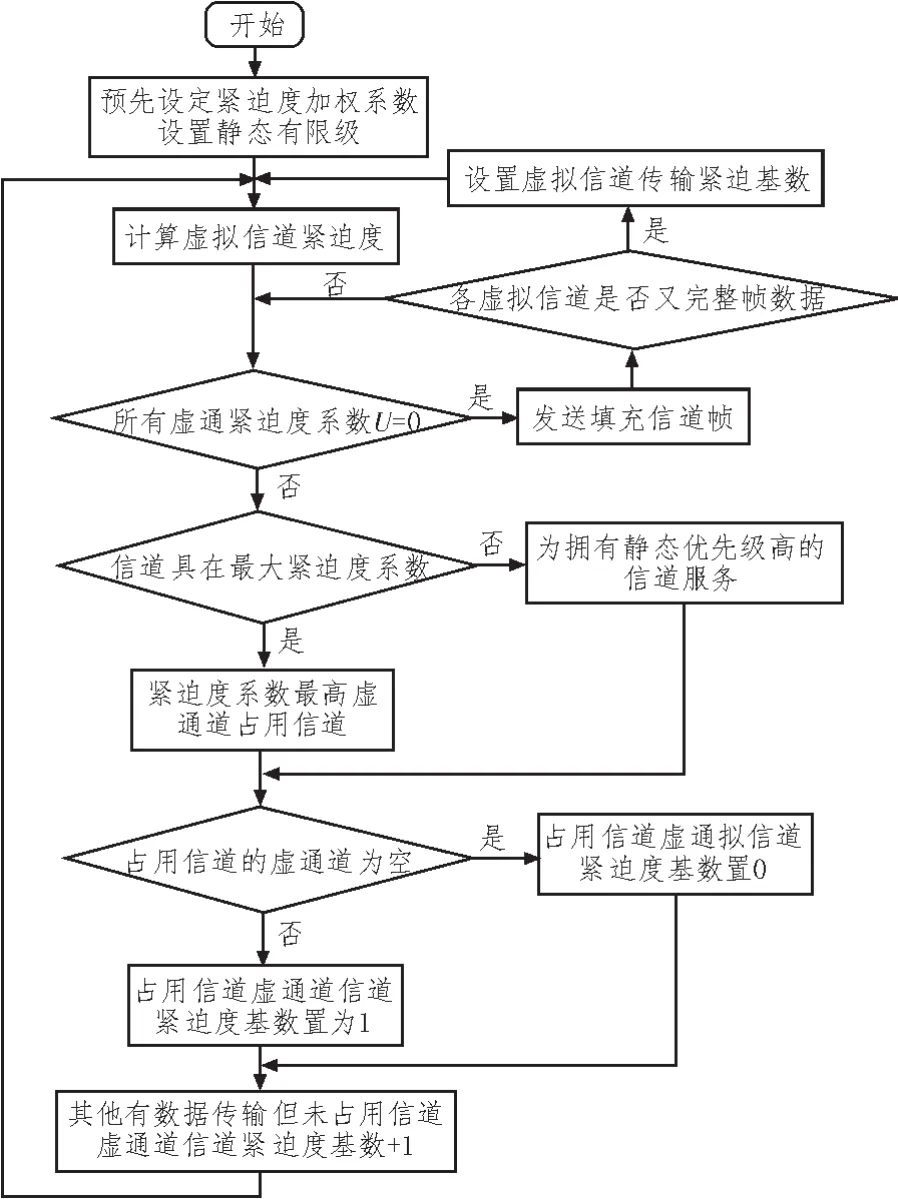

由于复接控制模块支持支持16路虚拟信道调度,优秀的信道优先级的调度策略能够提高在有限的下传带宽中的信道传输效率,还能防止数据丢失,CCSDS AOS推荐虚拟信道的调度策略主要包括:静态调度、动态调度和混合调度策略,一般虚拟信道优先级调度算法主要包括:先来先服务算法、静态固定优先级的调度算法,轮询调度算法(roundrobin),剩余量优先级调度算法等,这些算法在不同应用场景下各有优缺点,文中采用一种基于紧迫度的改进型轮询调度算法[9],算法主要思想:动态优先级调度需要考虑虚拟信道中的两个状态参数:传虚拟信道传输紧迫度基数(trans urgency)BTU与传输紧迫度加权系数(trans urgency weighting)WTU。传输紧迫度基数BTU是指一个虚拟信道从申请传输时刻开始到该虚拟信道被调度时刻的延迟,其取值是实时变化的,其取值方式如下:

1)当虚拟信道中没有完整的传输帧时,该虚拟信道的传输紧迫度基数为0;有完整的传输帧时,其传输紧迫度基数为1。

2)当虚拟信道中有完整的传输数据帧而没有得到传输时,每延迟一个调度时刻,传输紧迫度基数加1。

3)当一个虚拟信道被调度后,若该虚拟信道中还有完整的数据帧时,紧迫度基数自动降为1;若该虚拟信道中没有完整的数据帧时,紧迫度基数自动降为0。

传输紧迫度加权系数WTU取值为该虚拟信道的静态优先级,信道传输优先级越高,WTU取值越大。定义第i个虚拟信道的传输综合紧迫度Ui为:

其中BTUi和WTUi分别为第i个虚拟信道的传输紧迫度基数和传输紧迫度加权系数。

具有最大紧迫度系数的虚拟信道优先级最高,按照传统的轮询调度机制,当虚拟信道传输完后无论信道缓存中是否还有数据,其优先级降为最低,即WTU置0,这样在下一个调度判断时间到来时,该信道将不会被调度,这样对信道公平性产生影响。因此信道优先级的排序依据信道综合紧迫度大小来决定,算法原理图见图5。

图5 基于紧张度的虚拟信道调度算法

2.4 并行低功耗LDPC信道编码

CCSDS采纳LDPC码为近地空间和深空探测的信道编码标准,并推荐7/8码率LDPC码作为近地空间信道编码方案。传统串行编码方式使用寄存器搭建运算矩阵,当高速数传工况下,矩阵运算所产生功耗大幅上升,无法应用于卫星高速数传平台,针对运算矩阵实现手段方面,本文设计中使用在待编码信息位数据中插0和改变校验矩阵结构的方法形成LDPC(8192,7154)码字,并使用循环移位寄存器组的方式来实现LDPC编码,使用大小为511x511的校验矩阵子矩阵,并且实现两路数据奇偶位并行编码运算,在保证码率不变的前提下,降低寄存器资源开销,并提高了运算效率,并行LDPC编码电路结构图见图6。

图6 并行低功耗LDPC编码电路结构

循环移位寄存器的移位值范围从0到510之间,每次移位都由移位控制器进行控制,根据移位控制器输出的控制信息进行乘加操作。在编码过程中,7154位有效信息数据经插0操作后拓展到7168位,插0后数据分为14组,每组512位待编码数据,经矩阵运算电路编码后,生成8192位的编码码字。

3 验证与实现

原理样机应用场景为卫星平台数据传输系统数管单元,本设计已经在原理样机上进行验证,原理样机电路板外观见图7。

图7 原理样机图

根据应用系统结构,搭建了一套完整的地面测试系统,在该测试系统下,对设计进行包括热真空在内的大量环境适应性测试以及最大工况的强度测试。整个地面测试系统包括:1)载荷数据模拟单元,该单元用来模拟5路高速相机和卫星遥测工参数据数,入口码速率为550 Mbps;2)待测数管分系统单机,包括了载荷管理模块,大容量存储系统模块,加密和射频QPSK调制模块;3)地面应用模拟系统,包括星务模拟系统和信号解调设备。4)地面应用系统,主要完成数据的解码、解帧、解包和原始有效数据的比对;5)数据处理终端,主要完成系统控制指令序列自动化测试,以及对测试数据的记录归档。经过测试,所有接收到的传输帧格式符合CCSDS AOS建议,帧同步字、帧头,帧长度、插入长度、遥测数据包长度都和设定相符。填充数据、插入业务数据、虚拟信道调度功能,虚拟信道计数连续,复接器工作时不丢数、不丢包,入口有效的数据接收码速率不低于700 Mbps,出口速率达到400 Mbps。

4 结论

该设计采用FPGA平台[17-18]实现硬件功能,系统内部设计也考虑了EDAC和定时刷新等抗空间单粒子效应措施,具备较强的鲁棒性。并且已在原理样机上进行验证,性能指标能满足设计预期,能够满足多种卫星数传要求,通过与国内外已成功应用的类似系统的横向比较,该系统的各项功能和性能指标达到相近水平。但在星载数据并行处理,图像压缩处理,输入数据接口通用性,总线接口种类,存储整列容量和速率等方面可进一步地提升,可满足未来更加复杂航天器数据处理需求。

参考文献:

[1]CCSDS 701.0-B-3, Blue Book, Issue 3,Advanced Orbiting Systems,Networks and DataLinks:Architectural specifications[S].2001.

[2]CCSD S 1 33.0-B-I.Space Packet Protocol[S].September 2003.

[3]戴晔.AOS高速多路合路器的研究[D].上海:上海交通大学,2009.

[4]John Dickinson,Charlie Howard,Steven Torno.A High-Density,Non-Volatile Mass-Memory and Data Formatting Solution for Space Applications[C]//IEEEAC Paper 1575,Version 1,2009.

[5]司锋,张强.基于数据路由的星载高速数据处理系统研究[J].测绘通报,2014(S1):27-31.

[6]宋琪,邹业楠,李姗,等.卫星固态存储器数据容错设计与机制[J].国防科技大学学报,2016,38(1):101-106.

[7]郭柳柳,甄国涌,刘东海.基于FPGA高速图像数据的存储及显示设计[J].电子技术应用,2014,40(11):75-77.

[8]邹业楠,董振兴,朱岩.基于CFDP标准的空间数据链路传输协议软件实现[J].电子设计工程,2016(20):13-16.

[9]苏秀红,李春枝,申川.基于Nand Flash的高速存储器结构设计[J].电子设计工程,2014(23):4-7.

[10]马明晓,安军社.一组高效LDPC码空间通信方案设计与实现[J].电子设计工程,2014(6):99-102.

[11]刘庆利,潘成胜,王国仁,等.AOS虚拟信道/帧分离估算的调度算法[J].系统仿真学报,2013,25(1):87-93.

[12]宋琪,邹业楠,李姗,等.卫星固态存储器数据容错设计与机制[J].国防科技大学学报,2016,38(1):101-106.

[13]Dutta C,Lalitkrushna T,Jeeja K H,et al.CCSDS complied data handling system for mini satellite[C]//International Conference on Communication and Industrial Application.IEEE,2011:1-4.

[14]Chen D,Wilcox E,Ladbury R,et al.Heavy Ion Irradiation Fluence Dependence for Single-Event UpsetsinaNANDFlashMemory[J].2016,PP(99):1.

[15]宋琪,李姗,朱岩.星载固态存储器数据管理结构的设计[J].电子设计工程,2016(6):100-103,107.

[16]SamsungElectronics.K9F8G08U0M NAND Flash Memory datasheet(Revision1.1)[S].2012.

[17]胡雷钧,陈乃刚,李健,等.FPGA异构计算平台及其应用[J].电力信息与通信技术,2016(7):6-11.

[18]杨延飞,雷倩倩,王春兰.基于边界扫描技术的FPGA延时故障检测[J].纺织高校基础科学学报,2017,30(3):396-401.