相控阵天线校准单元高效代码实现技术研究

2018-04-02罗柳镇刘光祖孙琳琳

罗柳镇,刘光祖,孙琳琳

(南京理工大学电光学院,江苏南京210006)

校准单元是确保阵列天线[1-4]正常工作的重要组成部分。其主要工作就是对阵列天线每个阵元进行高精度的幅度和相位的测量。通常情况下使用FPGA加载特定的算法即可实现该功能。常用的XILINX或ALTERA公司的FPGA,其内部逻辑资源丰富,实现复杂的数字信号处理功能难度较小,但在宇航应用条件下,上述公司的FPGA存在较大的使用限制。文中将讨论使用ACTEL公司的反熔丝[5]的FPGA实现高精度幅相测量,反熔丝FPGA宇航环境适应能力强,但因为制造工艺不同,其规模相对较小,如SX-A系列A54SX72A。该芯片内部仅有6036个逻辑单元,而且没有内置乘法器。

仿真表明仅仅代码实现一个乘法器也将占用A54SX72A芯片将近12%的逻辑资源。测幅测相中包含下变频和低通滤波,这些都需要使用乘法器。传统方法编写的代码综合后使用的逻辑资源远超出芯片的实际逻辑资源,必须采用经过优化的测幅测相算法,在满足测量精度的前提下有效降低逻辑资源占用量。文中给出幅相测量的一种高效代码实现方法,重点论述了下变频,低通滤波和锁相环模块的高效代码策略。

1 传统幅相测量原理

假定整个单元由外部提供参考时钟40.92 MHz,A/D输入信号频率92.07 MHz,FPGA工作时钟40.92 MHz,均与外参考同源。整个单元没有额外的引入噪声,信号的信噪比非常高。测量采用数字检测和PLL结合的方案实现被测单频信号的幅相测量,设计的幅相测量方案如图1所示。

图1 幅相测量实现框图

采样后信号直接获取信号幅度,平方累加求均值。PLL[6-9]是本测量系统为保证相位精度而设计的反馈系统,在PLL设计中,首先是数字下变频,变频后的结果鉴相,输出经环路滤波器后控制NCO。当环路锁定时,NCO中的累加器的值即所求相位。仿真发现一个乘法器占用A54SX72A芯片将近12%的资源。上述算法需要使用多个乘法器。

2 幅相测量的高效代码设计

为了有效降低资源占用率,我们采用如图2所示结构实现幅相测量。

图2 幅相测量的高效实现结构

2.1 数字下变频模块的设计

常规的数字下变频需要一个NCO产生正余弦波和输入的信号分别相乘输出I,Q两路。NCO的频率是可控的。通过频率控制字实现。下变频目的是把信号变频到零频处理。显然在没有乘法器和逻辑之源少的ACTEL芯片中采用这种实现方案是不可取的。因为其所占的逻辑资源很多。

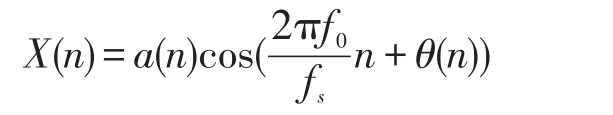

经过分析比较,选择采用免混频的下变频的算法。由于待测信号频率和采样频率符合的关系。其中fs是采用频率。f0是信号带宽中心频率。

设采样后信号为:

对输入的数据周期性的保持,取零,取反操作即可。节省乘法器和NCO资源。对于整个幅相测量单元来说,将省去了两个乘法器和一个NCO,逻辑资源占用率显著降低。

2.2 低通滤波器的设计

传统的FIR滤波器涉及一系列的乘法运算,直接采用的FIR低通滤波器显然不是最佳方法。本设计中提出采用半带滤波器。半带滤波器可以使2倍抽取乘法次数比一般线性相位的FIR滤波器减少1/2。

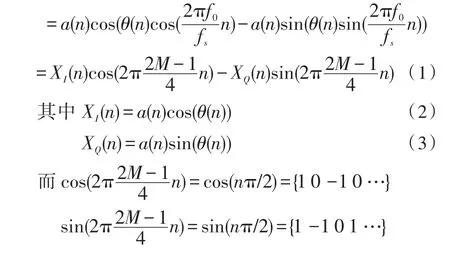

满足如下条件的FIR滤波器称之为半带滤波器:

1)δp=δs=δ(通带波纹等于阻带衰减)

2)wc=π-wA(通带带宽等于租带带宽)

半带滤波器有如下性质:

半带滤波器系数的对称性和近一半系数为0,使得滤波运算量大大降低。同时将乘法运算转换成移位运算。滤波器的系数设置成2的幂次方形式。这样就大大降低了运算资源。输入信号频率为92.07 MHz,采样时钟为40.92 MHz。半带滤波器截止频率为10.23 MHz,能够滤除高频分量。取7个滤波器的抽头 系 为 [-0.125,0,0.375,0.5,0.375,0,-0.125]。0.125和0.375,0.5都是2的幂次方形式。其幅频响应如图3所示。

由于信号信噪比较高,下变频后输出需要滤除主要是差频分量和和频分量,半带滤波器完全可以做到将和频分量滤除,达到低通滤波的目的。

由于测量时间充足,半带滤波器的设计采用串行的结构,这种结构对时序要求低,但运算时间相对较长,通过牺牲测量时间进一步降低资源占用率。

图3 设计的半带滤波器幅频响应

2.3 数字锁相环设计

采用了数字锁相环来实现高精度相位测量。锁相环[10-15]是一个相位的负反馈控制系统。锁相环的基本模块主要包括鉴相器(PD),环路滤波器(LF)和压控振荡器(VCO)。鉴相器的作用是提取输入信号和环路输出信号的相位差值。环路滤波器的作用是对鉴相器的输出信号进行环路的滤波,消除噪声。环路滤波器的输出电压控制压控振荡器输出一定频率的信号,锁相环不断调节压控振荡器频率直到能跟踪上输入信号的频率。早前锁相环的实现都是通过模拟电路来实现的,模拟锁相环也经过长期的发展已经成为相当稳定的一门技术。由于数字电路相对于模拟电路有着很多优势,所以锁相环多用数字电路实现,数字锁相环主要由数字鉴相器,数字环路滤波器和数控振荡器组成。

1)鉴相器

鉴相器的功能就是提取输入信号和反馈信号的相位差。一般由乘法器和低通滤波器构成。下变频输出的I,Q两路信号进入锁相环。一般用一个复数乘法器即可提取相位差。

由上式可以看出,只要将输入的复数信号和反馈回来的复数信号相乘取结果的虚部就可以提取相位差,为了节省逻辑资源不采用复数乘法器,而是使用两个乘法器和一个加法器获取复数乘法的虚部。

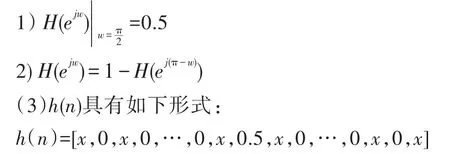

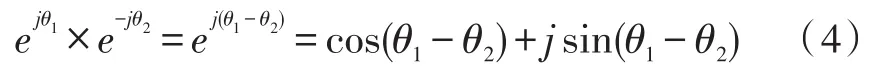

2)环路滤波器

数字环路滤波器是数字锁相环路中的一个关键模块,要实现数字环路滤波器,就必须找到将模拟滤波器映射到数字域的方法,其中最常用的就是双线性变换方法。双线性变换方法实现模拟系统与数字系统之间的转换十分简单,只需要直接应用下面的变换公式即可:

式中,T为数字采用周期,将上式带入模拟环路滤波器的传递函数中就可以得到数字环路滤波器的表达式,对于理想积分滤波器来讲,其数字化系统函数为

其中:

对于数字锁相环路来讲,显然关键问题在于设计C1和C2两个参数值。两个参数值直接决定了环路的性能。其实现结构如图4所示。

图4 环路滤波器结构

3)数制振荡器

数控振荡器是决定锁相环性能的主要因素之一,用于产生频率和相位的可控的正弦和余弦波。基于查找表方法设计NCO是最常用的方法。一般的查找方法是用两块ROM分别存储整个周期的正弦和余弦数值,根据相位累加器输出地址对ROM表进行查找。

如果f是时钟频率,也就是采样频率,则NCO的分辨率就是f/2n。基本原理就是输入的频率控制字在时钟的控制下进行一次一次的累加,而后把这个累加值作为正余弦查找表的查找地址,读出相应的值输出相位累加器主要作用就是对输入的信号进行累加,累加后的值输出作为查找表的地址。正弦查找表表中存储的就是正弦波形具体数字量化后的值,利用MATLAB编写程序生成一个周期的具体数值,而后编成一个COE文件存入ROM中。查找表取1 024个点存储,地址范围0到1 023,一个地址对应一个正弦波值。

而对于余弦查找表,余弦波形本来就是正弦波形前移1/4周期,所以为了节省硬件资源,只需要将查正弦波形的地址值加上256作为查找余弦波形的地址值即可。

充分利用正弦和余弦的对称性,设计中仅存储1/4周期正弦数据,余弦数据根据正弦数据位移得到,这种实现方法将减少占用FPGA约13%的的逻辑资源,实现的NCO与传统方法完全一致。

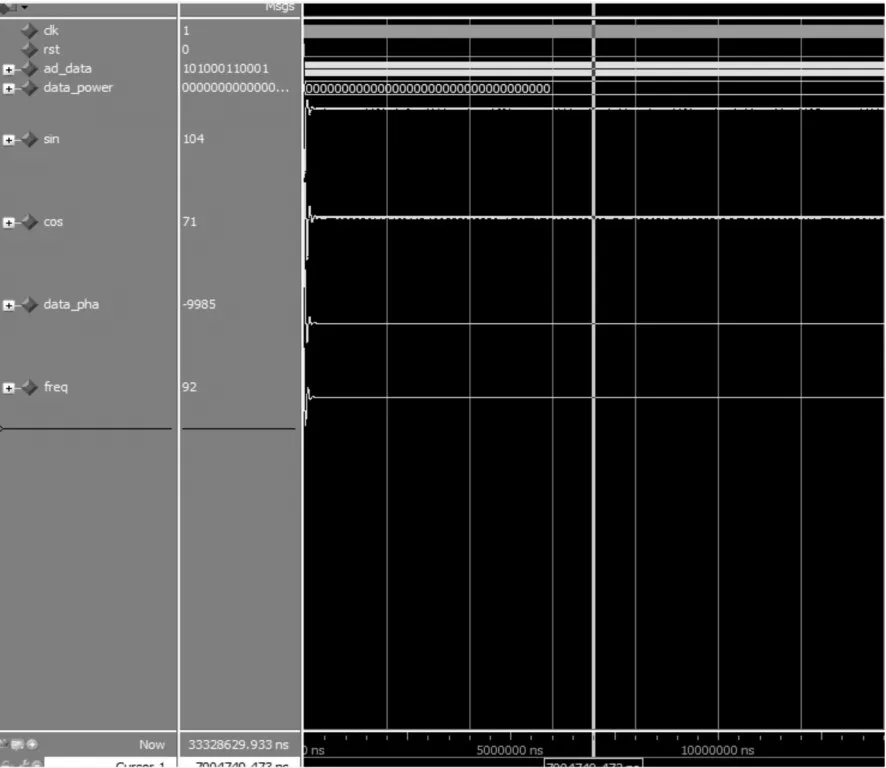

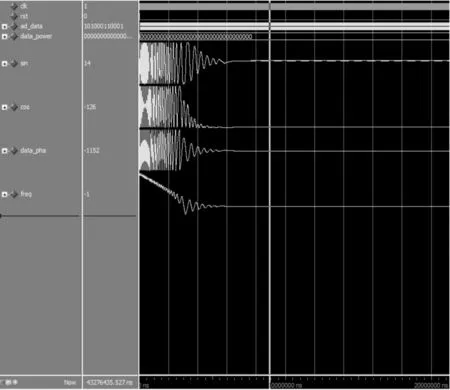

3 算法的仿真

基于上述设计实现代码,使用modesim-SE-64-10.1进行编译仿真。输入一个一定频率的单音信号,利用设计的算法对单音信号进行幅相测量。分别对传统的算法和优化算法进行仿真,输入条件相同。采用优化算法时,对于A54SX72A反熔丝FPGA来说,其资源占有率为77%。仿真结果如图5和图6所示。

图5 传统算法Modesim仿真结果

图6 优化算法Modesim仿真结果

图5和图6中除了时钟和复位信号外,从上而下依次为测量功率(data_power)、锁相环中的NCO的正弦波输出(Sin)、锁相环中的NCO余弦输出(Cos)、输出的测量相位(data_pha)。环路滤波器的输出(Freq)。

仿真的结果可以看出,两种方案锁相环最终都可稳定输出。但优化算法为了减少资源占用牺牲了运算时间,传统算法0.5 ms左右就开始收敛,优化算法在5 ms左右开始收敛。由于测量时间有一定余量,优化算法完全可以实现幅相测量并达到指标精度。

4 结论

在宇航应用背景下,充分利用反熔丝FPGA的宇航可靠性,通过算法优化在小规模反熔丝FPGA上实现高精度幅相测量,相比较传统算法,在不降低测量精度的前提下,资源占用率降低50%,整个设计单元体积、功耗显著降低,具有较强的工程应用价值。

参考文献:

[1]李阳,肖增利,孙芃,等.相控阵雷达捷联波束稳定方法[J].航空学报,2014,35(2):497-505.

[2]王春,吴楠,谢大刚.基于互阻抗原理的平面有源相控阵天线辐射近场计算方法:CN103678802A[P].2014.

[3]中秋.弹载有源相控阵雷达的应用[J].兵器知识,2016(2):54-57.

[4]余良壮.远程相控阵制导雷达调度研究[D].西安:西安电子科技大学,2012.

[5]张伟,杜涛,张国俊.反熔丝FPGA配置电路的研究[J].微电子学与计算机,2015(4):98-101.

[6]帅旗.基于FPGA的全数字锁相环的设计与实现[D].大连:大连理工大学,2013.

[7]王新浪.频率合成技术发展与应用[J].现代导航,2012,3(2):119-122.

[8]Won J H.A novel adaptive digital phase-lock-loop for modern digital GNSS receivers[J].IEEE Commu⁃nications Letters,2014,18(18):46-49.

[9]Mendel S.Phase-lock in all-digital phase-locked loops[M].US.2015.

[10]Balachandran G K,Petkov V P.Digitalphase lock loop circuit including finite impulse response filtering to reduce aliasing of quantization noise:US9246499[P].2016.

[11]Lin C L.Digital phase lock loop andmethod thereof[J].2015.

[12]刘丹丹.一种新型宽频域全数字锁相环的研究与设计[D].衡阳:南华大学,2015.

[13]Gupta A S,Hanjura A K,Mathur B S.Digital Phase Lock Loop for Tracking Very Low Frequencies[J].Iete Technical Review,2015,3(3):85-88.

[14]王华军.基于FPGA的新型全数字锁相环的设计与实现[D].成都:电子科技大学,2015.

[15]黄保瑞,杨世平.基于FPGA的全数字锁相环设计[J].电子测试,2014(16):33-34.

[16]罗宁,陈原聪,赵野.应用于全数字锁相环的高性能数控振荡器设计[J].微电子学与计算机,2015,32(12):59-62.