基于国产SOPC芯片BM3109工程设计研究

2018-03-02李云飞王建强宋景成

李云飞,陈 淼,王建强,宋景成,李 鹏

(山西银河电子设备厂,山西 太原 030006)

0 引言

在现代的武器系统、空间系统和飞行器领域,对控制系统的集成度、动态性需求日益增强,主控芯片作为整个控制系统的核心,正逐步由分离的元器件框架向高集成度的片上系统(SOC)发展,在功能复杂的应用场合,需要使用片上可编程系统(SOPC),来解决灵活的硬件接口设计、复杂的算法逻辑实现等功能。BM3109是一款国产的高动态、高性能、低功耗的SOPC芯片[1],通过将SoC硬件与可编程FPGA系统融合,实现系统的动态可配置和高集成度。对于高精尖领域核心模块的国产化设计,提供了芯片级的保证。本文从BM3109的硬件组成、软件架构设计、开发调试环境构建等方面入手,对基于BM3109芯片的国产化硬件平台工程解决方案进行探索研究。

1 BM3109 硬件组成

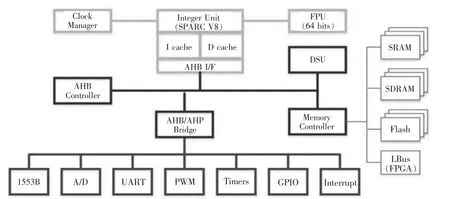

BM3109是国产的高性能SOPC芯片,由CPU处理芯片、可编程逻辑系统、多级存储器组成,系统构架如图1所示。CPU处理芯片采用SPARC-V8架构的32位微处理器BM3101,作为主控芯片,通过LOCAL-BUS总线与片上设备通信,实现整个系统的管理控制功能。BM3101芯片包含整数处理单元、浮点处理单元、独立的指令和数据Cache、中断控制器、DSU硬件调试单元、计时器、定时器和串口,支持PROM、SRAM、SDRAM和I/O映射空间访问的存储器控制器。可编程逻辑系统采用BQV300现场可编程门阵列,实现硬件接口设计及算法的实现功能。BQV300拥有30万门系统,工作频率支持到200MHZ,16-bit RAM、32-bit-RM 和16-bit双端口RAM,支持 slave-serial、masterserial、SelectMAP Mode、Boundary-Scan Mode 四种配置模式。存储器系统包括8M Byte FLASH、1 M Byte SRAM和16M Byte SDRAM,用于存放程序代码、用户数据等。

图1 BM3109系统构架示意图Fig.1 Architecture of general BM3109

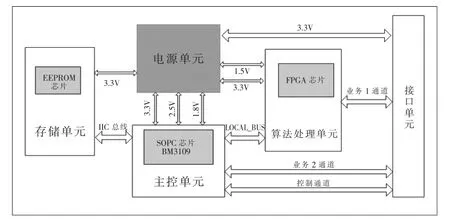

在工程设计中,增加复位电路、时钟模块、电源模块即可完成最小系统搭建,复位电路可选用MAX706芯片,时钟电路可选用25MHZ的外部晶体振荡器,电源电路可选用DC-DC芯片TPS54610,实现外设电压3.3V、内核电压1.8V、可编程逻辑器件2.5V的供电设计。根据工程设计需求,最小系统可以搭载高容量的可编程逻辑门阵列、CPLD芯片、FLASH 芯片、EEPROM 芯片及 MAX3232、MAX485、74ALVCH16245等电平转换接口芯片等,完成可裁减、可扩充、可升级国产高集成度嵌入式平台的搭建,如图2所示。

图2 硬件平台组成示意图Fig.2 Composition of whole hardware platform

2 软件构架设计

SOPC平台的处理器是基于SPARC体系的CPU芯片BM3101,软件架构包括启动引导段和用户程序段代码。启动引导程序类似于PC机的BIOS,完成系统初始化,使用汇编语言进行编写[2];用户程序存放在特定的存储空间,由启动引导程序搬移到RAM空间后开始运行,程序一般使用C语言进行开发设计。

启动引导程存放在BM3101处理的0X00000000地址处,系统上电后,程序从该地址开始执行,依次完成异常向量表的定义、堆栈初始化、系统硬件初始化、C程序运行环境初始化、跳转到用户C语言主程序。

用户程序根据软件需求进行编写,可以采用执行效率高的前后台程序设计模式,也可以基于VxWORKS系统进行开发设计。用户程序存放在BM3101处理器指定的FLASH地址空间,由bootloader搬移到RAM地址空间后开始执行。

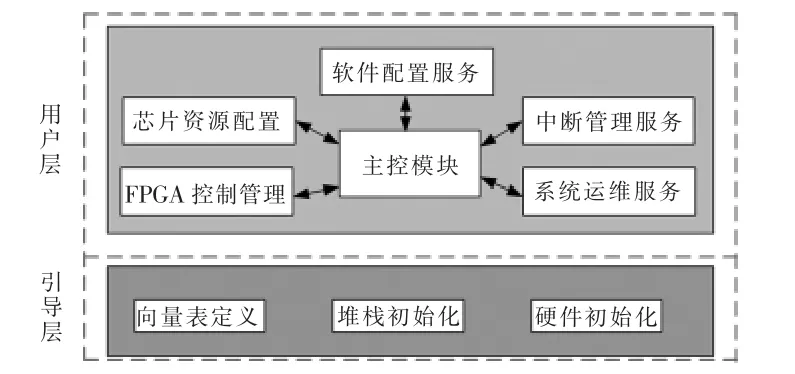

在工程设计中,用户程序一般包括主控模块、软件配置管理服务模块、芯片资源配置模块、业务管理服务模块、系统运维管理模块组成。在应用到FPGA功能的产品中,需设计FPGA控制模块管理模块,软件构架设计见图3。

图3 软件构架设计示意图Fig.3 Architecture of the standare software

3 开发调试环境介绍

BM3101处理器的开发调试工具包括SPE-C 2.55和GRMON[3]。SPE-C 2.55是针对C程序语言设计的一个完整的集成开发环境,运用GNU的整套集成开发套件作为编译/调试的核心,在Win32环境下使用,完成应用程序的开发和程序调试。GRMON是一款调试SPARC V8处理的汇编级调试工具,支持对系统寄存器和内存的读写访问,下载和执行LEON应用,断点和观察点管理。在实际软件调试过程中,往往将两者结合使用,使用SPE-C 2.55的用户界面完成源代码的编辑、编译,生成可执行代码,利用GRMON完成代码的下载与在线调试。

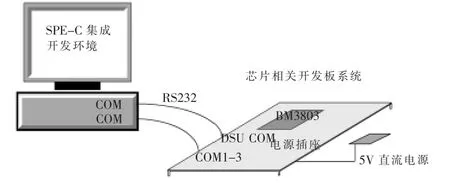

在工程设计中,完整的软件开发调试流程为:第一步,配置SPE-C工程选项,处理器型号选择BM3101,链接选项TEXT地址设置为0X40000000,该地址为用户程序的执行地址,其他选项默认即可;第二步,编写程序代码,以系统mould为基础建立新工程,根据软件需求,修改mian.c程序设计;第三步,按“编译”按钮完成C文件的编译工作;第四步,生成FLASH映像烧写文件,在Boot参数设置页,选择BM3101系列,勾选需要BOOT文件,烧写设置页,FLASH位宽选择16位,处理器运行频率填写实际频率,其他选项默认,点击“确定”按钮,在工程目录生成即可生成program_flash_in_ram.bin和program_flash_in_ram.exe两种二进制可执行映像文件。第五步,下载程序代码,可以通过两种方法将目标代码固化到SOPC芯片中。第一种,使用SPE-C开发环境的存储初始化功能,按图3完成PC机和硬件平台的连接,在初始化配置页,DSU口选择连接SOPC芯片的串口,文件选program_flash_in_ram.bin,其他选项默认,下载完成后,点击“转到”即可将程序固化到FLASH芯片中;第二种,使用GRMON工具,在cmd控制台中输入 “grmon–leon2-uart-comx”,即可使用pc机的X串口连接BM3109的DCL。串口连接成功后,cmd控制台会出现GRMON提示符“grmon>”。在提示符后可键入lo../program_flash_in_ram.Exe,将可执行代码下载到0X40000000地址处,下载完成后,再键入run命令,将目标代码烧写到FLASH中。将BM3109的DSU芯片拉低,设置为正常启动模式,重新上电,硬件平台即可正常执行程序。平台的系统调试构架如图4所示。

图4 平台系统调试构架图Fig.4 System debugging environment of the platform

4 结论

SOPC芯片凭借其高集成度、高灵活性的显著优点,在对系统体积、功耗、性能要求严格的军用和宇航领域已得到了广泛的应用。在追求高可靠性的网络完全领域和移动通信领域,SOPC芯片也发挥着越来越重要的作用。本文根据SOPC芯片的特点,结合工程设计,详细介绍了BM3109的硬件组成、软件构架设计和软件开发环境,对一套可行的基于国产SOPC芯片设计工程实现方案进行探索研究。

[1]BM3109IB产品使用手册[Z].航天第772研究所.

[2]吴景红.SPARC处理器启动代码的分析与编程[J].机电产品开发与创新,2008,6.

[3]张忆.BM3803计算机系统调试技术研究[J].电脑知识,2015,8.