超前进位全加器运算分析与模拟实现应用

2018-01-26大连计算机职业中专

大连计算机职业中专 梁 伟

加法器广泛应用于计算机电路和数字通信电路中,加法器能够实现加法运算的逻辑电路,加法器分为半加器和全加器两种。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出,则为全加器。

两个1位二进制全加器能够对两个1位二进制数和低位的进位实现加法运算,若被加数为Ai,加数为Bi,本位之和为Si,向高位进位为Ci,来自低位的进位为Ci-1。可以推出全加器的和为

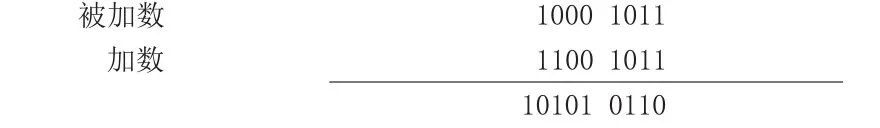

多位数加法可以实现多个二进制数相加运算,8位二进制全加器能够实现对两个8位二进制数加法运算。若A为8位被加数,B为8位加数,S为8位和,C为进位,当A=1000 1011B、B=1100 1011B时,列出计算式如下:

二进制数运算特点是“逢二进一,借一当二”,可以计算得出:和S7S6S5S4S3S2S1S0=0101 0110B ,进位C7C6C5C4C3C2C1C0=1000 1011B,如图所示,用全加器的逻辑符号画出的8位二进制全加器逻辑图。

加法器按进位数传递方式可分为串行进位和并行进位两种方式。串行进位加法器采用串行运算方式,从二进制数的最低位开始,逐位相加至最高位,运算速度不高,最高位的运算,必须等到所有低位运算依次结束,送来进位信号之后才能进行。并行进位加法器,即超前进位加法器,采用并行运算方式,将各位数同时相加,因而提高了运算速度。

超前进位加法实现原理如下:

定义两个中间变量Gi和Pi:,Gi为产生变量;,Pi为传输变量。

全加器的进位表明当Ai,Bi两个数全为1,高位进位Gi=1,即产生进位,所以Gi称为产生变量。当Ai,Bi不同时,即Pi=1,且Ci-1=1时,高位进位Gi=1,表明Pi=1时,低位的进位能够传送到高位的进位输出端,Pi称为传输变量。产生变量Gi和传输变量Pi都与进位信号无关,将Gi和Pi代入全加器的Si和进位Ci得:

进而可以推到各位进位信号的逻辑表达如下:

74LS283是具有超前进位4位二进制加法器芯片,用两个74LS283芯片能够实现超前进位8位二进制加法运算。如图所示,设置 A=1000 1011B为8位被加数,B=1100 1011B为8位加数,运用proteus模拟软件实验结果:8位和为S7S6S5S4S3S2S1S0=0101 0110B,第3位向第4的进位C3=1,最高进位第7向第8的进位C7=1,实验执行结果与分析计算结果完全相同。

下面再运用汇编程序实现8位二进制加法运算,若1000 1011B为8位被加数, 1100 1011B为8位加数,则执行加法指令后,求出本位和,并判断进位状态。

编写汇编程序:

运用debug命令进行调试,传送数据到寄存器(AL)=8BH=1000 1011B,(BL)=CBH=1100 1011B,执行加法指令ADD AL,BL后,观察到加法结果(AL)=56H=0101 0110B, 再观察执行加法指令后标志寄存器标志位的状态:CY表示CF=1进位标志,第7位向第8的进位为1,在字操作时低位字节向高位字节有进位。AC表示AF=1辅助进位标志,第3位向第4的进位为1,执行结果与分析计算结果完全一致。

算术运算包括加、减、乘、除四则运算,加法器能够实现二进制数加法运算,由于负数可用二进制数的补码来表示,这样可以把减法运算转成加法运算,加法器是实现算术运算的基本电路,超前进位加法器提高了运算速度。

[1]阎石.数字电子技术基础[M].清华大学电子教研组.

[2]沈美明,温冬婵 .IBM-PC汇编语言程序设计[M].清华大学.