基于PLL倍频电路的设计与实现

2018-01-06廉吉庆涂建辉崔敬忠

杨 坦 ,廉吉庆 ,涂建辉 ,崔敬忠

(1.兰州空间技术物理研究所甘肃兰州730000;2.真空技术与物理国防科技重点实验室甘肃兰州730000)

基于PLL倍频电路的设计与实现

杨 坦1,2,廉吉庆1,2,涂建辉1,2,崔敬忠1,2

(1.兰州空间技术物理研究所甘肃兰州730000;2.真空技术与物理国防科技重点实验室甘肃兰州730000)

锁相环由于其高集成度、良好的相位噪声和杂散特性,广泛的应用于通信、导航及遥测等领域。对于锁相环频率合成器,环路滤波器的设计对整个系统的性能起着决定性的影响。基于铷原子钟微波源的需求,文章利用锁相环技术设计了倍频电路。首先论述了锁相环的基本原理和环路滤波器的参数设计方法,然后利用ADS软件对锁相环的环路滤波器进行了设计和仿真。最后,将设计的环路滤波器应用于实际电路,并给出了测试结果。

倍频;锁相环;环路滤波器;仿真;相位噪声

倍频电路是原子钟信号源的核心部分,通过倍频电路,可以将输入晶振信号倍频至原子钟所需频率。传统的倍频方式[1-2]采用模拟倍频,分立器件的使用使得电路体积较大。为了满足原子钟小型化需求,现在多使用数字锁相倍频方式。锁相环(Phase Locked Loop-PLL)采用集成方式,不仅能减小体积,在相噪和杂散方面也有较好的性能。环路滤波器是锁相环的重要组成部分,主要由电容、电阻或者放大器组成。环路滤波器能滤掉鉴相器输出信号中的高频成分,对锁相环的杂散抑制、相位噪声、环路稳定性和锁定时间等重要环路参数有很大影响。

文中拟采用数字锁相倍频技术设计一个倍频电路,由晶振输入10 MHz信号,通过倍频电路倍频至3 417 MHz,应用于CPT铷原子钟微波信号源[3-5]。设计要求输出频率为:3 414~3 420 MHz,中心频率为3 417 MHz,相位噪声在100 Hz~1 kHz处均优于-60 dBc/Hz。

1 工作原理

PLL主要由4个模块[6-8]组成:鉴相器、环路滤波器、压控振荡器和分频器。通过振荡器引入的输入信号进入鉴相器,与经过分频器倍频后的输出信号进行鉴相处理,鉴相器输出一个与其相位差有关的电压信号,该信号经环路滤波器处理后进入VCO,通过VCO压控端对VCO输出信号进行控制。最后经反馈环路使输出频率达到稳定,经VCO输出目标频率。

其中环路滤波器对来自鉴相器的信号进行滤波,同时为系统提供一定的稳定裕量。一般鉴相器和分频器会集成在PLL芯片中,VCO有单独的芯片或者也集成在PLL芯片中,而环路滤波器则需要根据需求自行设计。

图1 锁相环系统框图

设鉴相器的增益为Kd,环路滤波器的传输函数为F(s),VCO的增益为Kv,N为分频倍数,由下图可以得到锁相环的开环增益[9-10]为:

闭环增益为:

根据上述传输特性,可以确定环路滤波器的电容、电阻值。锁相环的两个重要参数为环路带宽ωc和相位裕度φc。环路带宽会影响环路对各部分噪声的抑制,影响稳定度,需根据实际情况确定选择,取值不宜过大。相位裕度影响环路锁定时间和稳定度,相位裕度较大时,可以得到较好的稳定性,但响应速度会变慢。设计时需合理选择相位裕度的大小,初值一般取45°左右。

2 环路滤波器计算

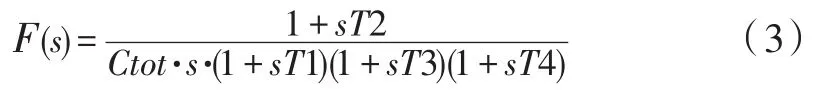

不同阶数无源环路滤波器[11]传输函数表达式如下:

其中,T1、T2、T3、T4为时间常数,Ctot为环路滤波器总电容。

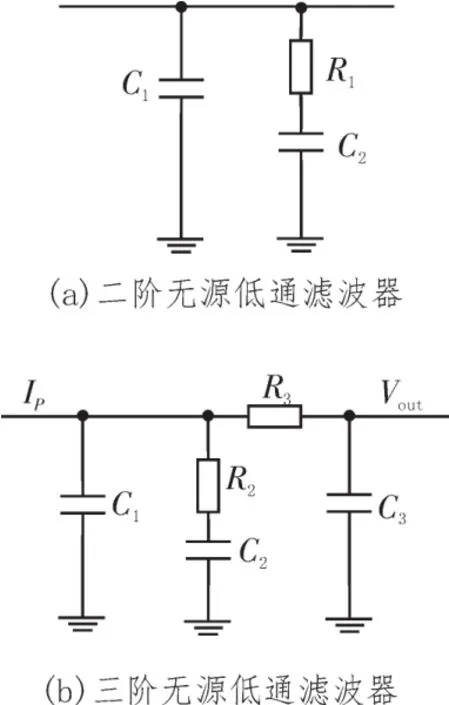

典型的二阶和三阶无源低通滤波器结构如图2(a)、2(b)所示。

图2 无源低通滤波器

不同阶数的无源低通滤波器参数如下:

表1 不同阶数无源滤波器参数表

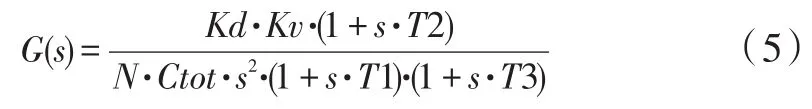

以三阶为例,滤波器传输函数:

锁相环的开环增益为:

把s=jω代入可得锁相环开环增益的相位裕度:

引入极点比T31,考虑到系统稳定性和输出信号杂散影响,T31在0到1之间取值,一般取为0.8。

总电容为:

上式中,K=KVCO·IP,KVCO为VCO压控增益,IP为电荷泵电流。

设计时根据具体应用的需求特点确定锁相环的带宽ωc、相位裕度φc和T31的值,结合器件相关参数,联立(6)、(7)、(8)、(9)式,就能求出环路滤波器参数T1、T2、T3及Ctot的值。再根据表1,通过一定的数学近似,可以求出三阶环路滤波器的电 阻和电容参数的具体值。

文中根据CPT铷原子钟微波信号源的需求,利用锁相环数字倍频技术设计一种中心频率为3 417 MHz的信号源,利用ADS软件来求解环路滤波器的相关参数并进行相位噪声模拟仿真[12-14]。

文中的锁相环芯片采用ADI公司的ADF4350,该芯片内集成有鉴相器、分频器和VCO,外部需接一个低通环路滤波器。倍频电路选用锁相环和VCO相关参数如下:

1)VCO输出频率:137.5~4400 MHz;

2)VCO灵敏度:33 MHz/V;

3)参考源频率:10 MHz;

4)鉴相器频率:32 MHz;

5)电荷泵电流:5 mA。

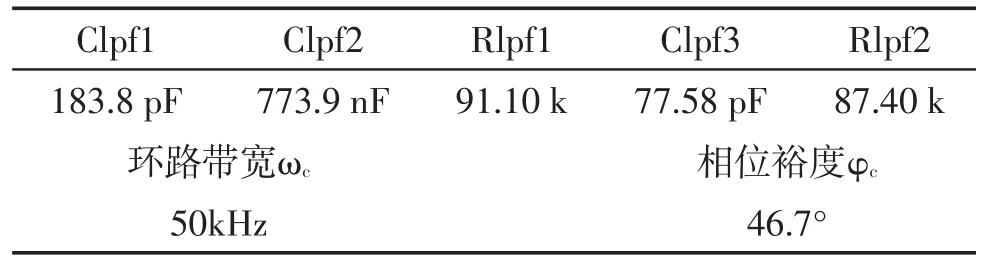

设计目标是:输出频率:3 414~3 420 MHz,频率分辨率为10 kHz,相位噪声在100 Hz~1 kHz处均优于-60 dBc/Hz。为减小有源环路滤波器引入的噪声,采用无源3阶环路滤波器,系统环路带宽ωc=50 kHz,相位裕度为45°~50°。

利用ADS生成的仿真结果如图3所示。

图3 环路滤波器仿真模拟图

所以,得到的仿真结果为:

表2 环路滤波器仿真结果

利用ADS软件模拟的环路滤波器的相位噪声如图4所示。

图4 环路滤波器噪声仿真模拟图

3 测试分析

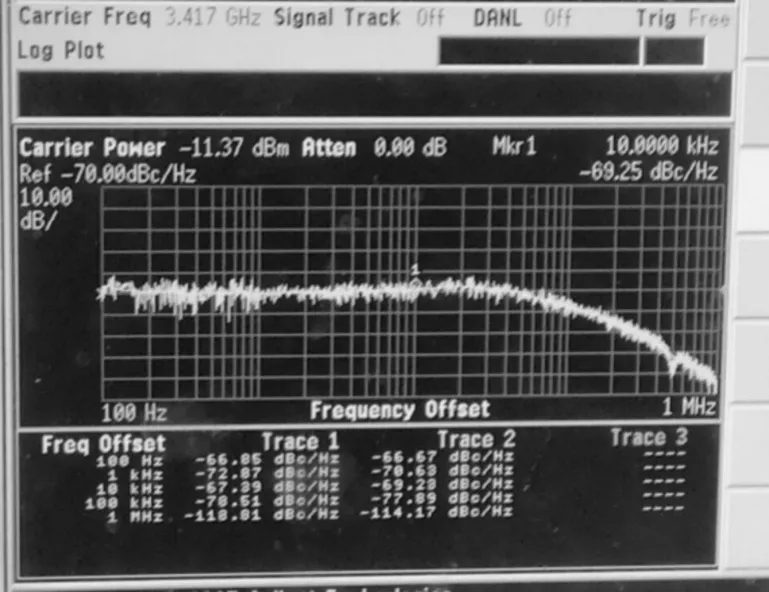

将计算的电阻、电容值应用于实际微波源电路[15-17],测得的信号频谱如图5所示,测得的相位噪声如图6所示。

由信号频谱图可以看出,输出信号的频率为3 416.987 MHz,与目标频率3 417 MHz的频差只有13 kHz,出现偏差的主要原因是倍频电路的输入10 MHz信号存在一定偏差,该信号频率在原子钟工作时由伺服电路进行调节锁定。因此,设计达到输出频率在3 414 MHz~3 420 MHz的要求。

考虑到系统相噪,PLL的带内相噪可用如下公式估算[18]:

图5 输出信号频谱图

图6 输出信号相位噪声测试图

其中PNTotal为锁相环输出信号的带内相噪,PNPLL为锁相环的归一化带内相噪,N为VCO输出频率与鉴相频率的比值,fPFD是鉴相器的鉴相频率。由式(10)可以看出,PLL系统相噪主要由PNPLL、分频器N和鉴相频率fPFD影响。而PNPLL是由锁相环芯片本身决定,可以当成一个常量处理。

ADF4350的带内归一化相噪为-213 dBc/Hz,本文在小数分频模式下,杂散平均化,所以ADF4350的带内归一化相噪为-210 dBc/Hz。本文鉴相频率为1 MHz,输出信号频率为 3.417 GHz,则N=3417,fPFD=1 MHz,根据式(10),带内相噪的理论值为:PNTotal=-79.33dBc/Hz。

由相位噪声图可以看出,相位噪声与理论值有一定偏差,这是由于实际电路系统外部噪声的干扰和电路的测试误差造成的。总的来说,实际测试的相位噪声和模拟噪声值较为接近,相躁偏差在误差允许范围内,在100 Hz~1 kHz处,实际相位噪声均小于-60 dBc/Hz,满足设计要求。

4 结束语

本文基于数字锁相环技术,设计一倍频电路,应用于CPT铷原子钟微波信号源。文章首先分析了锁相环的基本原理,由传输函数计算出环路滤波器相关参数,然后利用ADS进行设计和仿真。最后将设计结果应用于实际电路,经实际测试,设计电路满足要求。在实际工程设计中,可以通过选择合适的环路带宽和相位裕度,计算出环路滤波器的相关参数,对设计进行优化,最后得出最优的输出信号频谱。

[1]庄卉.锁相与频率合成技术[M].合肥:中国科学技术大学出版社,1996.

[2]白居宪.低噪声频率合成器[M].西安:西安交通大学出版社,1994.

[3]刘类骥,赵海清,曹远洪.一种芯片原子钟专用锁相倍频器研究与设计实现[J].宇航计测技术,2014,1(30):37-41.

[4]廉吉庆.CPT原子钟数字锁相倍频技术研究[D].兰州:兰州空间技术物理研究所,2014.

[5]刘静,孙兵峰,阎世栋.一种微波倍频方案在小型化铷钟的应用[J].波谱学杂志,2013,30(4):559-566.

[6]远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才,译.北京:科学出版社,2006.

[7]刘颖.锁相环中鉴相器和环路滤波器的设计[D].西安:西安电子科技大学,2013.

[8]廉琛.基于注入锁定技术的锁相环、倍频器和分频器的研究与设计[D].上海:复旦大学,2012.

[9]杨坡,黄显核,夏丹丹.电荷泵锁相环环路滤波器的设计[J].声学技术,2011,30(4):369-372.

[10]任青莲,高文华,郭萍.三阶PLL无源环路滤波器的设计与仿真[J].四川兵工学报,2014,35(2):101-104.

[11]王东虎.快速锁相无源三阶环路滤波器的设计与检测[J].电子产品可靠性与环境试验,2012,30(4):61-64.

[12]刘丽平,杨维明,李倩,等.锁相环中无源滤波器的设计与仿真[J].湖北大学学报,2011,33(4):494-497.

[13]金玉琳,佘世刚,周毅.锁相环环路滤波器噪声特性分析与仿真[J].现代电子技术,2011,34(21):193-198.

[14]高立俊.基于ADIsimPLL 3.1的锁相环环路滤波器设计[J].现代电子技术,2013,36(15):56-58.

[15]史学明,陈杰华,张奕.微波倍频器的设计[J].中国宇航协会,2011全国时间频率学术会议,北京,2011.

[16]汤晓东,孟志朋.6.5GHz锁相环单片集成电路设计[J].半导体集成电路,2014,39(3):174-192.

[17]窦建华.GHz PLL倍频器的设计与研究[D].南京:东南大学,2011.

[18]徐述武,汪海勇,唐云峰.基于ADF4350锁相频率合成器的频率源设计与实现[J].电子器件,2010,6(33):725-729.

Design and implementation of frequency multiplier based on PLL

YANG Tan1,2,LIAN Ji-qing1,2,TU Jian-hui1,2,CUI Jing-zhong1,2

(1.Lanzhou Institute of Physics,Lanzhou730000,China;2.National key Laboratory of Science and Technology on Vacuum Technology&Physical,Lanzhou730000,China)

PLL is widely used in communications,navigation,telemetry and many other fields for its high integration,good phase noise and spurious characteristics.For PLL frequency synthesizer,the design of loop filter has a decisive influence on the whole performance.In this paper,we design the multiplier in accordance with the requirement to microwave signal by the Rb atomic clock through digital PLL technology.First,we discuss the basic principle of the PLL and the design method of the parameters for the loop filter.Then we designed and simulated a loop filter for PLL by ADS according to demand.Finally,we applied the design to the circuit and presented the test results.

multiplier;PLL;loop filter;simulation;phase noise

TN742

A

1674-6236(2017)23-0105-04

2016-11-09稿件编号:201611071

杨坦(1989—),男,河南沈丘人,硕士研究生。研究方向:原子频标与技术。