555定时器构成的单稳态触发器仿真分析

2017-12-20张学文司佑全

张学文,司佑全

( 湖北师范大学 物理与电子科学学院,湖北 黄石 435002)

555定时器构成的单稳态触发器仿真分析

张学文,司佑全

( 湖北师范大学 物理与电子科学学院,湖北 黄石 435002)

由555定时器构成的单稳态触发器,在低电平触发端加入宽度大于暂稳态时间的负脉冲信号时,触发器输出的波形会出现抖动。为解决这一问题,可在输入电路中加入微分电路。经Multisim8模拟验证表明:加入了微分电路的555定时器,输出状态正常。

555定时器;单稳态触发器;微分电路

555集成定时器是一种模拟、数字混合型的中规模集成电路,只要外接适当的电阻、电容等元件,可方便地构成单稳态触发器、多谐振荡器、施密特触发器等脉冲产生或波形变换电路[1]。本文利用Multisim8对555集成定时器构成的单稳态触发器进行仿真分析。

1 内部结构、原理

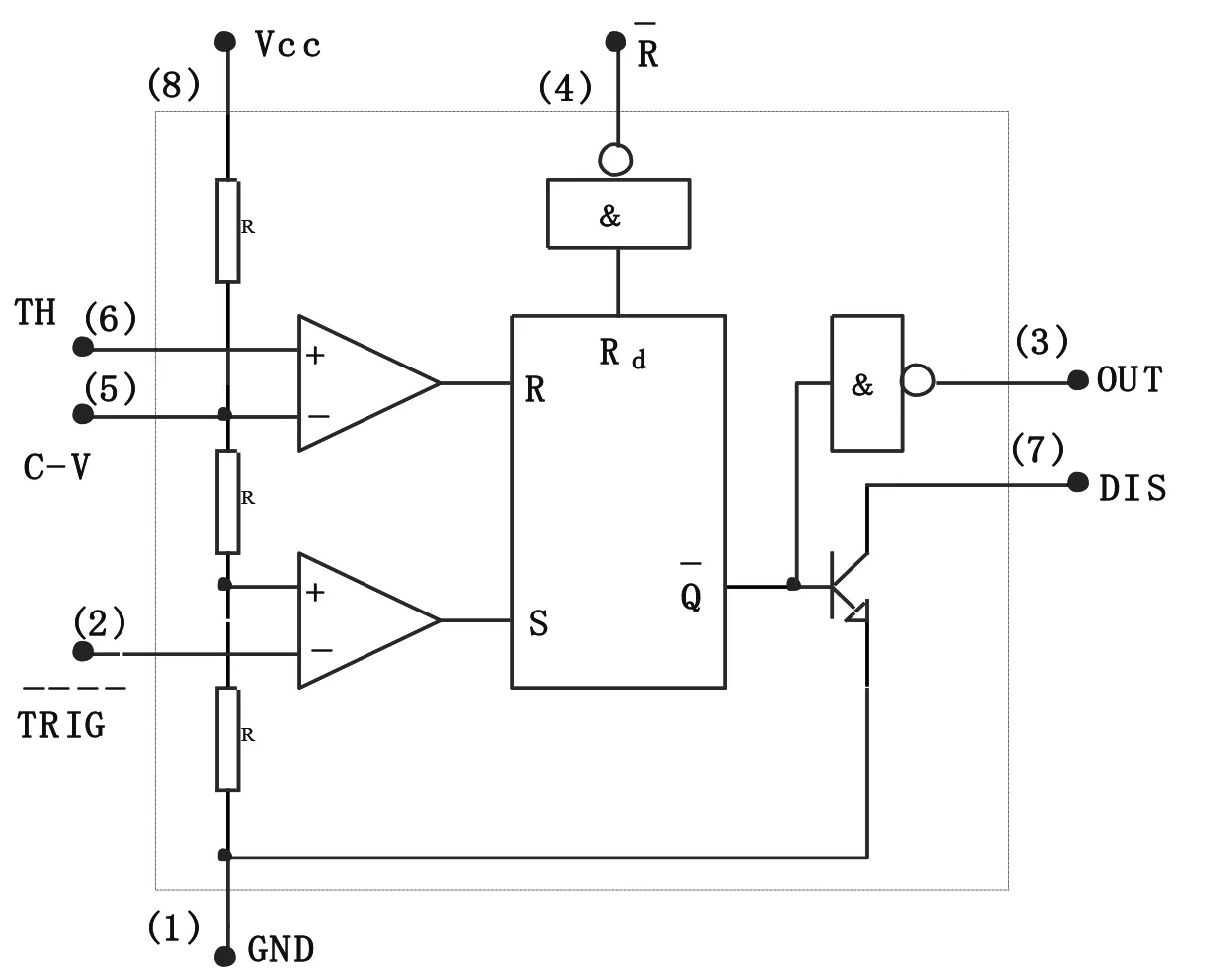

555集成定时器内部逻辑图如图1所示。

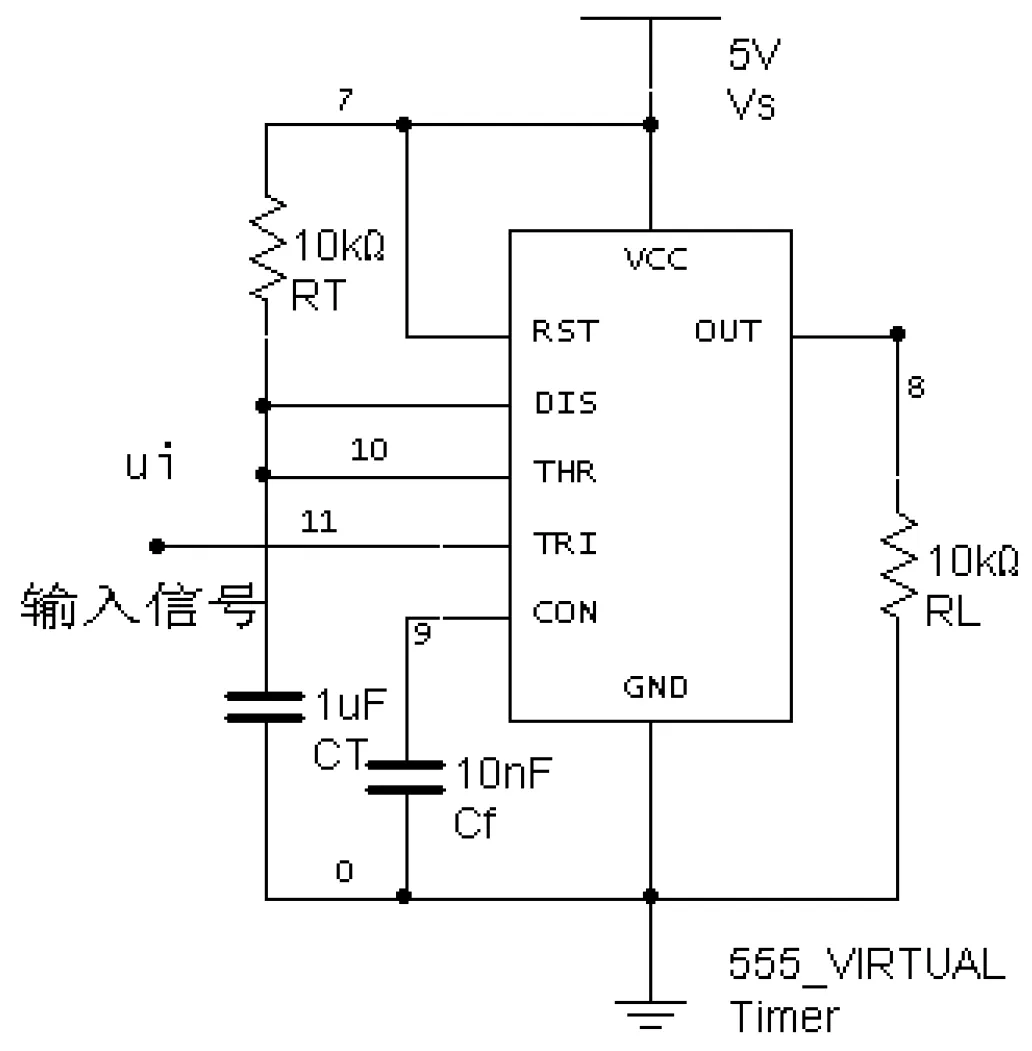

依据555集成定时器的结构特点,在图2所示电路中,2(TRI)脚为触发信号输入端,电路处于初始稳态时,单稳态触发器的输出u0为低电平。若在2脚加一个具有一定幅度的负窄脉冲,当电位小于Vcc/3,比较器A2触发翻转,触发器的输出u。从低电平跳变为高电平,暂稳态开始。电容C开始充电,uc按指数规律增加,当uc上升到2Vcc/3时,比较器A1翻转,触发器的输出u0从高电平返回低电平,暂稳态终止。同时内部电路使电容C放电,u0迅速下降到零,电路回到初始稳态,为下一个触发脉冲的到来做好准备。 暂稳态的持续时间tW由外接元件R、C的大小决定,其表达式为

tW=1.1RC

(1)

图1 555定时器内部逻辑图

图2 单稳态电路

改变上式中R、C的值可使tW在几个us到几十min之间变化。一般电阻取1kΩ~10MΩ,C>1000pF.[2]

2 单稳态电路

2.1 低电平触发端直接加入一定宽度的负脉冲信号

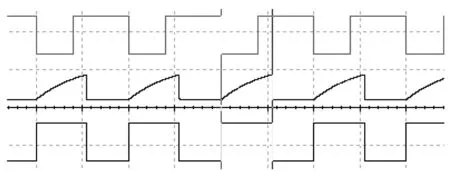

2.1.1 输入信号负脉冲宽度小于暂稳态时间

2.1.2 输入信号负脉冲宽度大于暂稳态时间

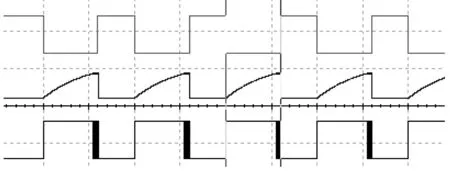

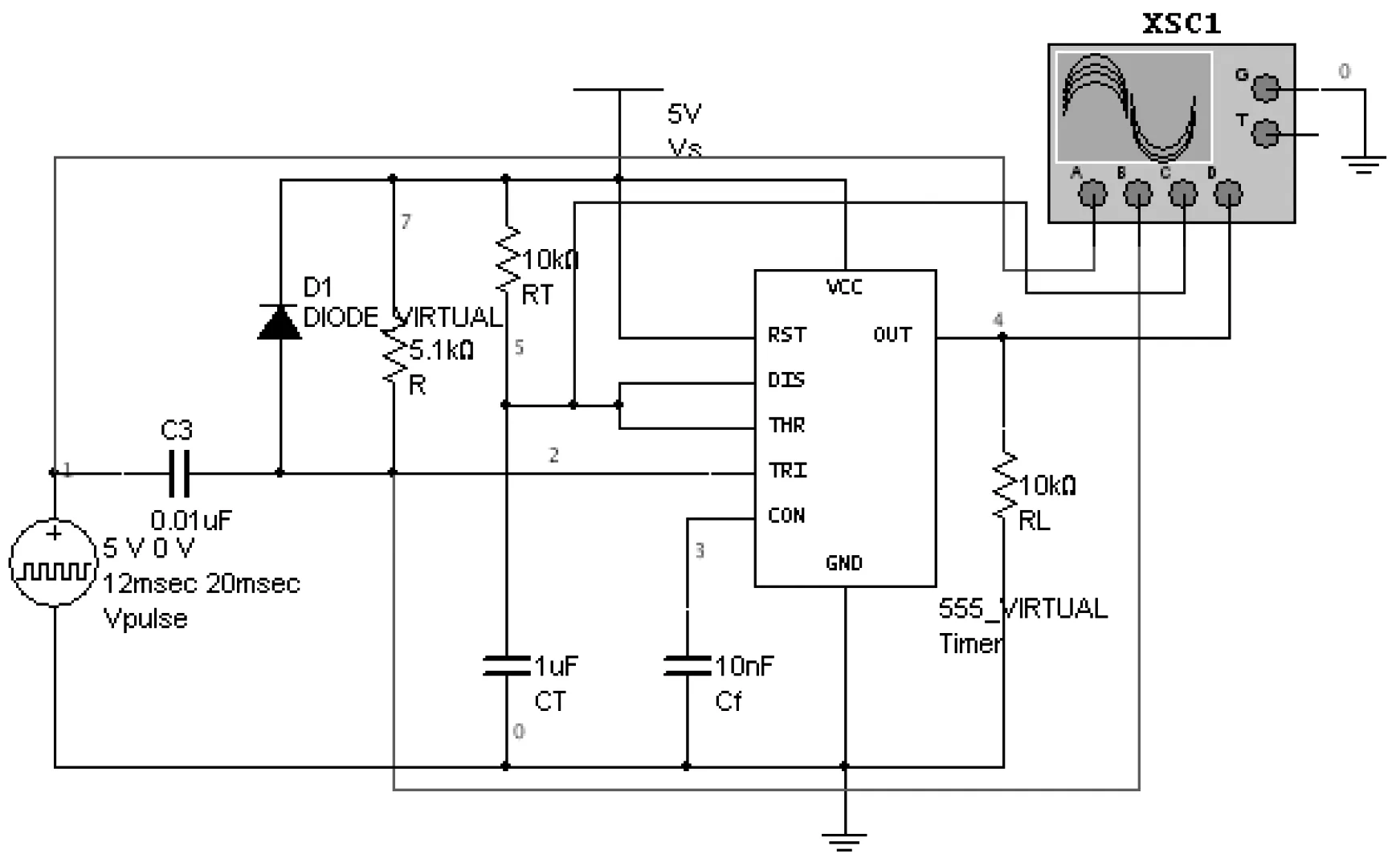

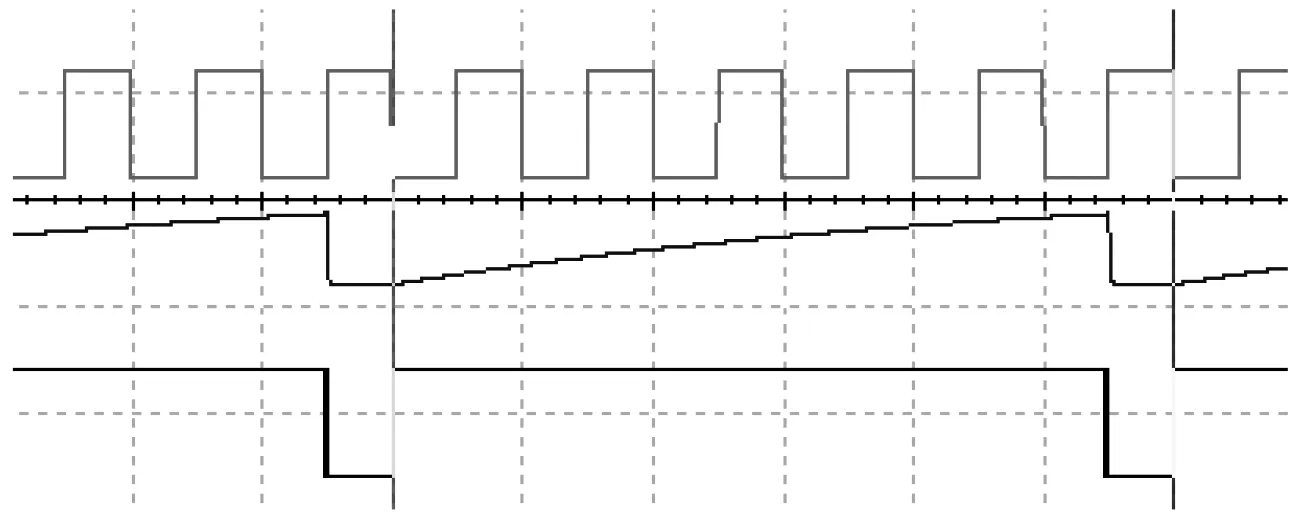

在图2电路中,由式(1)可知,暂稳态时间计算值为11ms,当输入信号负脉冲宽度大于11ms时,其仿真波形如图4所示。

从图4仿真图可知,当输入信号负脉冲宽度大于暂稳态时间时,输出波形出现了抖动。

图3 输入信号负脉冲宽度小于暂稳态时间仿真波形

图4 输入信号负脉冲宽度大于暂稳态时间仿真波形

2.2 低电平触发端加入周期性脉冲宽度大于暂稳态时间的脉冲信号

由以上分析及仿真可知,当输入信号负脉冲宽度大于暂稳态时间时,其输出波形出现了抖动,故对以上电路进行改进,以避免此现象的发生。

2.2.1 信号源输出信号通过微分电路加入低电平触发端

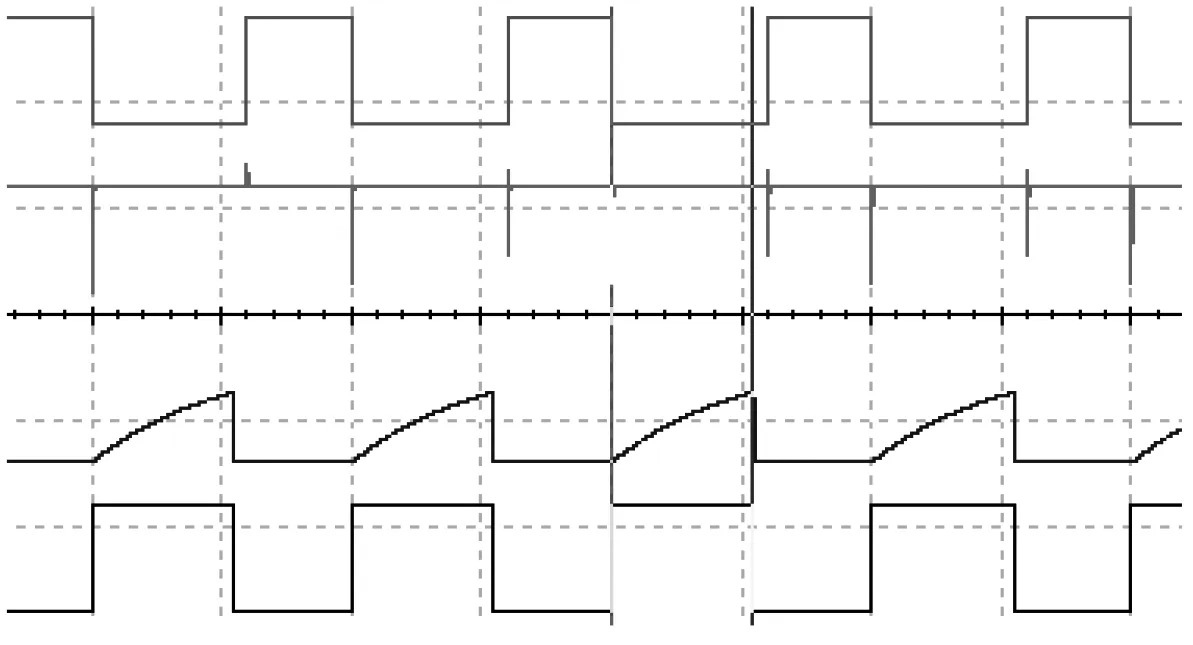

图5 加入微分电路的单稳态触发器

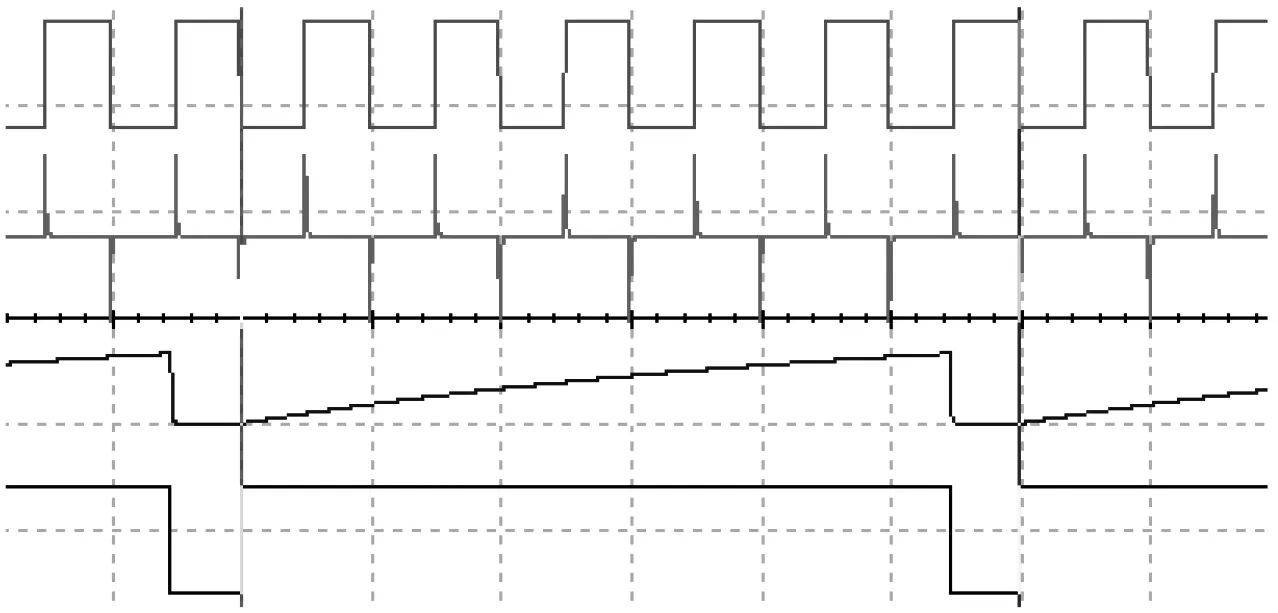

图6 加入微分电路脉冲宽度范围大于暂稳态时间的波形

此时输入信号频率不受限制,其仿真波形如图6所示。

图6中由上至下依次为输入信号、输入触发、定时电容两端电压uc的波形、输出信号波形。图8、图10、图11类同。

2.2.2 改进电路

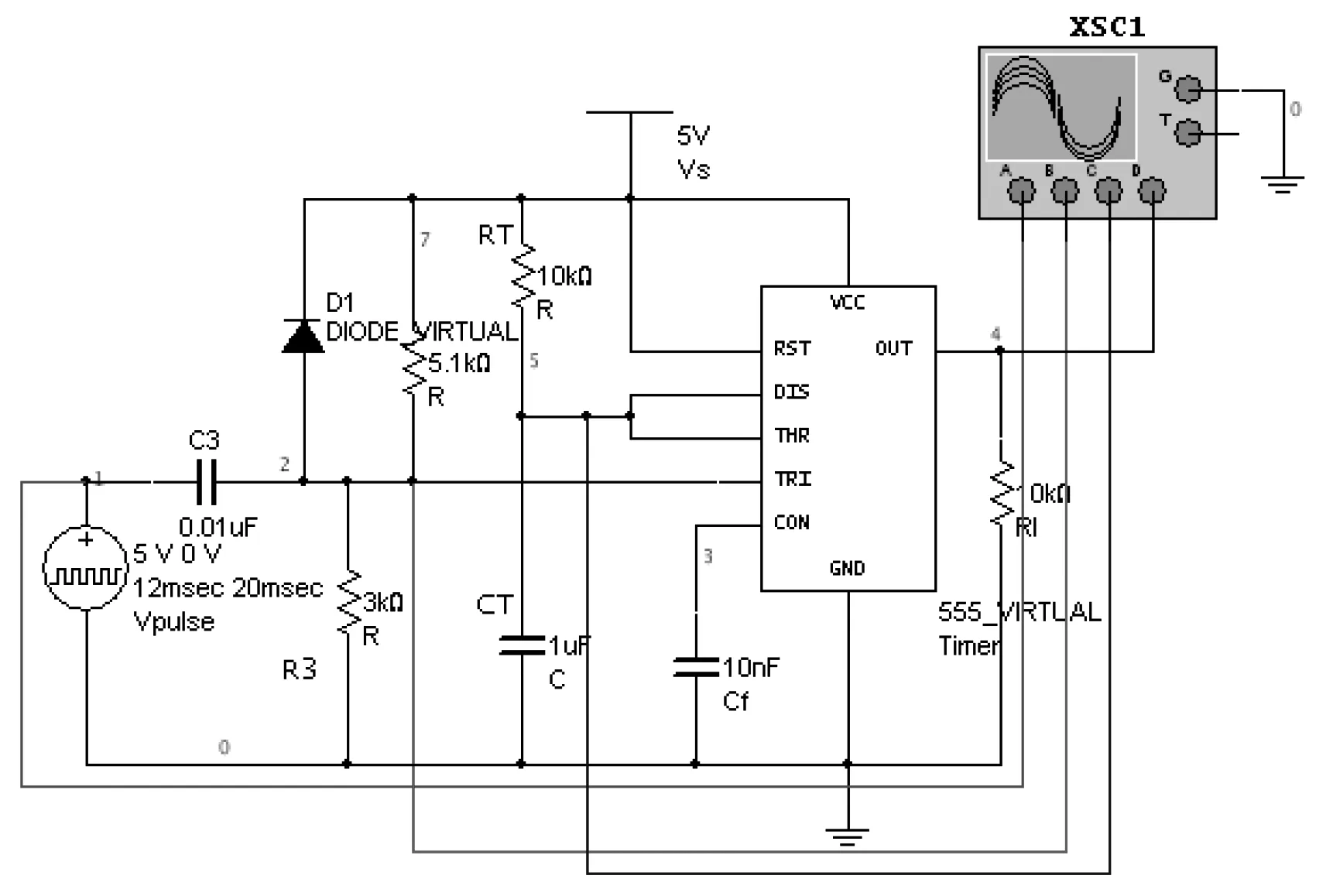

图7 加入微分电路和分压电路的单稳态触发器

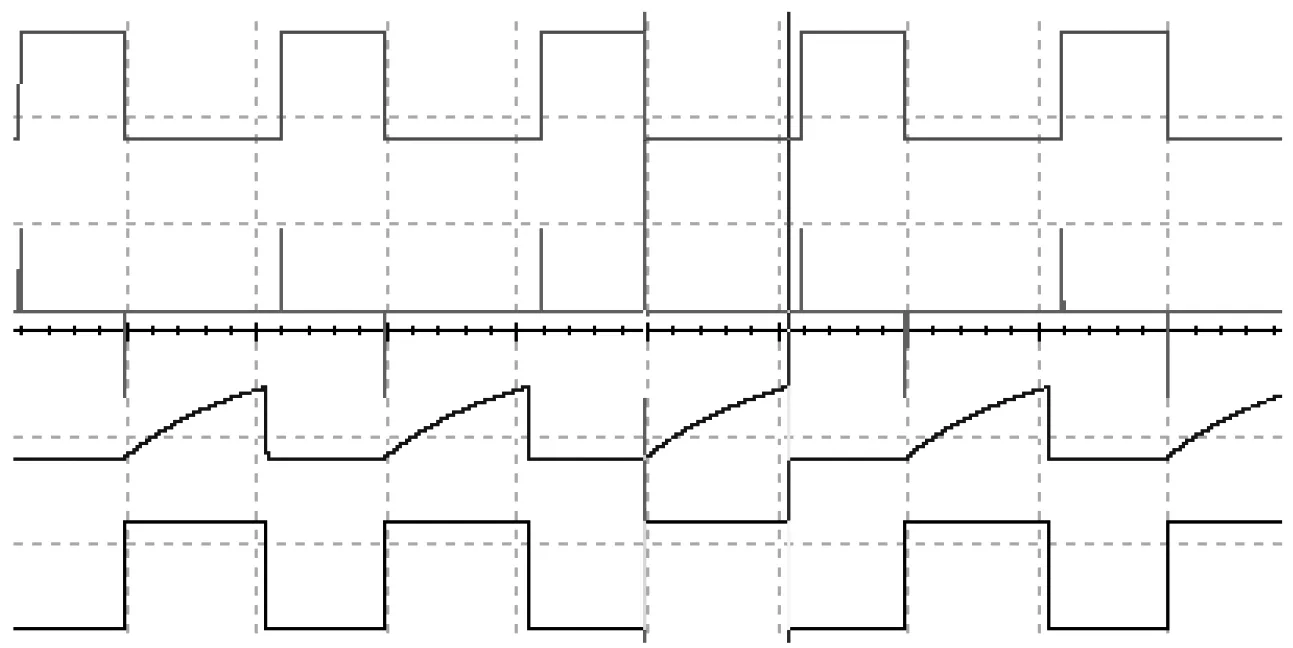

图8 加入微分电路和分压电路的单稳态触发器波形

2.3 低电平触发端加入周期小于暂稳态时间的脉冲信号

在图2中,R=10kΩ,C=1uF,当输入脉冲信号周期小于暂稳态时间时,1 图9 6分频电路波形 图10 加入微分电路6分频电路波形 由图9可见输出信号在输入信号的上升沿处均出现了抖动。 在图2中如图5那样,在低电平触发端加入微分电路,输入周期为2ms(占空比为50%)的连续脉冲,得到图10所示信号。 图10所示,在输入端加入微分电路后分频电路波形不再出现抖动现象,波形非常好。但是可以很清楚地看到在输入信号正脉冲部分2脚也有负尖脉冲。图2所示电路,如图7那样在输入端加入微分电路和分压电路,得到分频电路波形如图11所示。 图11 加入微分电路和分压电路的6分频电路波形 这样输出信号不会出现误触发,也不会出现抖动。可以确保实现预定的分频倍数。 信号源输出信号通过微分电路加入低电平触发端,可以加入脉冲宽度范围大于暂稳态时间的脉冲信号,输出波形稳定;若在正脉冲处低电平触发端出现负跳变,则在低电平触发端和地之间接入一个电阻构成分压电路能很好地解决了这一问题。当在低电平触发端加入周期小于暂稳态时间的脉冲信号时,输出信号周期是输入信号周期的整数倍,构成分频电路,在输入端加入微分电路和分压电路能确保实现所需分频。 [1]电工电子实验教程编写组. 电工电子实验教程[M].长春:东北师范大学出版社,2011,3:234~238. [2]王艳春.电子技术实验与Multisim仿真[M].合肥:合肥工业大学出版社,2011,6:76~78. [3]宋万年,王 勇,孔庆生.模拟与数字电路实验[M].上海:复旦大学出版社,2004,7:136~138. [4]阎 石.数字电子技术基础(第五版)[M].北京:高等教育出版社,2006,5:489~491. [5]陈大钦.电子技术基础实验[M].北京:高等教育出版社,1994,5:170~172. [6]李卫兵.555定时器电路的等效分析与Pspice仿真[J]. 滨州师专学报, 2004,20,(4):67~71. [7]姚海燕.555时基集成电路测试中电容的巧用[J].信息技术,2010,(08):189~193. [8]任骏原.555单稳态触发器的触发特性分析[J].吉林大学学报(信息科学版),2013,31,(02):170~172. Simulationanalysisofmonostabletriggerbasedon555timers ZHANG Xue-wen,SI You-quan (College of Physics and Electronic Science, Hubei Normal University, Huangshi 435002,China) For the monostable trigger composed of 555 timers, its output waveform will form dithering when a negative pulse signal with a width greater than the transient time is added to the low-level trigger. To solve this problem, a differential circuit can be added to the input circuit. The simulation by Multisim 8 shows that the 555 timer added the differential circuit output normally and no jitter occurs. 555 timer; monostable multivibrator; differential circuit TN79+1 A 2096-3149(2017)04- 0073-04 10.3969/j.issn.2096-3149.2017.04.015 2017—06—21 湖北师范学院校级教研项目(JH201129,ZD201121) 张学文(1965— ),女,湖北黄冈人,高级实验师,从事电子技术实验研究.

3 总结