基于FPGA的多通道串口数据采集与传输设计

2017-12-15,,,

,,,

(1. 榆林学院能源工程学院测控教研室,陕西 榆林 719000; 2. 中国人民解放军96901部队,北京 100094)

基于FPGA的多通道串口数据采集与传输设计

郭敏1,庄信武2,王向东2,吴金才2

(1.榆林学院能源工程学院测控教研室,陕西榆林719000; 2.中国人民解放军96901部队,北京100094)

多通道串口数据传输是现代工业控制传输一种新要求,而传统的工业控制器因接口数量的有限,往往难以满足该项要求;论文针对多通道串口数据的采集与传输现实需要,提出了一种基于FPGA的多通道串口数据采集方案;该方案引入了多路串口数据的同时采集、缓冲及打包的数据流处理思想,采用基于FPAG+多串口+USB的硬件框架结构及总线不同速率的传输软件处理算法,实现了多路串口数据的采集与传输;为了验证该设计方案的有效性,论文以某软件无线电平台为试验对象,预期设计了6路串口同时传输的试验方案,最终通过对发送的源数据与接收的数据进行比对发现两者一致,结果表明该方案的有效性,试验满足预期要求,达到多路串口同时采集及传输的目的。

FPGA;多通道串口;数据采集;数据传输

0 引言

目前多通道串口数据通讯在医疗、通信、工业控制等诸多领域得到广泛的应用[1-2],其特点是硬件实现简单,监控系统与被监控设备的连接采用“点对点”连接方式,不存在相互之间的干扰,出现问题时便于排查,且不受操作系统的限制,硬件成本低。然而在一般情况下,一个微控制器往往只带有一组或两组串口通信模块或通道。为了扩展更多的串口通道数,通常采用多通道串口芯片,如SP2358,SP2338,TL16L554等实现,这种模式亦存在诸多局限性,如:1) 单组芯片最多能容纳的通道数不超过4个通道;2) 芯片本身不具备波特率自行配置;3) 单芯片通道数越多,价格越昂贵等诸多问题[3]。

伴随着可编程逻辑阵列芯片的出现与发展,从某种程度上解决了上述单芯片的局限性问题。可编程逻辑芯片最为典型的是现场可编程门阵列(Field- Programmable Gate Array,简称FPGA),它是在PAL、GAL、CPLD等可编程器件上发展起来的。由于自身并行处理及可重复编程的特点,在硬件电路设计中克服了传统定制电路设计思想的不足,这对提高系统可靠性、提高设计效率、减少PCB电路板的面积、节约设计成本等诸多方面具有强大的优势,也为此得到了广大电子硬件工程师的青睐。在此过程中也有一些工程师设计了多串口扩展系统[4],采用模块化设计,满足了与多路串口外设同时通信的要求,但扩展系统中采用MCU + FPGA结构使得系统有些冗余,不易实现即插即拔和小型化。

论文针对上述传统微控制器在多通道运用上的局限性,结合FPGA并行处理等优势特点,着手基于FPGA的多通道串口数据采集与传输展开设计研究。目的是通过研究,解决波特率自行配置和串口通道数受限的问题,同时利用该设计思想,可将该成果拓展到其它接口多通道的设计。

1 系统框架架设

根据性能剖分,基于FPGA的多通道串口数据采集与传输系统,从硬件层面上可剖分为以下几大模块:电源模块、接口芯片模块、FPGA信号处理与控制模块等三大部分组成。其中电源模块为整个系统提供稳定的电压、电流源;接口芯片模块实现主机与外设之间交换信息,主要包括串口模块及向上位机高速率传输的USB接口模块,在现实使用过程中,USB接口模块可能还承担整个电路的电源供电功能,最终达到实现即插即拔,及电路模块的小型化功能;FPGA信号处理与控制模块,利用其可重复编程特点,实现整个系统的整体协调与控制,及必要的信号处理工作,从软件层面上看主要包括:

1) 实时正确接收、发送各个串口的数据;

2) 实现串行转并行工作,将串口芯片接收到的串行数据进行并行化处理,然后再将这些数据压入各个串口接收数据缓存中;

3) 协调各个串口接收缓存,将数据封装打包后压入高速传输的USB接口芯片缓存中;

4) 解析控制高速USB接收的缓存数据,后压入串口发送数据缓存中,并进行并行转串行处理;

5) 实现与USB接口芯片通信。

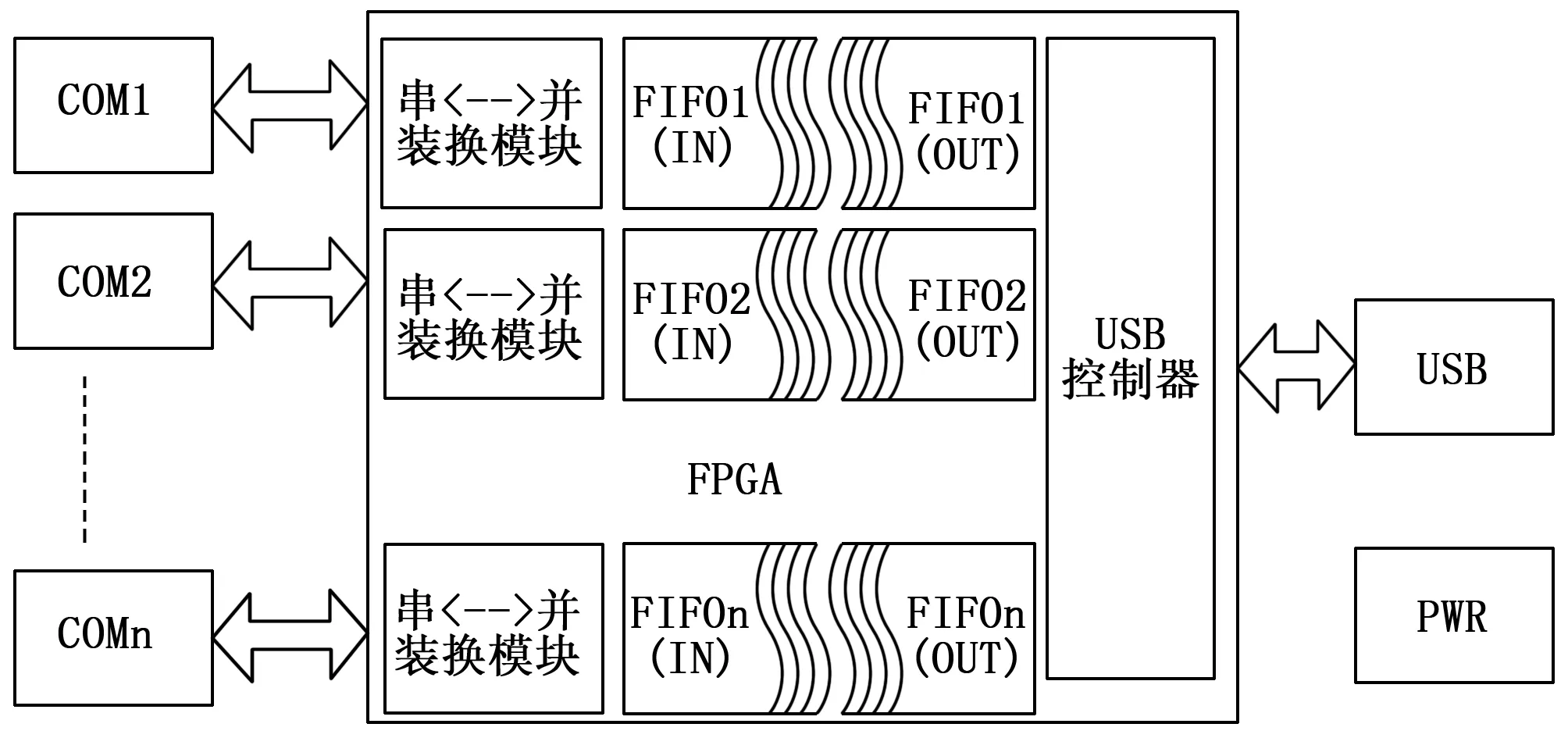

梳理上述功能,系统的整体框架可构建如图1所示。图中COMn表示第n个串口电路模块,主要完成串口逻辑电平与FPGA触发电平之间的逻辑电平转换、特性参数分析等;串并转换模块主要进行了串行信号的接收、接收数据的串转并,发送数据的并转串,以及所需的时序控制;FIFO数据缓存模块主要实现不同传输速率的数据在处理过程中的缓冲作用,以防止在进机和存储操作时,数据不必要的漏帧或溢出等情况发生,从中提高传输效率的作用;USB控制器主要实现转换电路与高速USB接口之间的握手通信,及数据的接收与发送等工作,其中包括串口传输波特率、传输位数、奇偶矫正等各个串口参数的控制。

图1 多通道串口采集与传输系统框架

2 FPGA功能模块设计

FPGA由于设计灵活,可重复编程,是整个转换电路的核心部分,为了能够实现FPGA上述5个功能,论文针对这些功能分别进行建模。

2.1 串口捕获模块设计

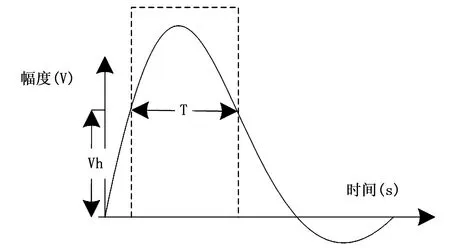

受外界扰动环境的影响,数据在串行总线上传输可能发送误比特情况。这种误比特通常表现为串行总线上串入浪涌或毛刺(下文将此情况称为“扰动”),其波形示意如图2,其中Vh为接口触发的门限电平,T为触发的扰动宽度。图中若触发的扰动宽度T越宽,则在单位时间内累计的触发样本数就越多,误触发的概率越大。

为了提高串口抗干扰能力,除了在硬件设计上采取串入防浪涌电容及线缆电磁屏蔽等防扰动处理外,还可以在串行传输数据的软件捕获上采取防扰动处理,以降低误比特率。关于硬件防扰动处理方式相关文献已做了论证[5-6],此文不再赘述。论文仅从软件层面结合FPGA硬件特点进行防扰动研究,以最大程度地忽略扰动对接口比特流采样的影响。

图2 扰动波形示意图

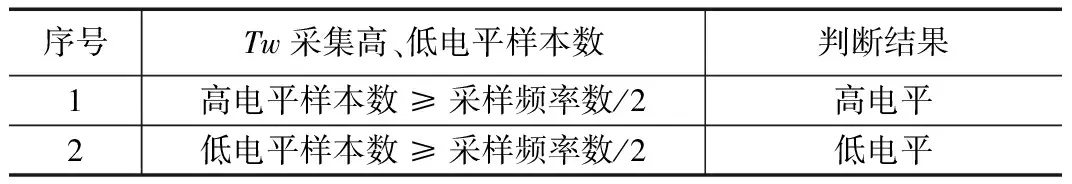

从统计学角度来看,样本数越多,则越能揭示事物的本质。同理,在采样系统中,若提高了接口的采样率,增加单位时间内接口采样的样本数,通过样本数的概率分布情况就可以很有效地揭示数据的真实性,即准确判断触发电平实际电平是高电平还是低电平。根据RS232串行总线接口规范定义,串口波特率是特定的,无非就是几种常用的波特率,如300、600、1 200、2 400、4 800、9 600、19 200、38 400、43 000、56 000、57 600、115 200等,当选择某种波特率作为数据的传输速率时,单个比特的数据位宽Tw也就对应明确。在这固定数据位宽Tw内采集高、低电平的样本数,通过此样本的高低电平分布情况,可准确判断串行总线在数据位宽Tw内为高逻辑电平,还是低逻辑电平,具体分布如表1所示。

表1 软件抗干扰判断表

2.2 串并转换模块设计

串并转换模块是根据串行总线规范协议,按照串行总线数据帧结构,从串行总线上解析出易于存储和传输的并行数据,如8位数据等;或者按照串行总线接口规范协议,并行数据的串行化处理,形成按规范要求的串行流数据帧结构。

串并转换模型设计是结合上述3.1中的防扰动处理措施进行建模的,模型的RTL模块如图3所示。

图3 串< - > 并互转电路RTL模块

其中clk为系统同步时钟,reset为系统复位信号;左图为串转并模型,iRXD为经接口电平转换后,FPGA能够采样的串口接收信号;oDOUT[7:0]为并行处理后的8位输出数据,若设定为7位,则取最低7位有效位;oslDone为串口接收完满帧后,给出的脉冲同步信号,以供后级模块提供同步触发源。右图为并转串模型,按照串行协议插入起始位、数据位、停止位以及必要奇偶校验位等,其中iDin[7:0]为8位宽度的并行数据,ilsSta为同步脉冲数据信号,oTXD为串行数据信号,oslFull为并串转换模块的32 Bytes的缓冲满标志。

并转串仿真结果如图4所示,此次仿真中,数据位为8位有效数据0x55,无奇偶校验位,2位停止位,波特率位115200,其中oTXD输出的数据流包括,起始位、数据位、停止位及奇偶校验位,按照串行总线接口规范,oTXD输出数据流为0_1010_1010_11,仿真结果与其一致,由此可说明该模型的正确性。

图4 并行转串行总线数据仿真结果

针对串口转并口模型验证,可利用上述“并转串模型”的oTXD输出数据作为“串转并模型”的信号源,仿真条件与上述一致,同时为了验证串行数据接收的抗干扰性,在串行总线上加入1/5位宽的干扰噪声,仿真结果如图5所示,在每个高电平处有大约1/5脉宽的低电平扰动,经过抗干扰软件处理后,得到的8位16进制数据0x55,通过比较发现,接收到数据与源16进制数据0x55是一致。这结果进一步验证了模型抗干扰的有效性。

图5 加入噪声后串行转并行总线数据仿真结果

2.3 多级缓存模块设计

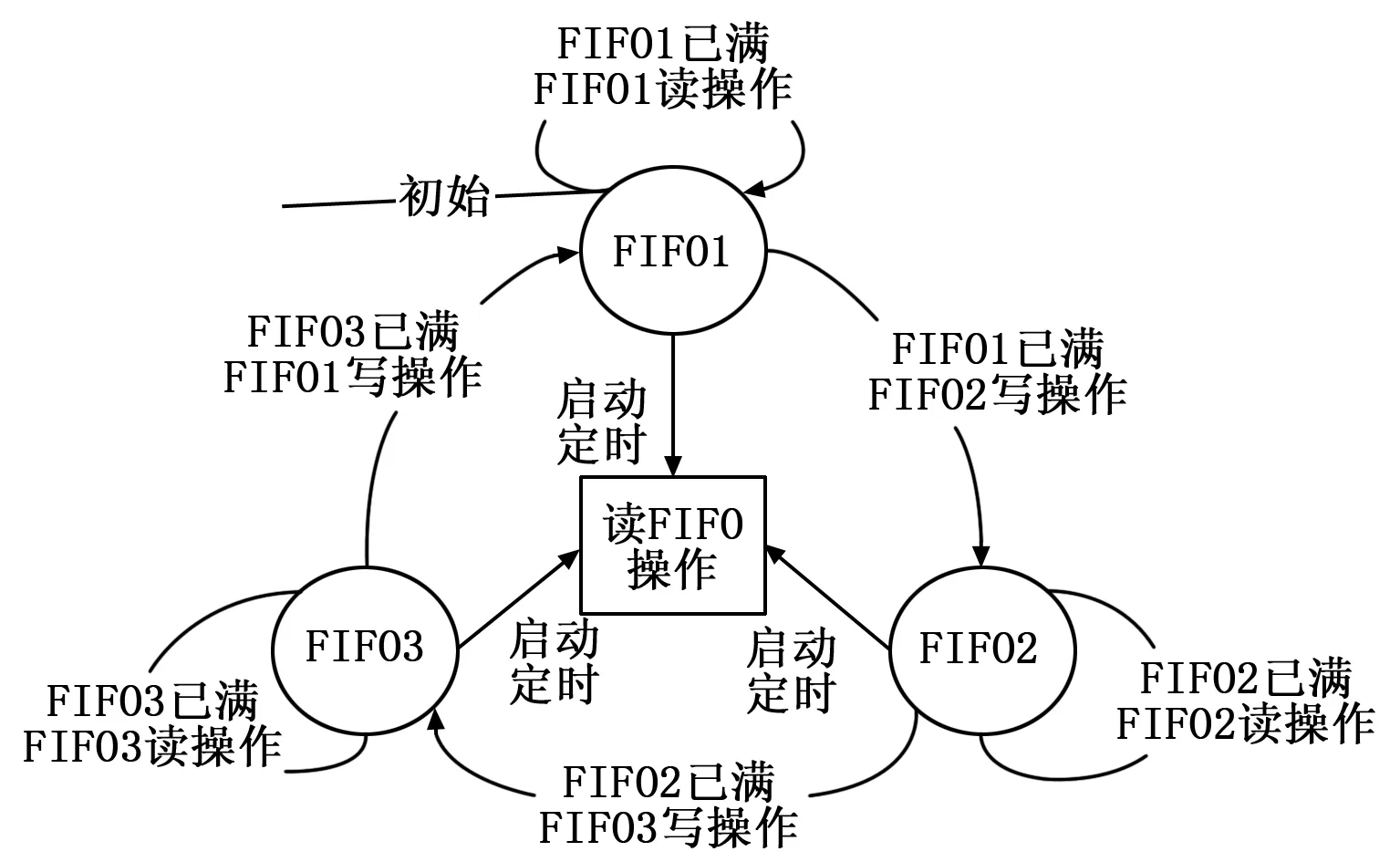

多级缓存设计的目的是实现多个串口数据接收过程中实现数据的缓冲,以避免数据同时处理出现数据的溢出或漏诊问题发生。在实际操作过程中,将接收的数据一级压入一级,避免不同速率传输数据因未匹配而造成的数据丢帧情况发生。本设计中,每个串口的多级缓存拟采用多个3数据级联FIFO结构,如图6所示。

图6 多FIFO数据缓存结构

单个FIFO缓冲器进行轮换读写,其中有一个FIFO始终处于空闲状态,目的是为了避免读写冲突,另外两个:一个FIFO进行写操作、一个FIFO进行读操作;当写操作FIFO满时,启动两个方面工作:一方面是启动打包程序,将FIFO中的数据快速转入数据帧结构中,待传输到高速的USB接口缓存中;另一个方面是启动缓存写FIFO的切换。当3个FIFO经过一段时间后,仍没有数据写入时,系统启动读取FIFO中剩余的数据操作,及时读取FIFO中剩余的数据,以避免数据丢帧。系统状态机可设计如下

图7 多FIFO数据缓存状态机

2.4 USB控制模块设计

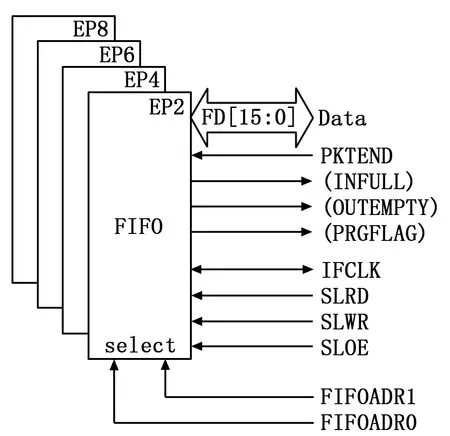

USB控制器主要实现FPGA与高速USB接口之间的握手通信,及数据的接收与发送等工作。目前常用的USB接口主控制器芯片有几十种,其中比较典型的是Cypress公司的CY7C670xx序列的芯片,论文仅以CY7C67013型号芯片展开FPGA的读写建模设计。该芯片[7]内部集改进的8051内核和USB通信控制引擎于一体,不仅提高芯片集成度,同时在无需外加芯片的条件下即可完成高速USB传输,内部采用了“量子FIFO”独特的处理框架结构,如图8所示,较好地解决了USB高速速率传输的带宽问题。

图8 芯片内部FIFO的Slave-FIFO模式

图中, PKTEND表示包结束,FPGA可通过PKTEND管脚向USB发送一个IN 数据包而不用考虑包的长度;SLRD为从模式的读信号;SLWR为从模式的写信号;SLOE为输出使能信号;FIFOADR[1:0]用于选择与FD连接的端点缓冲区,当其值为00、01、10、11分别对应选择端点EP2、端点EP4、端点EP6、端点EP8。FLAGA、FLAGB、FLAGC为FIFO状态标志位,用于指示FIFO的当前状态。

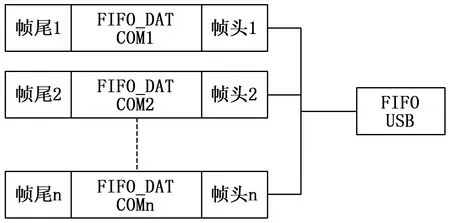

在数据传输过程中,FPGA从串口缓冲中读取相应的打包数据,按照Slave FIFO的传输时序,定时地从各个接口的缓存中读取打包后的数据帧,并按照约定的帧排列方法(如图9所示),组成数据传输结构,即可完成与主机之间高速通讯[8],这种模式的优点是USB芯片不需要内部核芯片参与工作,有效地提高了传输的速度。

图9 多接口缓存数据结构

3 试验验证与分析

为了验证上述方案的正确性,以某软件无线电平台为试验对象,该平台具有USB接口、Xilinx公司的可编程逻辑芯Spartan6-XC6SLX150、40针可编程IO接口,符合多串口数据采集最小系统要求。其中,以6pins/6pins作为目标串口的输入/输出接口,6pins/6pins作为源串口的输入/输出接口,通过FPGA内部设定的状态机实现数据的传输;而上位机以Slave-FIFO传输模式,经USB2.0接口读取FPGA传来数据,经数据包的识别、解包,最终还原出各个串口的数据,最终对发送的源数据和接收的目标数据进行比对。

通过100次模拟实验,每次实验传输65535个字符数据,通过比较发现源数据与接收数据一致,无出现误比特的现象,这结果表明该方案是有效的,试验满足预期要求,达到多路串口同时采集及传输的目的,由此验证了模型的正确性。

4 结论

论文基于FPGA的多通道串口数据采集与传输设计,通过对多路串口数据的同时采集、缓冲及打包的数据流处理思想,采用FPAG+多串口+USB的硬件框架及多种总线不同速率的传输算法,实现了多路串口数据的采集与传输。论文仅从原理上进行有效的验证,在产品的后期设计中,可从小型化、节能化方向出发,选择高集成度、节能型芯片,实现采集与传输模块的即插即拔。

[1]邓竑杰.多路串口到以太网的数据网关的设计与实现[D].昆明:云南大学,2014.

[2]贾佩衡.串口-以太网关转换器设计及其在通信供电监控系统中的应用[D].长春:吉林大学,2011.

[3]李志伟,姚江敏.基于串口通信的控制系统设计[J].科技与创新,2016(16):102-103.

[4]陈标龙,王保成等.基于FPGA和FIFO技术的多串口系统设计与实现[J].计算机测试与控制,2013.21(10):2835-2837.

[5]康春雨.几种常用开关防抖电路简介[J].电子世界,2009(11):43-44.

[6]戴钱坤.一种新型机载防浪涌电压保护电路设计[J].电子技术应用.2011(11):58-60.

[7]王兵兵.基于EZ-USBFX2和FPGA的数据传输系统研究[D].西安:西安电子科技大学,2010.

[8]张 静,叶小芹.基于FPGA的高速USB协议分析仪的设计[J].绥化学院学报,2016(9):152-154.

DesignofDataCollectionandTransmissionSystemofMulti-SerialportsBasedonFPGA

Guo Min1, Zhuang Xinwu2, Wang Xiangdong2, Wu Jincai2

(1.Office of Measurement and Control, Energy Engineering Institute, Yulin University, Yulin 719000,China; 2.PLA 96901 Unit, Beijing 100094,China)

Multi-channels serial data transmission is a new requirement for modern industrial control transmission, and the traditional industrial controller due to the limited number of interfaces, often difficult to meet the requirements. For multi-channel serial ports data collection and transmission of real needs, a data acquisition program based on FPGA for multi-channel serial ports was presented in this paper. The idea of simultaneous acquisition, buffering and packet data processing for multi-channels serial data, and the structure of hardware frame based on FPAG + multi-serials port + USB and bus different rate transmission software processing algorithm was introduced to achieve a multi-channel serial data collection and transmission, In order to verify the effectiveness of the design, a software radio platform as the experimental object was taken to design a 6-way serial transmission system in this paper. And finally through the transmission of the source data and the

data comparison found that the two consistent. The results show that the scheme was effective and the test meets the expected requirements, and achieved the purpose of multi-channel serial acquisition and transmission.

FPGA; multi-channel serial ports; data collection; data transmission

2017-04-30;

2017-05-23。

榆林学院高层次人才科研启动基金(11JK60)。

:郭 敏(1984-),女,讲师,主要从事智能控制方向的研究。

1671-4598(2017)11-0186-04

10.16526/j.cnki.11-4762/tp.2017.11.047

TB47

A