MEMS数字检波器用高精度抽取滤波器的设计与实现

2017-12-02湘潭大学物理与光电工程学院湖南省微光电与系统集成工程实验室金湘亮

湘潭大学物理与光电工程学院 湖南省微光电与系统集成工程实验室 李 凡 金湘亮

MEMS数字检波器用高精度抽取滤波器的设计与实现

湘潭大学物理与光电工程学院 湖南省微光电与系统集成工程实验室 李 凡 金湘亮

针对类似石油勘探应用中采用一位数据输出的高精度MEMS数字检波器,设计数字抽取滤波器对输出数据做进一步处理。首先基于Matlab的simulink建模平台搭建完整的MEMS数字检波器系统模型,使用Filterbuilder工具箱进行数字抽取滤波器设计与建模,结果表明经过数字抽取滤波器滤波后,信噪比仅下降1dB。其次使用Verilog硬件语言实现该滤波器,使用双时钟实现四通道数据分配,降低资源消耗。通过Modelsim与Quarts2进行联合仿真,结果显示通带波纹小于0.02dB,阻带衰减小于-130dB,该滤波器效果达到设计要求。

MEMS;数字抽取滤波器;Verilog

0 引言

MEMS数字检波器广泛应用于航空航天,石油探测,生物学等各种领域。在诸如石油探测的高精度应用中,MEMS数字检波器中的加速度传感器大多使用sigma-delta调制器来获得较好的性能[1][7];文献[2][3]研究了MEMS加速度闭环系统仿真参数;文献[4]中提到搭配一位量化器来获得最高的线性度,以解决量化台阶之间的非线性失配问题,并构成一个稳定的回路。但一位输出数据无法直观地还原原始信号波形,而过采样ADC的噪声整形特性使量化噪声被排至高频率区间。

针对这个问题,本文以简便的滤波器设计工具设计数字抽取滤波器,建模仿真并用Verilog硬件语言实现,用以滤除高频段的量化噪声,同时将一比特数据流还原为原始波形,将输出速率降至奈奎斯特频率。

1 MEMS数字检波器系统结构

传统MEMS数字检波器系统结构如图1所示,输入加速度信号通过一个敏感MEMS器件引起电容变化,通过一个C/V读出电路将电容变化转为电信号,继而通过过采样ADC进行采样转为数字信号,一位量化器将输出表达为1bit数据流,这种方法解决了量化台阶之间的非线性失配问题。1bit数据流输出以静电力反馈形式反馈至敏感MEMS器件以维持器件的平衡,构成伺服系统。数字抽取滤波器用以处理量化器后输出的1bit数据,输出一个原始信号波形,并滤除高频段量化噪声[12]。

图1 系统结构图

MEMS数字检波器的过采样ADC基带带宽为500Hz,采样率为128,故输出信号速率为128kHz。

2 数字抽取滤波器分析及Matlab设计

针对输出1bit数据流速率为128kHz的高精度MEMS数字检波器,对其进行128倍的抽取,输出速率为1kHz的信号。数字抽取滤波器的设计指标如表1所示。

表1 数字抽取滤波器的设计指标

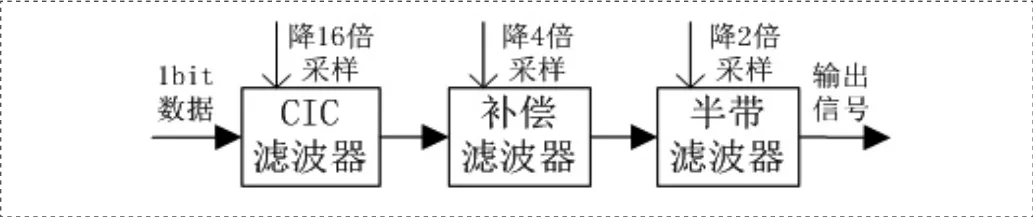

图2 降采样示意图

传统数字抽取滤波器设计采用手工计算FIR滤波器,过程繁琐[5][6]。现今各种滤波器设计软件已经成熟,本文利用Matlab中Filterbuilder工具箱对以上滤波器进行设计并导出simulink模型,输入具体设计参数如表2所示。

2.1 CIC滤波器

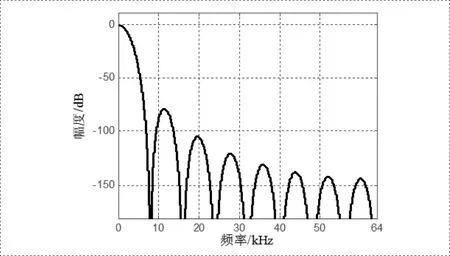

作为整个数字抽取滤波器的第一级,CIC滤波器的主要作用是实现较大的抽取数,为后级滤波器节省资源,同时CIC滤波器可以增大阻带衰减,接近设计指标[9]。在Filterbuilder工具箱输入各项指标后可生成CIC幅频响应图。

图3 CIC滤波器幅频图

如图3所示,依据我们的设计指标生成了一个6阶16抽取的CIC滤波器。

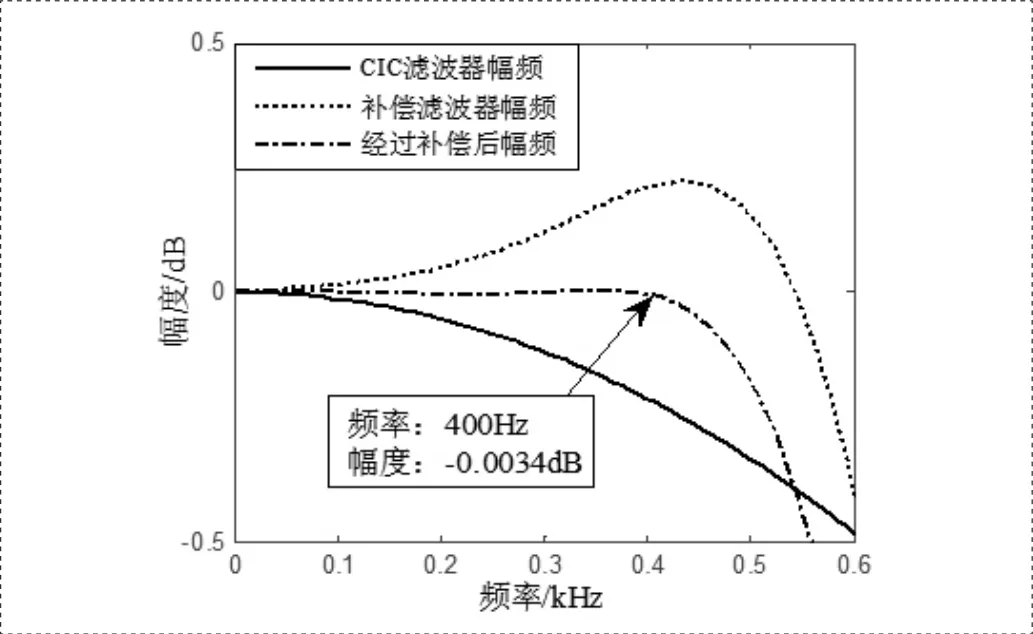

2.2 补偿滤波器

CIC滤波器在实现较大幅度的阻带衰减的同时,通带中也会有相应较大衰减,这时需要一个补偿滤波器来补偿其通带中的衰减,这里需要注意的是,补偿滤波器的阻带起始频率如果越接近最终半带输出的阻带起始频率,滤波效果会更好但是滤波器阶数会变得非常大,这样做会消耗大量资源,这里经过权衡后将阻带起始频率设置在1500Hz,生成43阶的补偿滤波器,使用fvtool可视化工具可以查看补偿效果如图4所示。

图4 补偿滤波器补偿效果图

可以看到经过补偿后,通带截止频率点400Hz处的幅度为-0.0034dB,满足设计指标。

图5 滤波器系统整体级联图

2.3 半带滤波器

使用半带滤波器作为整个滤波器最后一级,与一般的FIR滤波器相比,半带滤波器的通带特性比较平坦,过渡带的带宽也比较容易控制,并且滤波器的系数有一半为零,因此减少了设计的硬件开支,减少了滤波器整体的面积和功耗。

通过Fvtool工具将滤波器整体级联图作出如图5,可以看到通带内波纹远小于0.02dB,阻带衰减也达到小于-130dB要求。

3 simulink仿真验证

在simulink平台中搭建MEMS数字检波器的模型如图6所示。输入加速度经由MEMS加速度传感器前端电路,输出一位数据流,一位数据流经一个反馈系数转为静电力反馈至MEMS数字检波器的敏感器件,用以将MEMS敏感器件回归原位,构成伺服系统[4]。

图6 MEMS数字检波器系统simulink模型

输入信号为一个低频的幅度为1g的加速度信号与一个幅度为0.4g的高频噪声信号相叠加,图7分别为输入信号,输出1bit数据与最终输出信号的示波器示意图。

图7 示波器示意图

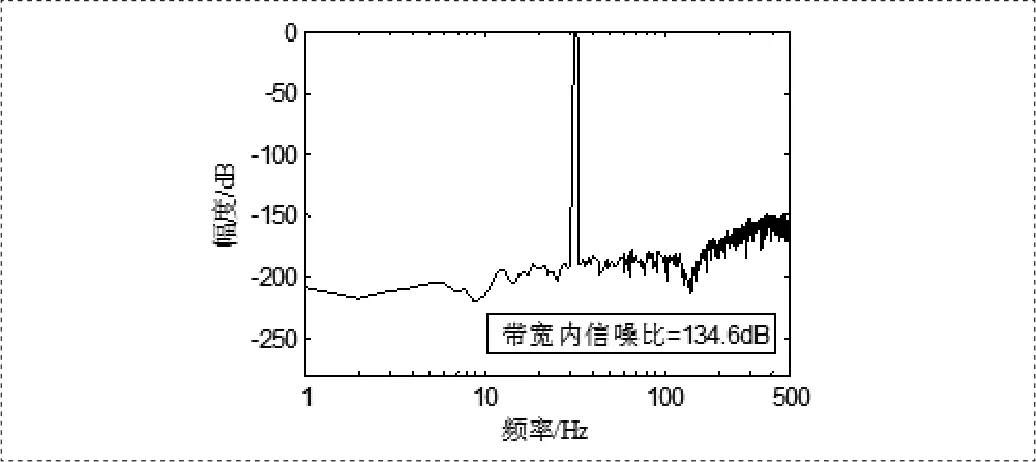

可以看到,输入信号通过MEMS数字检波器前段电路后输出极高速率的1bit数据流,表现为示波器中密集的1与-1,再通过所设计生成的数字抽取滤波器组进行信号处理,输出的最终信号完美地保留并还原了原始的加速度信号波形,滤除了高频噪声信号。对输出1bit数据流与最终输出数据进行频谱分析如图8,9所示[11]。

从图8中可以看到输出的1bit数据流包含了频率固定的低频的加速度信号,高频噪声信号以及高频段大量的量化噪声信号,带宽内信噪比为135.7dB。图9中可以看到高频段的噪声信号与量化噪声信号都已完全被滤除,只保留了带宽内的加速度信号,同时带宽内信噪比只下降了约1个dB。

图8 1bit输出数据频谱分析图

图9 滤波器输出数据频谱分析图

4 Verilog硬件语言实现

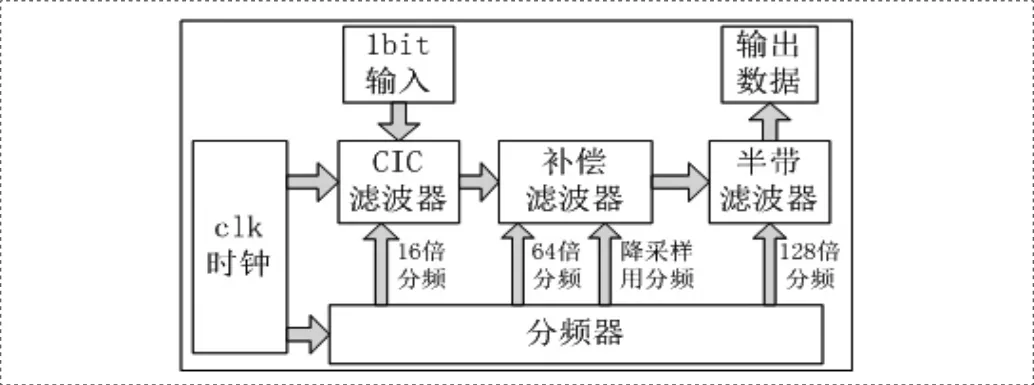

图10 系统框架图

在Matlab中对滤波器进行建模仿真后,确定simulink模型的正确性后,可以进行编写Verilog代码进行滤波器的硬件实现。Filterbuilder支持直接生成Verilog代码,但是自动生成的Verilog代码冗长繁杂[11]。在simulink模型中可以查看底层电路和滤波器系数,依据底层电路与滤波器系数可以编写Verilog代码,整个硬件系统框架图如图10所示。

系统采用计数器的方式进行时钟分频,分别进行16倍,64倍,128倍分频,并向补偿滤波器产生一个降采样用分频时钟,这个降采样分频时钟频率与64倍分频后的时钟频率一样,相位相差半个周期,目的是以两个时钟的上升沿与下降沿实现补偿滤波器中四通道数据分配,以满足补偿滤波器降4倍降采样的需要,实现波形如图11所示。

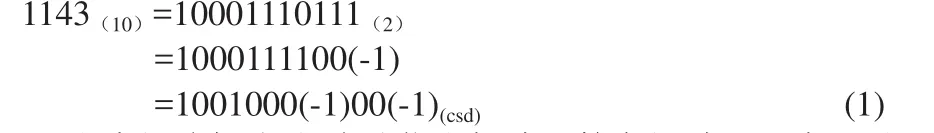

图11 双时钟实现四通道数据分配

在实现滤波器中的系数时,采用CSD编码可以大大减少资源消耗[6]。其原理是将系数转化为由0,1和-1组成的编码,进行优化后产生最少非零元素的编码,保证用最少的加减运算和移位运算实现系数进行乘法运算后的结果,在公式(1)中通过一个例子演示了CSD编码的过程。

可以看出原本需要7次移位和加法运算在经过CSD编码后只需4次移位和加减法运算便可实现原系数乘法运算的结果。

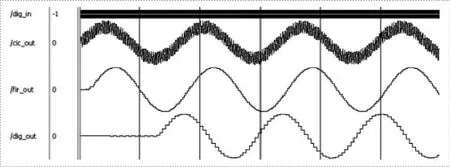

图12 联合仿真波形

在通过Modelsim软件功能仿真后,在Quaters2软件中配置Altera公司的cycloneIII-EP3C120F484C8型号FPGA板,编写Testbeach测试文件,通过编译并进行仿真[7]。将Matlab工作区的MEMS数字检波器量化器后1bit数据输出导出,利用Testbeach输入至Quaters2软件中,与Modelsim进行联合仿真得到下图波形结果。

图12中由上至下依次为输入1bit数据,CIC滤波器输出数据波形,补偿滤波器输出数据波形与半带滤波器即最终输出数据波形。可以看到,数字抽取滤波器成功实现了抽取与滤波的功能。

5 总结

本文针对一位输出的高精度MEMS数字检波器利用Matlab设计了一套完整的数字抽取滤波器系统,在simulink平台中建模并仿真,结果显示滤波后的信噪比只下降了1dB,表明滤波器性能达到期望指标。其次使用Verilog代码实现整个数字抽取滤波器系统,通过优化代码减少资源消耗。最后通过Quarts2软件配置FPGA开发板与Modelsim软件联合仿真,结果表明该滤波器成功实现了抽取与滤波的功能,满足设计要求,有较好的实际应用价值。

[1]Liang W,Yang C,Qiao D.On the design of feed-forward interface for MEMS based accelerometers[J].Analog Integrated Circuits and Signal Processing,2012,72(1):3-10.

[2]Petkov V P,Boser B E.High-order electromechanical sigma-delta modulation in micro-machined inertial sensors[J].Circuits and Systems I:IEEE Transactions on,2006,53(5):1016-1022.

[3]ZHANG F,JIN X,WANG L.Modeling and test result of closedloop MEMS accelerometer with wide dynamic range[J].Microsystem Techn ologies,2016,22(3):653-657.

[4]Wang L,Xie L,Jin X.A design of order-adjustable sigma-delta modulator for high performance micro-machined accelerometers[J].Analog Integrated Circuits and Signal Processing,2014,80(1):77-84.

[5]LIU X.A High Speed Digital Decimation Filter with Parallel Cascaded Integrator-Comb Pre-Filters[C]//International Congress on Image and Signal Processing.IEEE,2009:1-4.

[6]LI L,XIAO yue L I,ZENG J,et al.Design of 24-bit Delta-Sigma A/D digital decimation filter[J].Journal of Beijing Jiaotong University,2016.

[7]李宗敏,张法全,王国富,等.基于FPGA高精度微震信号采集系统设计[J].仪表技术与传感器,2016(4):108-110.

[8]李秀花,马雯.基于FPGA的IIR数字滤波器设计与实现[J].电子技术,2016(5).

[9]杨静.宽带∑-△A/D转换器中数字抽取滤波器的设计与验证[J].电子设计工程,2013,21(22):168-170.

[10]刘忠超,张长春,李卫,等.0.18μm CMOS Σ-ΔADC用数字抽取滤波器设计[J].微电子学与计算机,2014(6):44-47.

[11]杨翠娥.CIC抽取滤波器的MATLAB设计及FPGA实现[J].山西电子技术,2017(1):46-48.

[12]骆丽,李晓玥,曾俊琦,等.一种24位Delta-SigmaA/D数字抽取滤波器设计[J].北京交通大学学报,2016,40(5):45-49.

李凡(1993—),硕士研究生,现就读于湘潭大学,主要研究方向为信号处理与集成电路设计。

金湘亮【通讯作者】(1974—),教授,主要研究方向为传感与信息获取、集成电路与系统。

Design and realization of high precision decimation filter for MEMS digital geophone

Li Fan,Jin Xiang-liang

(Hunan Engineering Laboratory for Microelectronics ,Optoelectronics and System on a chip,Faculty of Physics and Optoelectronics Xiangtan University,Xiangtan 411105 China)

In view of the application of oil exploration,a high-precision MEMS digital geophone with one bit output data is used,the digital decimation filter is designed to further process the output data.A MEMS digital geophone system model is complete based on Simulink platform of Matlab,the Filterbuilder toolbox is used to design and modeling the digital decimation filter,the results show that after the digital decimation filter,the SNR decreased by 1dB .Then use the Verilog HDL to realize the filter,using dual clock to achieve four channel data allocation,reduce resource consumption.Through the joint simulation simulation of Modelsim and Quarts2,the simulation result shows that the passband ripple is less than 0.02dB,and the stopband attenuation is smaller than -130dB,the filter effect meets the design requirements.

MEMS;Digital decimation filter;Verilog

国家自然科学基金重点项目(61233010);国家自然科学基金面上项目(61774129);国家自然科学基金青年科学基金项目(61704145);湖南省自然科学杰出青年基金项目(2015JJ1014)。