基于OpenOCD和DAP的嵌入式远程调试系统研究与设计

2017-12-01余梓奇章建雄阎燕山

余梓奇,章建雄,马 鹏,阎燕山

(1.中国电子科技集团第三十二研究所上海201808;2.中国航空无线电电子研究所上海200241)

基于OpenOCD和DAP的嵌入式远程调试系统研究与设计

余梓奇1,章建雄1,马 鹏1,阎燕山2

(1.中国电子科技集团第三十二研究所上海201808;2.中国航空无线电电子研究所上海200241)

为了解决传统调试器与自主可控芯片兼容性不强的问题,文中针对自主设计的一款嵌入式CPU,分析了远程调试的原理,研究并设计了一种基于OpenOCD和DAP(调试访问端口)的远程调试系统。该系统通过OpenOCD向目标芯片发送调试命令,经过JTAG仿真器传给目标芯片的JTAG接口,并通过DAP生成总线事务完成调试操作。经实际应用表明,该系统支持插入断点、单步执行、读写寄存器和存储空间等调试功能,可作为GDB服务程序与GDB集成以实现更强大的调试功能,具有兼容性强,稳定性强,可扩展性好的特点。

远程调试;OpenOCD;调试访问端口;JTAG仿真器

嵌入式远程调试系统是嵌入式系统开发的重要工具,可极大降低嵌入式软件开发的难度。嵌入式开发中的调试工作受限于嵌入式软件运行的资源,不能够直接在开发板上运行调试软件,调试软件与被调程序不得不在两个不同的环境中运行,因此嵌入式调试必须采用远程调试的方式,也称交叉调试[1],被调软件和调试器之间一般通过并口、USB接口或者网络接口连接。

国外在嵌入式调试器方面一直领先,国内普遍采用国外的工具,价格比较昂贵,而适配自主可控的国产芯片的调试系统相对缺乏,这就对嵌入式开发环境提出了新的要求,因此文中针对自主设计的嵌入式CPU研究并设计了一种基于OpenOCD和DAP的远程调试系统,以适应目前嵌入式开发的需求。该调试系统可适用于没有操作系统的目标机,通过OpenOCD向目标芯片发送调试命令,目标芯片的DAP收到命令并发出总线事务实现对CPU和外围设备的访问。

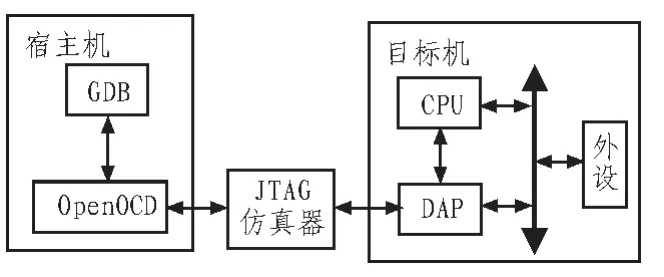

1 远程调试系统结构

本远程调试系统包括的部件有:GDB、OpenOCD、JTAG仿真器和目标机调试访问端口。系统架构如图1所示。其中OpenOCD和GDB运行在宿主机端,JTAG仿真器连接宿主机和目标机,目标机调试访问端口DAP解析收到的调试命令,控制处理器执行调试操作。本系统实现的关键在于设计了独立的DAP以及在OpenOCD中设计了符合目标芯片的调试特性的接口函数。

图1 远程调试系统架构

1.1 OpenOCD

OpenOCD(Open On-Chip Debugger)是一个开源的通用上位机调试软件,与GNU GCC工具链联合作为多种嵌入式目标系统的调试器所用,支持所有系列的ARM处理器以及MIPS和FPGA等核心的芯片,也支持众多商用的JTAG仿真适配器[2]。由于OpenOCD的开源性,可根据不同的目标芯片改写相应的操作函数以适配各个芯片,使得基于OpenOCD搭建的调试系统具有兼容性强,可扩展好的特性[3]。OpenOCD相较于其他调试器的优势在于,可以直接读写物理地址和核内部寄存器,更接近硬件层面,对于测试硬件设计有不小帮助[4];

1.2 JTAG仿真器

大多数仿真器都由一个位于主机和被调试系统之间的硬件电路组成。一端通过USB接口与主机端连接,另一端通过JTAG接口与目标板上的微处理器的调试电路连接。

仿真器中主要部分为USB协议栈,以及JTAG接口。JTAG仿真器接收到宿主机通信端口发出的信号后,将其转换成标准的JTAG信号发给目标机JTAG接收端,目标机完成指定的调试操作后再将结果反馈给宿主机[5]。

1.3 调试访问端口

调试访问端口DAP(Debug Access Port)主要由调试端口(DP)和访问端口(AP)两部分组成。DAP作为一个整体的本质作用是将JTAG接口传来的数据翻译成不同的系统总线事务[6]。JTAG-DP接收到JTAG信号,经过DAP内部总线控制访问端口AP;通过AHB-AP可以访问到挂载在AHB总线上的所有从设备;APB-AP仅能访问与Debug APB连接的处理器核,通过访问处理器核中的Debug逻辑实现调试操作[7]。DP和AP内部也有相应的控制寄存器,主机端的调试器可以独立地访问这些寄存器,以获取DAP的运行情况,且不干扰目标芯片的运行。

1.4 GDB

GDB作为GNU开源组织下的一个调试工具,具备其他商用调试器的所有功能。GDB远程调试的基本原理是通过 RSP(Remote Serial Protocol)协议实现调试功能。RSP协议定义了消息的读写格式,控制应用程序的调试以及相应状态[8]。GDB在此系统中不是必须的,根据实际调试需求而定。OpenOCD与GDB联合使用时可视作一种GDB Server[9]。

2 调试系统设计实现

本节详细介绍本远程调试系统中调试访问端口和OpenOCD调试函数的具体设计实现。

2.1 DAP设计原理

DAP由调试端口DP和访问端口AP组成。数据流经DP传给AP,最后流向待访问的调试资源。DAP结构图如图2所示。

图2 DAP结构图

调试端口JTAG-DP可以分成TAP控制器、扫描链、指令系统3个部分[10]。TAP控制器事实上是一个有限状态机,由输入信号TMS和时钟TCK控制状态机的运行,提供控制信息。JTAG-DP内部包括两大类扫描链:指令扫描链(IR scan chain)和数据扫描链(DR scan chain)。根据状态机的不同状态首先指定指令或数据寄存器组,然后控制寄存器组的捕获、移位、更新等操作。如表1所示定义了5种JTGA指令。如果是DPACC或APACC指令,接下来则换到数据扫描链,数据经TDI移入数据寄存器,写数据在更新状态发出,读数据则在下一次的捕获状态读取,经TDO读出。

表1 JTAG指令

访问端口AHB-AP和APB-AP内部分为主从端,Slave端负责接收DP传来的命令和数据,Master端负责产生相应的总线事务[11]。本系统设计APBAP与Debug APB总线相连,可访问到核内的调试资源,控制CPU运行或插入硬件断点和观察点;AHBAP与AHB总线相连,可以访问到所有挂载在AHB总线上的外设。由于对核的访问和对外设的访问是通过不同的线路进行,故该调试系统可以实现访问外设而不影响核内指令的正常运行。

调试器对DAP的访问可分为三级[12]:对DP的访问,对AP的访问和对系统资源的访问。这三级是递进的关系,要想访问系统资源,必须先访问DP和AP。三级访问结构如图3所示。首先访问DP,配置APSEL寄存器指定要访问的AP寄存器;再访问AP的Bank0中的寄存器TAR和DRW,分别指定要访问系统资源的地址和读写数据;最后AP发出相应的总线事务,完成对调试资源的访问。可以配置AP中的CSW寄存器选择访问模式,例如要连续访问一段地址,可以使用地址自增模式,每完成一次读写访问便将AP-TAR中的地址加4,这样每次只需操作DP访问一次AP-TAR,不用重新写值改变地址。通过这三级访问最终实现嵌入式系统的调试和对DAP本身的控制。

为了能够控制处理器的状态,设计DAP以存储空间映射(Memory map)的方式访问处理器核的调试接口[13]。核中的调试相关寄存器映射到Debug APB上的4KB地址空间。向APB-AP TAR寄存器中写入相应地址即可访问到调试寄存器。

2.2 OpenOCD设计原理

基于OpenOCD的开源性,可以根据不同的目标芯片进行定制设计和裁剪。OpenOCD可主要分为GDB服务模块、DAP访问模块和目标芯片调试模块这样三个模块。另外还有JTAG仿真器驱动模块,主要是调用现有的libusb库函数根据不同仿真器的特性来驱动USB接口,进而驱动JTAG仿真器[14],这里不再赘述。下面介绍主要功能模块的设计原理。

图3 DAP三级访问结构示意图

2.2.1 GDB服务模块

GDB服务模块类似于GDB Server,主要包括3个子模块[15]:1)通信连接模块,作为GDB与OpenOCD中间的桥梁,实现两者的通信。GDB服务模块启动后,将调用一个线程监听通信连接,当GDB发起连接时,将通知后续模块建立调试连接;2)事件监听模块,循环监听调试事件并跟踪某个进程的进行;3)命令解析模块,解析RSP包的格式,提取调试命令内容交给OpenOCD执行,收到返回数据后再封装成RSP数据包。

2.2.2 DAP访问模块

DAP访问模块根据上一节提到的DAP三级访问原理,实现了扫描链的驱动,DAP寄存器的访问,依据不同的上层调试操作选择不同的AP访问系统资源。如图4所示是DAP的访问流程图。该模块具体分为两部分:1)JTAG协议模块,实现TAP状态机的状态转换,根据配置文件中对时钟的设置改变TCK的速度,在每个TCK节拍到来时,指定TMS完成状态跳转。设计jtag_ir_scan()和jtag_dr_scan()函数实现JTAG指令的选择和数据扫描链的移位;2)DAP协议模块,分析调试操作模块的不同命令,首先调用jtag_ir_scan()函 数 指 定 DP操 作 为 DPACC或APACC,接着调用jtag_dr_scan()函数载入数据选择AP和指定读写操作。访问结束后调用jtagdp_transaction_endcheck()函数检查访问是否正常,主要根据数据扫描链后3位的值,查看当前DPCTRL/STAT的OVERRUN和STICKYERR位是否置1,如果不正常就尝试重新访问并向上层反馈错误代号。

图4 DAP访问流程

2.2.3 目标芯片调试模块设计

根据目标处理器的类型,本模块设计实现的是通过调用DAP访问模块中的函数,访问处理器中DEBUG相关寄存器和外设资源,实现让目标处理器执行具体调试操作。下面重点讨论各项功能的实现。

1)停止运行:控制CPU停止运行当前指令,进入调试状态,首先向DRCR_HALTREQ位写1发出停止请求,该操作会产生调试请求异常,使CPU保存现场。接着写DSCR_ITRen位写1使能ITR功能,以便在后续的调试操作中向CPU发送指令。读DSCR字获取当前CPU状态,DSCR_HALTED位为1说明CPU已经停止进入调试状态。

2)插入断点:断点是调试器控制目标程序执行的基本手段。这里断点分为软断点和硬断点,软断点是将待插入断点处的机器码换成特殊的BKPT指令,当CPU执行到这条指令时会产生断点异常使CPU进入调试状态;硬断点是通过向BVR中写待插入断点的地址,CPU每次执行指令前会将PC与BVR比较,地址匹配便产生断点异常,打断这条指令的执行,使CPU直接进入调试状态。从速度上讲,设置硬件断点更快。

3)单步执行:实际上是一个删除断点——插入断点——恢复执行的过程。首先删除当前停止位置的断点,再向下一条指令位置处插入新的断点,然后恢复执行,CPU执行完当前指令会触发下条指令的断点。

4)恢复执行:恢复CPU运行指令,离开调试状态。和停止运行操作相似,首先向DSCR_ITRen位写零关闭ITR功能,再DRCR_RESTART位写1发出重新运行请求,控制CPU恢复现场。如果没有指定恢复执行的地址,则在当前PC处开始执行,如果指定了地址,在离开调试功能前会向PC写入新地址,控制CPU从这里开始执行。

5)读写调试资源:分两种情况,如果访问CPU内的寄存器是通过ITR执行相应指令,再通过RX、TX完成数据传输。如果访问CPU外的存储空间是直接通过AHB总线访问。

2.3 集成GDB

OpenOCD可以与GDB协同工作,接收GDB发送来的命令传给目标机。相对OpenOCD的调试操作,GDB提供了更强大并更“上层”的调试功能。GDB可以直接面向源码级调试,可以针对函数名或语句行号插入断点,并以语句单步执行[16]。在GDB环境中输入target remote localhost:3333命令即可与OpenOCD建立连接,端口号可以在目标芯片配置文件中修改。连接成功后使用load命令载入待调程序。与调试本地程序不同,远程调试是通过“c”命令而不是“r”命令使待调程序开始执行。其他命令与本地调试类似,所以对于熟悉GDB操作的开发人员,可以使用GDB配合OpenOCD高效地调试嵌入式软件程序。

3 测试结果

文中针对自主设计地嵌入式CPU,选用J-link作为JTAG仿真器,在ubuntu系统上启动OpenOCD,向目标芯片发送调试命令。测试过程为首先向芯片下载一个根据U-boot裁剪的boot程序,然后在该程序所在内存处的的不同位置插入断点,观察程序执行情况。

OpenOCD连接成功后首先读取JTAG仿真器和DAP的相关信息,以比较是否和配置文件中声明的相同,同时还读取了核中的调试寄存器,获取芯片信息,如支持的硬件断点和观察点个数。

使用halt命令使处理器停止运行后即表示进入调试状态,使用load_image命令下载程序到指定地址并改变PC指针到指定地址开始执行。通过bp命令插入断点,处理器执行到断点处停止执行,可以看到停止时的状态信息。单步step操作执行到下条指令再恢复运行。程序最后停止在0x00200380处,这与boot程序的最后一条指令地址一样,说明处理器执行完了该程序的所有指令,操作过程如图5所示。

图5 OpenOCD操作过程

4 结 论

当前我国在嵌入式软件开发中所使用的调试工具多为国外产品,价格昂贵,不利于推广。本文研究了嵌入式系统远程调试技术,自主研发的嵌入式处理器设计了专门的DAP模块,在调试器OpenOCD的基础上设计了相应的调试操作函数接口,实现了高效稳定的远程调试系统。本文提出的远程调试设计方法对其他嵌入式调试系统设计具有一定参考价值。

[1]马艳.基于事件循环机制的嵌入式应用级交叉调试器的研究[D].武汉:华中科技大学,2013.

[2] Wootton C.DebuggingYourApplication[C]//Beginning Samsung ARTIK.Apress,2016:325-331.

[3]黄子晨,李德华.基于OpenOCD和JTAG的嵌入式交叉开发环境[J].仪器仪表用户,2012,18(2):470-478.

[4]Mike Anderson.Using OpenOCD JTAG in Android Kernel Debugging:Making Android Driver Work-(PPT)[C]//Embeded systems conference 2013,San Jose,California,USA:ESC Silicon Valley,2013.

[5]吴亚杰.基于EJTAG的OCD调试方案的研究与实现[D].青岛:中国海洋大学,2012.

[6]徐文昌.SoC调试跟踪系统的设计与实现[D].西安:西安电子科技大学,2013.

[7]张鹏,樊晓桠,黄小平.基于总线访问的片上调试方法研究[J].计算机测量与控制,2014(2):510-512,518.

[8]况阳.支持USB的嵌入式软件远程调试器的设计与实现[D].成都:电子科技大学,2011.

[9]Beneder R,Kramer M,Brejcha P.A two stage approach for a cost-effective and versatile debugging unit and starter platform[C]//Mechatronics and Embedded Systems and Applications(MESA),2012 IEEE/ASME International Conference on.IEEE,2012:330-335.

[10]刘慧.基于SOC嵌入式处理器调试系统的开发与研究[D].武汉:武汉纺织大学,2013.

[11]Joseph Yiu.ARM Cortex-M3权威指南[M].姚文祥.北京:清华大学出版社,2014.

[12]Esliger J L,Foley D.Integrated circuit with secure boot from a debug access port and method therefor:U.S.Patent 8,156,317[P].2012-4-10.

[13]王哲宇.基于CoreSight接口的ARM跨平台调试系统的研究与实现[D].上海:华东师范大学,2015.

[14]Beneder R.Development of an OpenOCD compatible Debugger for ARM-CMARMJTAG[D].University of Applied Sciences Technikum Wien,2011.

[15]殷绍剑,雷航,詹瑾瑜.嵌入式远程调试原理研究与实现[J].计算机应用与软件,2014(6):240-243.

[16]任艳伟.基于acoral操作系统的调试器的研究与设计[D].成都:电子科技大学,2012.

Research and design of embedded remote debugging system based on OpenOCD and DAP

YU Zi⁃qi1,ZHANG Jian⁃xiong1,MA Peng1,YAN Yan⁃shan2

(1.The32nd Research Institute of China Electronics Technology Group Corporation,Shanghai201808,China;2.China Aviation Radio Electronics Research Institute,Shanghai200241,China)

In order to solve the problem of the compatibility between the traditional debugger and selfcontrollable chip.In view of the self-designed embedded CPU,this paper analyzes the principle of remote debugging,researches and designs a remote debugging system based on OpenOCD and DAP(debug access port).The system sends the debug command to the target chip through OpenOCD,these commands are sent to the JTAG port of the target chip by JTAG emulator and completes the debug operation through DAP generating bus transaction.The experiment and application show that this system supports insertion breakpoints,single-step execution,read or write registers and storage space and other functions,the system also can integrate with GDB as GDB server program to achieve more powerful debugging features,with strong compatibility,strong stability,good scalability.

remote debugging;OpenOCD;debug access port;JTAG emulator

TP302.1

A

1674-6236(2017)22-0149-05

2016-10-23稿件编号:201610134

余梓奇(1992—),男,湖北武汉人,硕士研究生。研究方向:计算机系统结构、数字系统设计。