全差分结构低功耗CMOS运算放大器设计*

2017-11-14肖莹慧中南财经政法大学武汉学院武汉430000

肖莹慧(中南财经政法大学 武汉学院, 武汉 430000)

全差分结构低功耗CMOS运算放大器设计*

肖莹慧

(中南财经政法大学 武汉学院, 武汉 430000)

为了减小低电源电压以及短沟道效应对放大器的影响,获得低电压高增益的放大器,提出了一种基于65 nm CMOS工艺技术的全差分运算跨导放大器(OTA).采用基于增益增强技术的折叠共源共栅拓扑结构,使放大器具有轨到轨输入及大输出摆幅特性,同时兼备高速、高增益及低功耗优点.电路仿真结果表明,其直流增益为82 dB,增益带宽为477 MHz,相位裕度为59°.正常工艺角下稳定时间为10 ns,稳定精度为0.05%,而功耗仅为4.8 mW.

CMOS集成电路; 增益增强; 运算跨导放大器; 高速; 高增益; 低功耗; 折叠共源共栅结构; 高增益带宽

随着MOSFET沟道长度不断缩小,晶体管的速度变得越来越快,效率也越来越高.伴随着低电源电压和短沟道效应而来的,例如厄立电压,减小了晶体管的增益,但在深亚微米技术上实现了较高增益,使得宽输入和宽输出电压范围放大器用于高性能模拟电路成为一项极具挑战性的任务.在A/D转换器、开关电容滤波器和采样保持放大器等模拟电路中,速度与精度是放大器最为重要的两个参数[1-3].稳定速度主要取决于单位增益频率和单极稳定时间,而高稳定精度是由运算放大器的高直流增益决定的.然而,对放大器的速度和增益进行优化时经常导致自相矛盾的结果.放大器通常采用低偏置电流的长沟道器件来进行多级放大器设计以获取高直流增益,而使用高偏置电流的短沟道器件来进行单极放大器设计以获取高速度.文献[4]介绍了一种增益增强电路,其能够在不降低运算放大器增益带宽的情况下,提高放大器的直流增益;文献[5]首次将该技术应用于折叠式共源共栅运算放大器,在过去的几年中,增益增强共源共栅放大器的正确设计过程成为了人们研究的课题;文献[6]得到了直流增益为95 dB,增益带宽为412 MHz的共源共栅放大器,其功耗为12.8 mW;文献[7]实现了直流增益为106 dB,增益带宽为57 MHz的共源共栅放大器;文献[8]实现了一个复杂的三级放大器结构,其直流增益为84 dB,增益带宽为200 MHz,而功耗仅有10 mW.本文提出了一种全差分结构的运算放大器,其直流增益为82 dB,单位增益频率为477 MHz,而功耗仅为4.8 mW.

1 增益增强技术原理

运算放大器增益增强的基本思想是基于在负反馈回路上设置晶体管M2的漏极电压,其中,IØ为电流源.图1为增益增强共源共栅增益级电路.附加增益级的增益Aaux增加了该电路的输出阻抗,电路输出阻抗为

Rout= (gm2ro2(Aaux+1)+1)ro1+ro2≈

gm2ro2Aauxro1

(1)

式中:gm2为MOS管M2的跨导;ro1、ro2分别为MOS管M1、M2的输出电阻.增加的输出阻抗使得总增益增强了几个数量级,总增益为

Atot=gm1Rout=AorigAaux

(2)

式中:gm1为MOS管M1的跨导;Aorig为原始增益.

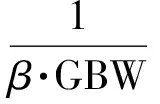

为了使放大器有较好的稳定性,同时使稳定时间较小,其单位增益频率ωu,a的范围被限定为

βωμ,m≤ωu,a≤ω2p,m

(3)

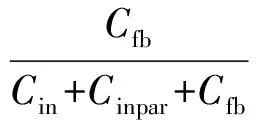

式中:βωμ,m为闭环主导极点频率;ω2p,m为第二极点单位增益带宽频率;ωμ,m为主放大器的开环单位增益频率;β为闭环反馈系数(运算放大器的输出电压被反馈到运放输入的比例分数),可通过运算放大器的输入电容Cin、寄生电容Cinpar以及反馈电容Cfb来定义,其表达式为

(4)

典型的增益增强结构如图2所示.增益增强折叠共源共栅结构通常被选为低电源电压应用的最佳结构,与非折叠共源共栅增益增强结构相比较而言,折叠共源共栅增益增强结构具有更大的输出摆幅,同时单极滚降频率响应也更好.对于附加放大器而言,主要有单端与全差分两种结构,单端结构的附加放大器有两个缺点:1)放大器内部的电流镜会使其增加额外的极点;2)偏置电路会产生噪声.全差分放大器则需要共模反馈电路(CMFB).

图1 增益增强共源共栅增益级电路Fig.1 Gain enhancement cascode gain stage circuit

图2 折叠共源共栅结构的全差分放大器Fig.2 Fully differential amplifier withfolded-cascode structure

2 电路设计与分析

2.1 参数规格

放大器的总相对稳定误差ε是静态误差εs和动态误差εd两者之和,其表达式为

ε=εs+εd

(5)

考虑到放大器被用于电荷转移开关电容电路中,εs可由有限的直流增益A来获得,则有

(6)

在此种情况下,εs应小于0.2%,取β=0.5,这意味着增益应该至少为60 dB.

动态误差εd的计算表达式为

(7)

(8)

式中:τ为时间常数;T为放大器稳定时间;GBW为增益带宽.

为了使εd=0.1%,放大器的稳定时间必须小于10 ns.当稳定时间T=8τ时,由式(8)可得运算跨导放大器的增益带宽至少为120 MHz.然而,考虑到转换时间tslew(本文中转换时间约为3τ),放大器的增益带宽应大于170 MHz.

2.2 主放大器

对于带有P沟道输入对的增益增强电路结构而言,其输入电压范围为

VSS≤Vin≤VDD-|VDsat|-|VTP|

(9)

对于带有N沟道输入对的增益增强电路结构而言,其输入电压范围为

VSS+VDsat+VTP≤Vin≤VDD

(10)

式中:VSS为接地电压;VDD为电源电压;VDsat为饱和漏源电压;VTP为阈值电压.

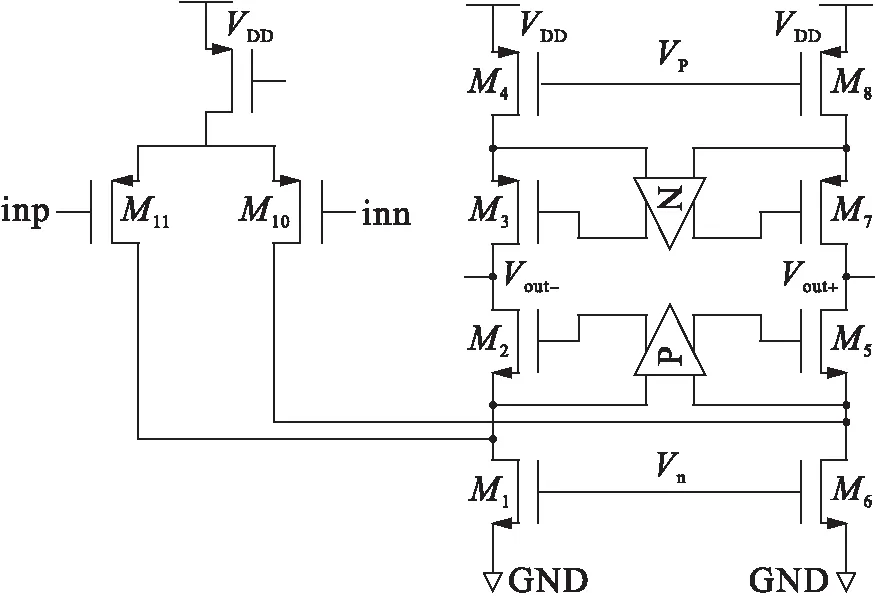

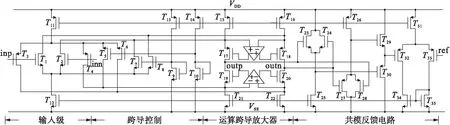

此时输入电压的可用范围约为电源电压的一半,这在低电压应用中是不可接受的.图3为本文提出的具有共模反馈电路的运算放大器,在具有轨到轨输入级[9-10]的常规紧凑型运算放大器中,N沟道输入对T1~T2与P沟道输入对T3~T4并联放置,以处理从轨到轨的信号.为了使跨导作为共模输入电压常数的函数,简单的前馈方法是应用电流开关T5~T8.电流开关由两个晶体管组成,且组成电流开关的这两个晶体管的漏极分别与相对应的输入晶体管的漏极相连,例如,图3中电流开关T5和T6的漏极分别与输入晶体管T4与T3的漏极相连;而电流开关T7、T8分别与输入晶体管T2、T1的漏极相连.电流开关通过将电流添加到输出级的输出,使输出级的电流不作为共模输入电压的函数而改变.由于可以使用相对较小的电流开关晶体管,因此能够使其对放大器产生的噪声较小.

图3 具有共模反馈电路的全差分运算放大器电路图Fig.3 Fully differential operational amplifier circuit with common mode feedback circuit

对于输出级的晶体管而言,主要有以下几个限制条件:1)输出分支上所有晶体管的饱和电压之和必须能够满足阈值电压的要求,这体现在电源电压与输出电压之差要大于分支上所有晶体管的饱和电压与阈值电压之和,因而导致电压供应与期望的输出电压摆动之间有差值;2)级联晶体管T17~T20必须拥有足够高的跨导,从而增大共源共栅放大器的输出电阻,进而使放大器获取足够大的直流增益;3)有源负载T15~T16和T21~T22的饱和电压必须达到最大值,才能减小有源负载对输出级造成的噪声.这些限制条件强调了在将饱和电压拟合到电压余量和最小化噪声贡献之间的权衡.该做法的优势是使级联晶体管的跨导达到最大,这不仅增强了放大器的直流增益,同时减小了级联晶体管的饱和电压,从而使有源负载具有更大的饱和电压,而不超过电压余量.

2.3 辅助放大器

辅助增益放大器采用具有全差分输出的折叠共源共栅运算放大器,其分别在顶部和底部辅助放大器中采用N沟道和P沟道差分对.T17~T20的源极栅极电容形成米勒电容,连接在附加放大器的输入和输出之间.在折叠节点处看到的电容从Cgs被提升到(1+Aaux)Cgs,因此需降低运算放大器的相位裕度.

在具有深反馈的高速设计中,第二极点频率ω2p通常远高于第一极点频率ω1p,使得增益带宽乘积最优化变得复杂.为了跟踪其过程变化并增加辅助放大器的主极点频率,在辅助放大器的输出端添加额外电容器CC对ωaux微调[11],其中,ωaux为辅助放大器的主极点频率.需要注意的是,最终结果应对CC的价值不敏感,CC只是验证过程的重要部分.

2.4 偏置电路

为了实现大输出摆幅,本文采用高摆幅共源共栅偏置电路.同时,由于通过偏置网络的电流比通过主放大器的电流小10倍,因而偏置电路产生的功耗较小.

2.5 共模反馈电路

目前,大多数共模反馈电路主要由差分电路或基于开关电容的电路构成.然而,以开关电容电路为基础的共模反馈电路CMFB对于连续时间系统或高频应用而言并非是最优选的,基于对称和非对称DDA的CMFB不适用于具有大输出信号摆幅的系统(尤其是在低电源电压下)[12].相反,虽然平衡电阻/电容DDA[13]不适合高输出阻抗系统或在深亚微米技术制造的电路中,但其可工作在大输出摆幅电压下.本文提出了一种共模反馈电路,其包括晶体管T23~T35.在该共模反馈电路中,平衡电阻/电容差分放大器共模反馈结构中的电阻/电容网络由晶体管T23~T28组成的晶体管网络代替,其可以感测输出共模电平而不改变系统输出端的阻抗.由于信号从运算放大器的输出端outp和outn传递到晶体管T32的栅极时中间只经过源跟随器,因此,晶体管T32的栅压VG(T32)随着输出共模电压的增加而增加.由于晶体管T23~T28为互补型CMOS晶体管,因此能够保证在全摆动范围内检测输出共模电平,而不将晶体管T31~T35之中的任何一个晶体管拉离饱和区.此外,由于在晶体管T23~T28所组成的晶体管网络中,其所有节点的等效阻抗均比较低,因而不对电路的稳定性造成影响.与其他共模反馈电路相比较而言,该共模反馈电路的线性输入范围更大,输出共模电压误差最小,同时输出摆幅最大,且不改变运算放大器的输出阻抗.

3 仿真结果

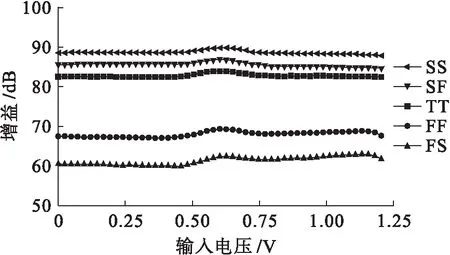

工艺参数、电源电压和工作温度的变化对深亚微米集成电路的使用与性能有着较大的影响,本文用PVT(precess voltage temperature)仿真方法来对文中的放大器电路进行仿真.PVT仿真是将电路在不同工艺、电压、温度组合下对电路进行仿真的方法,其已经成为在模拟电路和射频电路等设计中不可缺少的电路仿真方法.本文在1.05、1.20和1.35 V电源电压下对所有5个工艺角SS(slow-slow),SF(slow-fast),TT(typical-typical),FF(fast-fast)以及FS(fast-slow)和3种不同温度0、27以及75 ℃进行了模拟研究.表1为仿真结果,其显示了在宽温度范围和不同电源电压下OTA在不同工艺角下的性能.

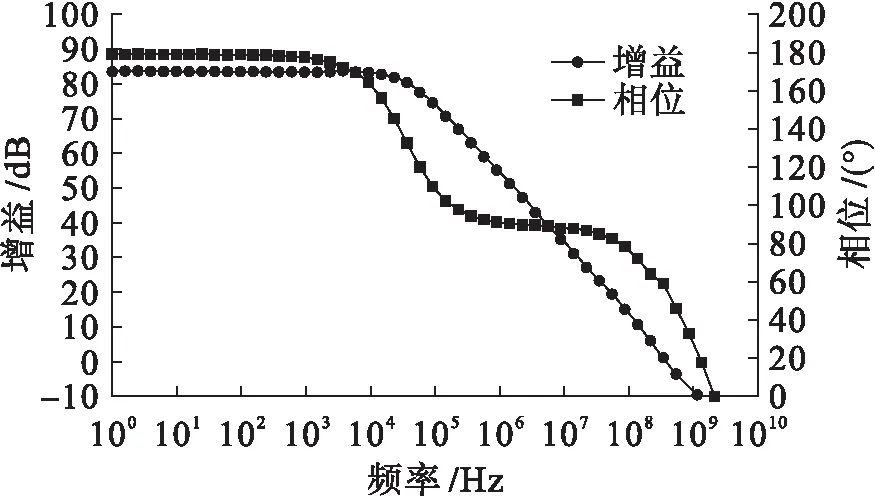

图4为在不同工艺角下,放大器增益随输入电压的变化曲线.由图4可以看出,对于所有的工艺角,运算放大器的增益均为常数.在典型情况下,通过轨到轨输入电压实现82 dB的直流增益.此外,电路的AC分析仿真结果显示了放大器的增益带宽为477 MHz,且当负载为1 pF时其相位裕度约为60°,放大器的总功耗约为4.8 mW,如图5所示.

表1 模拟结果数据Tab.1 Simulation result data

图4 不同工艺角下增益随输入电压的变化曲线Fig.4 Change curves for gain with input voltageunder different process angles

图5 增益与相位随频率的变化曲线Fig.5 Change curves for gain andphase with frequency

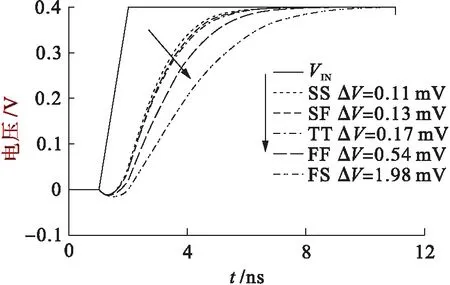

在闭环配置中模拟运算放大器的稳定行为,图6为运算放大器的阶跃响应图,其显示了运算放大器的稳定性能,其中,ΔV表示对应工艺角下瞬态响应电压与输入阶跃信号电压的差值.瞬态仿真结果显示,当输入电压为0.4 V,放大器稳定时间为10 ns时,在正常角下放大器稳定精度为0.05%,而最坏角和最好角下稳定精度分别为0.5%和0.03%.

图6 运算放大器阶跃响应Fig.6 Step response of operational amplifier

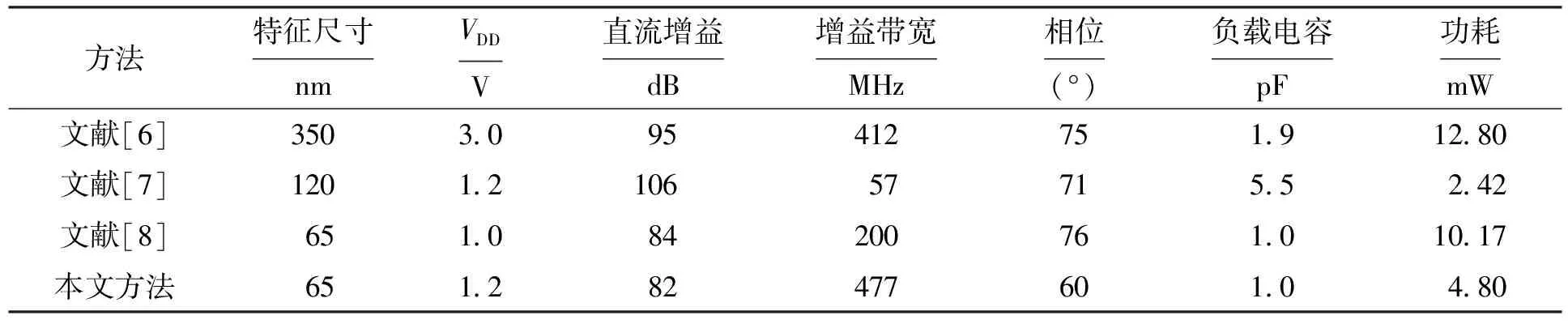

表2列举了不同文献中提出的运算放大器与本文提出的运算放大器的性能参数值.由表2中数据可知,本文提出的全差分结构放大器与其他文献提出的运算放大器相比,具有较高的增益带宽及较低的功耗,其在低功率下的高增益带宽使其成为了高频应用的适当选择.

4 结 论

本文提出了一种采用了65 nm CMOS工艺技术的具有轨到轨输入级的运算放大器,其在1.2 V的电源电压下具有477 MHz的带宽.同时,对于正常角在1 pF的负载下,直流增益为82 dB,相位裕度为60°,高增益和高增益带宽使其成为无线通信和其他高频应用的正确选择,这项工作将用于可编程模拟正弦波发生器设计中.

表2 不同文献中放大器性能比较Tab.2 Comparison in performance of amplifiers in different references

[1] Liu Y T,Xing D Y,Wang Y,et al.A low power dissipation high-speed CMOS image sensor with column-parallel sigma-delta ADCs [J].Microelectronics Journal,2015,46(9):860-868.

[2] Kumngern M,Khateb F,Kulej T.Fully-balanced four-terminal floating nullor for ultra-low voltage analogue filter design [J].Iet Circuits Devices & Systems,2017,11(2):173-182.

[3] Abolhasani A,Tohidi M,Hadidi K.A new high-speed,high-resolution open-loop CMOS sample and hold [J].Analog Integrated Circuits and Signal Processing,2014,78(2):409-419.

[4] Liu Y C,Chang H Y,Huang S Y.Design and analysis of CMOS high-speed high dynamic-range track-and-hold amplifiers [J].IEEE Transactions on Microwave Theory & Techniques,2015,63(9):2841-2853.

[5] Yun C.On the operation of CMOS active-cascode gain stage [J].Journal of Computer & Communications,2013(6):18-24.

[6] Musa R,Yusoff Y,Tan K Y,et al.Design of single-stage folded cascode gain boost amplifier for 100 mW 10-bit 50 ms/s pipelined analog-to-digital converter [C]//IEEE International Conference on Semiconductor Electronics.Kuala Lumpur,Malaysia,2006:800-804.

[7] Schlögl F,Zimmermann H.OPAMP with 106 dB DC gain in 120 nm digital CMOS [C]//Proceedings of the 29th European Conference on Solid-State Circuits.Estoril,Portugal,2003:381-384.

[8] Sancarlo I D,Giotta D,Baschirotto A,et al.A 65-nm 84-dB-gain 200-MHz-UGB CMOS fully-differential three-stage amplifier with anovel common mode control [C]//Proceedings of the 34th European Confe-rence on Solid-State Circuits.Edinburgh,UK,2008:314-317.

[9] Perenzoni M,Parmesan L,Stoppa D.A robust,power and area-efficient gm-control for low-noise operational amplifiers [J].Analog Integrated Circuits and Signal Processing,2015,82(1):209-216.

[10]Rezaei F,Azhari S J.Rail-to-rail input/output operational transconductance amplifier (OTA) with high CMRR and PSRR [J].Electrical Engineering,2012,94(3):165-175.

[11]Guo S,Xi T,Gui P,et al.A transformer feedback-boosting technique for gain improvement and noise reduction in mm-wave cascode LNAs [J].IEEE Tran-sactions on Microwave Theory & Techniques,2016,64(7):2080-2090.

[12]Mak P I,Liu M,Zhao Y.Enhancing the performances of recycling folded cascode OpAmp in nanoscale CMOS through voltage supply doubling and design for reliability [J].International Journal of Circuit Theory & Applications,2014,42(6):605-619.

[13]Guo B,Chen J,Jin H.A linearized common-gate low-noise amplifier using active cross-coupled feedback technique [J].Analog Integrated Circuits & Signal Processing,2016,89(1):1-10.

DesignoflowpowerCMOSoperationalamplifierwithfullydifferentialstructure

XIAO Ying-hui

(Wuhan College, Zhongnan University of Economics and Law, Wuhan 430000, China)

In order to reduce the influence of low supply voltage and short channel effect on the amplifier and obtain an amplifier with low voltage and high gain, a fully differential operational transconductance amplifier (OTA) based on a 65 nm CMOS technology was proposed. A folded-cascode structure with a gain enhancement technology was adopted, which made the amplifier have a rail to rail input and large output swing characteristics and such advantages as high speed, high gain and low power. The circuit simulation results show that the DC gain is 82 dB, the gain bandwidth is 477 MHz and the phase margin is 59°. In addition, the settling time is 10 ns and the settling accuracy is 0.05% under the normal process angle, while the power consumption is only 4.8 mW.

CMOS integrated circuit; gain enhancement; operational transconductance amplifier; high speed; high gain; low power; folded-cascode structure; high gain bandwidth

2017-04-01.

中国博士后科学基金资助项目(2015T80797).

肖莹慧(1982-),女,湖北武汉人,讲师,硕士,主要从事集成电路与功率集成技术,人工智能与软件工程等方面的研究.

* 本文已于2017-10-25 21∶13在中国知网优先数字出版. 网络出版地址: http:∥www.cnki.net/kcms/detail/21.1189.T.20171025.2113.060.html

10.7688/j.issn.1000-1646.2017.06.13

TN 432

A

1000-1646(2017)06-0670-05

(责任编辑:钟 媛 英文审校:尹淑英)